FPGAを使用した組み込み設計:実装言語

編集者注:スマートな製品設計のための高度なアルゴリズムが出現し続けるにつれて、開発者は、これらのアルゴリズムに関連する処理要求を満たすことができる組み込みシステムの実装に苦労することがよくあります。 FPGAは必要なパフォーマンスを提供できますが、FPGAを使用したデザインは、FPGAプログラミングの専門家の権限に限定されると長い間考えられてきました。しかし、今日では、より強力なFPGAとより効果的な開発環境が利用できるようになり、FPGA開発に幅広くアクセスできるようになりました。この抜粋、 『Architecting High-Performance Embedded Systems』の第4章では、FPGAデバイス、実装言語、FPGA開発プロセスの包括的なレビューと、FPGAの実装を開始する方法の詳細なウォークスルーを提供しています。設計。完全な抜粋は、次の一連の記事で紹介されています。

編集者注:スマートな製品設計のための高度なアルゴリズムが出現し続けるにつれて、開発者は、これらのアルゴリズムに関連する処理要求を満たすことができる組み込みシステムの実装に苦労することがよくあります。 FPGAは必要なパフォーマンスを提供できますが、FPGAを使用したデザインは、FPGAプログラミングの専門家の権限に限定されると長い間考えられてきました。しかし、今日では、より強力なFPGAとより効果的な開発環境が利用できるようになり、FPGA開発に幅広くアクセスできるようになりました。この抜粋、 『Architecting High-Performance Embedded Systems』の第4章では、FPGAデバイス、実装言語、FPGA開発プロセスの包括的なレビューと、FPGAの実装を開始する方法の詳細なウォークスルーを提供しています。設計。完全な抜粋は、次の一連の記事で紹介されています。

1:ハードウェアリソース

2:実装言語(この記事)

3:開発プロセス

4:プロジェクトの構築

5:実装

ジム・レディンによる「高性能組み込みシステムの設計」から採用。

FPGA実装言語

FPGAのデザインを実装することは、最終的には1つ以上のソフトウェアプログラミングのような言語を使用してデバイスの機能を定義することになります。

FPGA開発に使用される従来の言語は、VHDLとVerilogです。

現世代のFPGA開発ツールは、通常、これらの言語の両方をサポートし、ブロック図手法を使用してシステム構成を定義する機能も備えています。一部のツールスイートは、従来のCおよびC ++プログラミング言語を使用したFPGA機能の定義もサポートしています。

VHDL

VHSICハードウェア記述言語 ( VHDL )、ここでVHSICは Very の略です 高速集積回路 、Adaプログラミング言語を彷彿とさせる構文があります。 VHDLは、1983年から米国国防総省の指導の下で開発されました。

Adaと同様に、VHDLは非常に冗長で厳密に構造化されている傾向があります。プログラミング言語の用語では、VHDLは強く型付けされています。この言語には、主にブール値、ビット、ビットベクトル、文字、文字列、整数、実数、時間、および配列の事前定義された基本データ型のセットが含まれています。他のすべてのデータ型は、基本型の観点から定義されています。

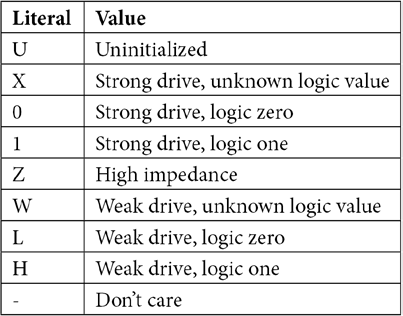

VHDLライブラリのセットは、米国電気電子学会によって定義されています。 ( IEEE )およびIEEE 1164標準として形式化された、 Multivalue Logic System for VHDLモデルの相互運用性 。これらのライブラリは、VHDL言語で使用される論理値のセットを定義します。このライブラリには、1ビット信号を表すstd_logicという名前の型が含まれています。 std_logicタイプ内の論理値は、次の表に示す文字リテラルで表されます。

前の図の「強い」0と1の値は、指定されたバイナリ状態に駆動される信号を表します。 「弱い」信号は、複数のドライバーを備えたバスで駆動される信号を表し、任意のドライバーがバス上で自分自身をアサートして、他のドライバーをオーバーライドできます。 Z値は、ハイインピーダンス状態のCMOS出力を表します。この場合、バスを0または1状態に駆動するのではなく、出力はバスから効果的に切断され、バスをまったく駆動しません。 U状態は、すべての信号のデフォルト値を表します。回路シミュレーションを実行すると、U状態の信号が検出されます。これは、初期化されていない値が意図せずに使用されていることを示している可能性があります。 X状態は、それらを駆動する出力がないワイヤに関連付けられています。 –状態は未使用の入力を表すため、どの状態にあるかは関係ありません。

VHDL回路設計は通常、次のステートメントを介してIEEE1164ライブラリをインポートすることから始まります。

ライブラリIEEE;

IEEE.std_logic_1164.allを使用します;

この章の後半のプロジェクト例では、VHDLを使用します。これは、VerilogよりもVHDLを強く優先することを意図したものではありません。どちらのハードウェア定義言語も、FPGA用に合成できる基本的にすべてのデザインを完全に表現できます。

Verilog

Verilog ハードウェア記述言語 ( HDL )は1984年に導入され、2005年にIEEE 1364として標準化されました。2009年に、Verilog標準は SystemVerilog と統合されました。 IEEE標準1800-2009を作成するための標準。 SystemVerilogには、Verilogに存在するハードウェア設計機能に加えて、システム検証を実行するための広範な機能が含まれています。

Verilogは、Cプログラミング言語に似せて設計されており、同様の演算子の優先順位や、if、else、for、whileなどの同じ制御フローキーワードの使用が含まれています。

Verilogはワイヤーの概念を使用しています 信号の状態を表します。信号値は、0、1、ドントケア(x)、または高インピーダンス(z)のいずれかの値を取ることができ、強いを持つことができます。 または弱い 信号強度。

VHDLとVerilogはどちらも、ロジック回路の設計に使用できる言語サブセットを定義しています。これらのサブセットは、合成可能と呼ばれます。 言語サブセット。回路シミュレーションなどのタスクをサポートするために、合成可能なサブセット以外の追加の言語機能を利用できます。この例については、この章の後半で説明します。

合成不可能な言語構造は、従来のソフトウェアプログラミング言語のように動作する傾向があります。たとえば、合成不可能なforループは、通常のプログラミング言語の場合と同様に、コードのブロックを指定された回数だけ順番に繰り返します。一方、合成可能なforループは効果的に展開され、ループの各反復を表す並列で実行される複製されたハードウェア構造のコレクションを生成します。

ブロック図

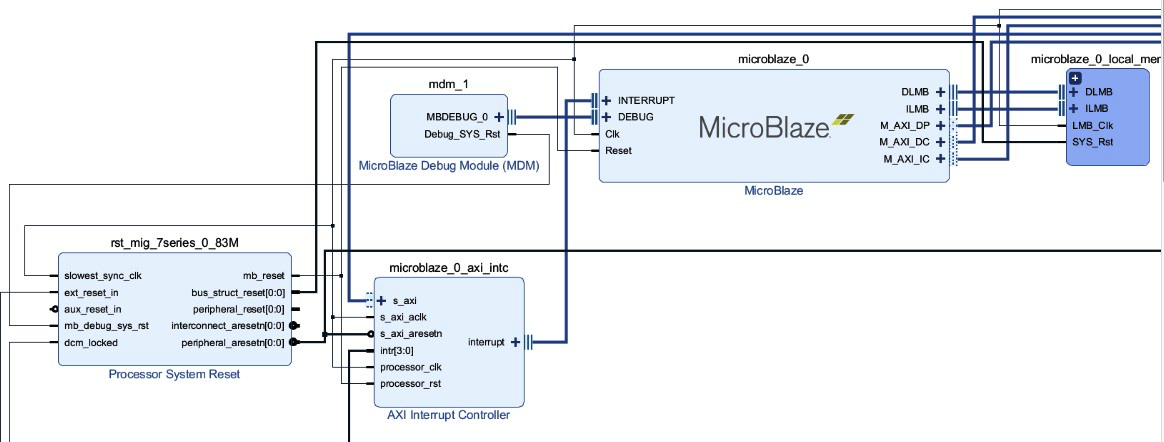

最新のFPGA開発ツールスイートは、テキストベースのHDLを超える抽象化レベルで、マイクロプロセッサやブロック構造フォーマットを使用した高度なI / Oデバイスなどの複雑なロジックコンポーネントを組み込んだシステム設計の迅速な構成をサポートします。 図4.2 MicroBlazeソフトプロセッサを組み込んだザイリンクスFPGAデザインのブロック図の一部の例です。

クリックしてフルサイズの画像を表示

図4.2–MicroBlazeソフトマイクロプロセッサを含むブロック図

MicroBlazeプロセッサ は、Artix-7を含むプロセッサファミリのFPGAデザインで使用するためのザイリンクスVivadoツールスイートで提供されるプロセッサコアです。

ブロックダイアグラムを使用すると、FPGAデザインの複雑なロジックエレメントのインスタンス化と相互接続を視覚的に直感的に整理できますが、ダイアグラムの背後で、開発ツールがVHDLまたはVerilogコードを生成してコンポーネントとそのコンポーネントを定義することを覚えておくことが重要です。接続。ブロック図は、これらのコンポーネントの構成を管理するための単なるユーザーインターフェイスです。

ブロック図を作成した後、プロジェクトに関連付けられたファイルに含まれる、生成されたHDLコードを調べることができます。 図4.2 の図 、design_1_microblaze_0_0_stub.vhdlという名前のファイルがダイアグラムから生成されます。このファイルは、次のVHDLコードで始まります。

ライブラリIEEE;

IEEE.STD_LOGIC_1164.ALLを使用します;

エンティティdesign_1_microblaze_0_0は

ポート(

Clk:STD_LOGIC内;

リセット:STD_LOGIC内;

割り込み:STD_LOGIC内;

Interrupt_Address:STD_LOGIC_VECTOR(0〜31);

Interrupt_Ack:out STD_LOGIC_VECTOR(0 to 1);

Instr_Addr:out STD_LOGIC_VECTOR(0〜31);

命令:STD_LOGIC_VECTOR(0から31);

このコードは、IEEE 1164標準ライブラリへの参照から始まり、システムクロック、リセット、割り込み要求、割り込みベクトル入力など、マイクロプロセッサで期待される信号を公開するMicroBlazeプロセッサへのインターフェイスを定義します。割り込み確認応答と命令アドレス出力。およびメモリから取得した命令用のバス。

このコードは、シングルビット信号(STD_LOGIC)およびマルチビットバス信号(STD_LOGIC_VECTOR)のIEEE1164ライブラリデータ型を利用します。

リストのコードはMicroBlazeプロセッサーへのインターフェースを定義していますが、プロセッサー自体のHDL定義は含まれていません。マイクロプロセッサなどのコンポーネントの複雑なHDL設計は、価値があると見なされます知的財産 ( IP )およびこれらの設計を開発する営利団体は、適切なライセンスなしに使用されないようにするための措置を講じることがよくあります。ベンダーが顧客が使用するためにIPを配布する場合、エンドユーザーには不透明なコンパイル済み形式で提供される場合があります。これにより、ユーザーはIPを設計に組み込むことができますが、開発に使用されたHDLを調べることはできません。これは、コンパイルされた形式でライブラリをリリースするが、ソースコードを提供しないソフトウェア開発者と概念的に似ています。

C / C ++

多くのベンダーが、FPGA開発で使用するために従来の高水準プログラミング言語(多くの場合CおよびC ++)をHDLコードに変換するソフトウェアツールを提供しています。このアプローチは、FPGA実装で高速化するCまたはC ++の複雑なアルゴリズムがある場合に魅力的です。これらのツールを使用すると、C / C ++に精通しているソフトウェア開発者は、HDLの1つを学ぶ必要なしに、FPGAで使用するコードの実装をすぐに開始できます。

これらの高級言語用のFPGA開発ツールは、C / C ++コードアルゴリズムの結果として得られるFPGA実装を大幅に最適化することができますが、C / C ++実行モデルにはステートメントの順次実行が含まれるという点で、依然として何らかの断絶があります。ネイティブFPGA環境は、並列ハードウェアコンポーネントで構成されています。 C / C ++コードから得られたFPGAデザインは、通常、プログラミング言語ステートメントで定義された操作の順次実行を管理するステートマシンのコレクションに似ています。 C / C ++コード内での並列実行の機会の可用性によっては、FPGA実装により、従来のプロセッサで同じコードを実行する場合と比較して、パフォーマンスが大幅に向上する場合があります。

最新のFPGA開発ツールスイートでは、このセクションで説明するFPGA実装のすべてのメソッド(VHDL、Verilog、ブロックダイアグラム、およびC / C ++)を、必要に応じて1つのデザインに組み合わせることができます。このため、あるチームメンバーはVHDLでの作業を好み、別のチームメンバーはVerilogを使用する場合があります。単一のプロジェクト内でのマルチHDLの使用を思いとどまらせるプロジェクト管理上の理由があるかもしれませんが、言語自体は問題なく単一の設計で一緒に機能します。プロジェクトマネージャーが複数のHDLの使用を避けたいと思う理由のひとつは、今後の取り組みの継続には、両方の言語のスキルを持つ開発者の参加が必要になるためです。

同様に、ブロック図の観点からプロジェクトの高レベルのアーキテクチャを定義し、選択したHDLを使用して詳細なサブシステム機能を実装することができます。同じ設計で、C / C ++アルゴリズムから生成されたHDLを統合することも可能です。組み込みシステムのアーキテクトと開発者は、その影響を慎重に検討し、FPGAデザインの各部分に適切な実装方法を選択する必要があります。

次のセクションでは、標準のFPGA開発プロセスの手順を紹介します。

PacktPublishingの許可を得て転載。 Copyright©2021Packt Publishing

>

ジム・レディン Ledin Engineering、Inc。のCEOです。Jimは、組み込みソフトウェアおよびハードウェアの設計、開発、およびテストの専門家です。彼はまた、組み込みシステムのサイバーセキュリティ評価と侵入テストでも活躍しています。彼は理学士号を持っていますアイオワ州立大学で航空宇宙工学の学位を取得し、M.S。ジョージア工科大学で電気およびコンピューター工学の学位を取得。ジムは、カリフォルニアで登録された専門の電気技師、Certified Information System Security Professional(CISSP)、Certified Ethical Hacker(CEH)、およびCertified Penetration Tester(CPT)です。

ジム・レディン Ledin Engineering、Inc。のCEOです。Jimは、組み込みソフトウェアおよびハードウェアの設計、開発、およびテストの専門家です。彼はまた、組み込みシステムのサイバーセキュリティ評価と侵入テストでも活躍しています。彼は理学士号を持っていますアイオワ州立大学で航空宇宙工学の学位を取得し、M.S。ジョージア工科大学で電気およびコンピューター工学の学位を取得。ジムは、カリフォルニアで登録された専門の電気技師、Certified Information System Security Professional(CISSP)、Certified Ethical Hacker(CEH)、およびCertified Penetration Tester(CPT)です。 >

関連コンテンツ:

- FPGAを使用した組み込み設計:ハードウェアリソース

- オープンソースツールはFPGAプログラミングを簡素化するのに役立ちます

- FPGAまたはASICでの浮動小数点アルゴリズムの実装

- ソフトウェアツールは、AIアプリケーション用にGPUコードをFPGAに移行します

- FPGAはスバルEyesightビジョンベースADASのASICに取って代わります

- フラッシュベースのFPGAが機能安全要件をどのように簡素化するか

- インスタントオンFPGAのメリットを享受する

- 高速NORフラッシュを使用したFPGA構成

- 新しいミッドレンジシステム要件を満たすためにFPGAテクノロジがどのように進化しているか

Embeddedの詳細については、Embeddedの週刊メールニュースレターを購読してください。

埋め込み