ArmコアデバイスでのJTAG実装

この記事では、ArmデバッグインターフェイスまたはADIに特に注意を払いながら、JTAGとArmコアデバイスの共通部分について説明します。

これまでのJTAGに関するシリーズでは、テストアクセスポート(TAP)コントローラーとTAPステートマシンを含むIEEE1149.1標準について説明してきました。次に、コネクタの一般的なピン配置、市場で入手可能なJTAGインターフェースとデバッグプローブなど、JTAGでの作業に使用できるさまざまな物理インターフェースを確認しました。

この記事では、JTAG標準から少し逸脱し、代わりにJTAGがユビキタスARMコアデバイスにどのように実装されているかを見ていきます。

アームとは何ですか?

Armは、マイクロプロセッサおよびマイクロコントローラインターフェイスに関連する大量の知的財産とともに、プロセッサアーキテクチャを指します。民生用PCがx86派生プロセッサ、PowerPC、またはMIPSを使用する傾向がある場合、組み込み電子機器はほとんどの場合、Armコアプロセッサで実装されます。

プロセッサの「コア」はSTMicroelectronicsやNXPなどのメーカーに配布され、これらのメーカーはI2CおよびSPIインターフェイス、ADCおよびDAC、USBインターフェイスなどの追加の周辺機能を追加します。

ArmアーキテクチャはARMvとしてバージョン管理されており、例としてARMv2(1987年から)、ARMv6(2002〜2005年に製造されたプロセッサ)などがあり、これらのアーキテクチャを利用するプロセッサコアはARMxシリーズ(ARM1、ARM6、ARM7)としてブランド化されています。最近では、高性能(Cortex-A)、リアルタイム(Cortex-R)、およびマイクロコントローラー(Cortex-M)アプリケーション向けのARM Cortex-A / R / Mシリーズとして使用されています。アーキテクチャのバージョン管理は、Cortexサフィックスの命名に従い、ARMv6-M、ARMv7-R、ARMv7-Aなどのバージョンになります。

Armのデバッグインターフェイスは、Arm CoreSightArchitectureの名前に分類されます。これには、デバッグインターフェイス(Arm Debug Interface、ADI)、組み込みトレースマクロセル(ETM)、高速シリアルトレースポート(HSSTP)、およびCoreSightプログラムフロートレースアーキテクチャが含まれます。 ADIは、Armコアプロセッサを使用したデバッグ操作のベースを形成します。この標準の一部には、JTAGインターフェイスとSerial Wire Debug(SWD)の代替手段が含まれています。この記事のトピックはADIであり、特にハードウェアインターフェイス層です。

Arm Debug Interface(ADI)の概要

Arm Debug Interface(ADI)は、ホストと1つ以上のデバイス間のデバッグ用のハードウェアインターフェイスと論理インターフェイスの両方の仕様です。現在、ほとんどのプロセッサはADIv5(Arm IHI0031Eで指定)を実装していますが、新しいADIv6(Arm IHI0074Cを参照)は徐々に段階的に導入されています。人気が高いため、ここではADIv5標準に焦点を当てます。

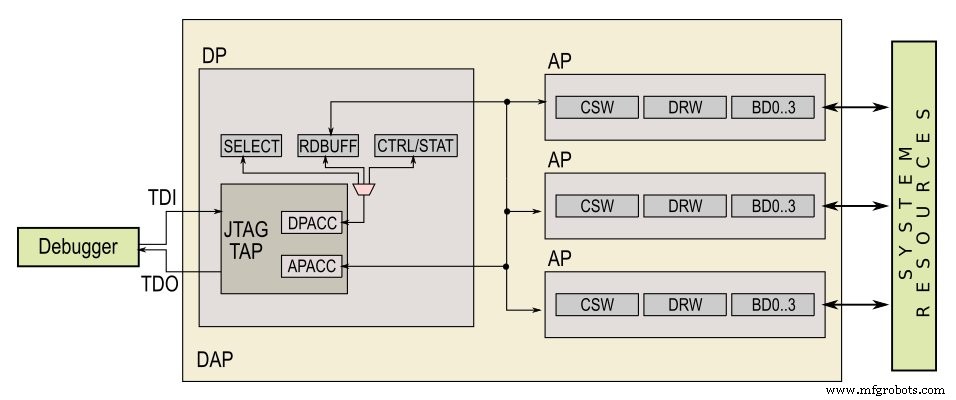

ADIは、デバッグポート(DP)とアクセスポート(AP)で構成されるデバッグアクセスポート(DAP)を定義します。 DAPは、デバッグインターフェイスの主要な「ユニット」です。特定のデバイスには、デバッガーとの物理接続を処理する1つのデバッグポートと、デバッグレジスタ、トレースポートレジスタ、ROMテーブル、システムメモリなどのシステムリソースへのアクセスを提供する多数のアクセスポートがあります。したがって、DPには物理接続(JTAG、SWD)といくつかの組み込みレジスタが含まれ、各APにはシステムへの接続と、いくつかの独自のレジスタがあります。

ADIv5には、2種類のデバッグポートと、(大まかに言えば)3種類のアクセスポートがあります。 DPは、デバイスの外部からDAPに接続する際に使用されるインターフェイスにちなんで名付けられたJTAG-DPまたはSWD-DPのいずれかです。 APはMEM-APにすることができ、アドレス指定(メモリマッピングに類似しているため、名前)、JTAG-AP、JTAGスキャンチェーンをデバッグユニット全体(DAP)に接続できるようにすること、およびベンダー固有のリソースへのアクセスを提供します。 Armによって指定されていないAP。 MEM-APは最も一般的で便利なため、ここでは他のタイプについては説明しません。

JTAGのコンテキストでは、デバッグインターフェイスがJTAG命令コードとベンダー固有のJTAG機能を提供することが期待されます。実際、ADIv5標準では、次の手順が提供されています。

- EXTEST(0b00000000)

- サンプル(0b00000001)

- プリロード(0b00000010)

- テスト(0b00000100)

- クランプ(0b00000101)

- HIGHZ(0b00000110)

- ABORT(0b11111000)

- DPACC(0b11111010)

- APACC(0b11111011)

- IDCODE(0b11111110)

- バイパス(0b11111111)

また、JTAGデータレジスタには次のものが含まれます。

- ABORT(35ビット)、アクセスポートを強制的に中止するように登録します

- DPACC(35ビット)、デバッグポート読み取り/書き込みアクセスレジスタ

- APACC(35ビット)、アクセスポート読み取り/書き込みアクセスレジスタ

- IDCODE(32ビット)

- バイパス(1ビット)

ここで目立つのは、DPACCとAPACCの命令、および関連するデータレジスタです。 DPACC(デバッグポートアクセス)およびAPACC(アクセスポートアクセス)は、デバイスの関連するDPおよびAPにコマンドを渡すために使用される命令/レジスタです。 DPACCまたはAPACCデータレジスタに異なる値を設定することにより、デバッガは異なる操作を実行でき、通常はDPおよびAP自体のレジスタと相互作用します。これらのDPACCおよびAPACCレジスタ(JTAGレジスタ)と、DPおよびAPに組み込まれているレジスタの違いに注意してください。

ここでの一般的な方法は、デバッガーがJTAGまたはSWDインターフェイスを使用してTAPステートマシンを経由して命令を実行し、命令がデータを取得してDPまたはAPにロードし、データに応じて、 DPまたはAPにアクセスして、システムへの目的のリンクを提供します。

では、DPおよびAPレジスタとは何ですか?使用可能なDPレジスタは次のとおりです。

- CTRL / STAT、DPに関するステータス情報を制御および取得するために使用されます

- データリンク制御レジスタであるDLCRは、データリンクの動作モードを制御します

- DLPIDR、データリンクプロトコル識別レジスタ、プロトコルバージョン情報

- DPIDR、デバッグポート識別レジスタ、デバッグポート情報

- EVENTSTAT、イベントステータスレジスタ。システムが外部デバッガにイベントを通知するために使用します

- RDBUFF、読み取りバッファレジスタは、読み取り操作を提供します。 DP(JTAGまたはSWD)に依存

- SELECT、AP Selectレジスタ、アクセスポートとそのAPを備えたアクティブなレジスタバンクを選択します。 DPアドレスバンクを選択します

- TARGETIDは、ホストが単一のデバイスに接続されている場合のターゲットに関する情報を提供します

MEM-APレジスタは次のとおりです。

- 制御/ステータスワードレジスタ(CSW、0x00)、制御およびステータス情報を保持します

- 転送アドレスレジスタ(TAR、0x04)は、メモリシステムまたはシステムリソースへの次のアクセス用のアドレスを保持します

- データ読み取り/書き込みレジスタ(DRW、0x0C)は、TARのアドレスの読み取りまたは書き込みを設定します– DRWを読み取る場合、アクセスは読み取りに設定されます。 DRWに書き込む場合、アクセスは書き込みに設定されます

- バンクデータレジスタ(BD0〜BD3、0x10、0x14、0x18、0x1C)は、TARのアドレスから始まる4つの32ビットメモリブロックへの直接読み取りまたは書き込みアクセスを提供します。

- 構成レジスタ(CFG、0xF4)、MEM-AP構成に関する情報

- ベースアドレスレジスタ(BASE、0xF8)のデベース、メモリシステムへのポインタ、一連のデバッグレジスタの開始またはROMテーブルの開始

- 識別レジスタ(IDR、0xFC)は、MEM-APを識別します。

以下の図1に、接続を概略的に示します。

図1。 接続を要約したArmDebugInterface図。注:DPとAPのすべてのレジスタが表示されるわけではありません。

DP / APレジスタとメモリマッピングの詳細は、仕様IHI0031Eに記載されています。詳細に立ち入るのではなく、他のタイプのデバッグポートであるSWD-DPと、2本のワイヤのみを使用してJTAGを実装する方法に焦点を当てたいと思います。

シリアルワイヤデバッグ(SWD)

JTAG-DPは、デバッグインターフェイスの一般的でよく知られた例ですが、ここでの説明に最も関連するのは、Armデバイス用に定義されたJTAGの代替手段であるArm Serial Wire Debug(SWD)です。 SWDは、ピン数が制限されたArmコアデバイス用の2線式インターフェイスとして開発されました。マイクロコントローラは周辺機器が非常に密集している傾向があるため、ほとんどのCortex-Mデバイスは、ピンの領域を節約するために、完全なJTAGの代わりにSWDを実装します。では、このプロトコルはどのように機能しますか?

SWDは、ADIv5仕様(B4章)で指定されています。 JTAGのTDIピンとTDOピンは、SWDIOと呼ばれる単一の双方向ピンに置き換えられています。テストモード選択(TMS)ピンが完全に削除されています。クロック(TCK)は同じままです(CLKまたはSWCLKのラベルが付け直されています)。したがって、SWDは、JTAGで使用される4つのピンと比較して、2つのピンのみを使用します。これを機能させるために、SWDはJTAG操作の反復性に依存しています。つまり、ステートマシンが操作され、データがシフトインまたはシフトアウトされ、プロセスが繰り返されます。 SWDとの違いは、ステートマシンがないことです。代わりに、コマンドはSWDIOを介してシリアルに発行され、同じピンがデータの読み取りまたは書き込みに使用されます。

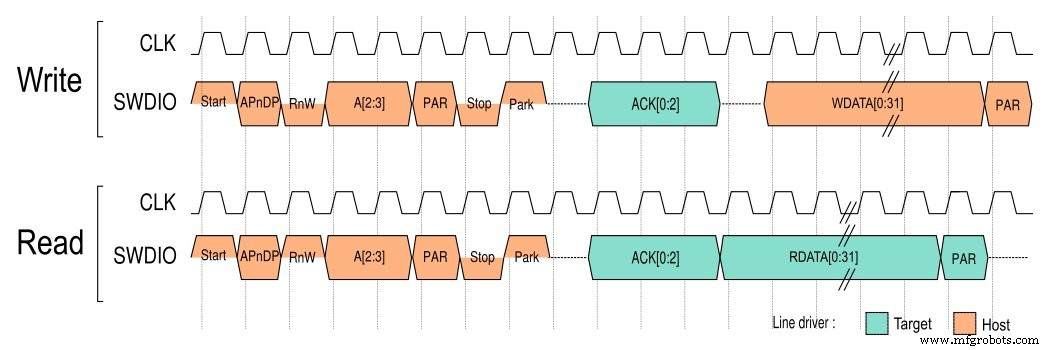

SWD通信には、パケット要求、確認応答、およびデータ転送の3つのフェーズがあります。パケット要求中に、ホストプラットフォームはDPに要求を発行し、その後に確認応答が続く必要があります。パケット要求がデータ読み取りまたはデータ書き込み要求であり、有効な確認応答があった場合、システムはデータ転送フェーズに入り、SWDIOを介してデータがクロックイン(書き込み)またはクロックアウト(読み取り)されます。データ転送後、ホストはパケット要求を開始するか、アイドルサイクル(SWDIO LOWのクロッキング)でSWDインターフェイスを駆動する責任があります。パリティチェックは、パケット要求とデータ転送フェーズに適用されます。

SWDの詳細は、図2に示すタイミング図を見ると最もよく理解できます。

図2。 シリアルワイヤデバッグの読み取りおよび書き込み操作を示すタイミング図。 [クリックして拡大]

読み取り操作と書き込み操作はどちらも同じように開始され、ホストがSWDIOラインをHIGH信号であるスタートビットに駆動するところから始まります。これに続いて、APまたはDPアクセスビット(APnDP)、読み取りまたは書き込みビット(RnW)、アドレス(A [2:3])、パリティビット(PAR)、およびストップビット( LOW信号)、最後にパークビットが続きます。これは、回線がターンアラウンドに入る前に、ホストが回線をHIGHに駆動するときです。ターンアラウンド中、ターゲットもホストもラインを駆動することはできません。

RnWの値に応じて、読み取りまたは書き込み操作が選択されます。書き込みの場合、ターゲットは3ビットのACK信号を提供し、次に別のターンアラウンド期間があり、その後に書き込まれる32ビットのデータ(WDATA)とパリティビットが続きます。読み取りの場合、ターゲットはACKを提供し、32ビット読み取りデータ(RDATA)、続いてパリティビットでラインを駆動し続けます。エラーが発生した場合、ACKビットは障害を示し、ホストは操作の再開を試みることができます。 WDATA [31:0]の代わりにWDATA [0:31]を書き込むことにより、図2に示すように、WDATAとRDATAが最初に最下位ビット(LSb)で送信されることを確認します。

Arm IHI0031Eドキュメントには、通信のさまざまなケースを明確にするためのタイミング図がさらに記載されていますが、上記が主な使用例です。 SWDには(執筆時点で)2つのバージョンがあることに注意してください。 SWDv1は、ホストとターゲット間の1つの接続(ポイントツーポイント)のみをサポートしますが、SWDv2は、単一ホストの複数ターゲット通信(マルチドロップ)を実装します。バージョン2は、いくつかのエッジケースを除いて、バージョン1とほぼ下位互換性があります。

JTAGの他のバリエーション

SWDは、JTAG IEEE1149.1標準の2線式バリアントだけではありません。特に、IEEE 1149.7標準は、ピン数を減らした(2線式)JTAGインターフェイスを提供します。 IEEE 1149.4(ミックスドシグナルテストバスの標準)やIEEE 1149.6(高度なデジタルネットワークのバウンダリスキャン標準)などの他の1149.x標準は、過去20年間に開発され、より複雑なアプリケーションに追加機能を提供します。これには、アナログバウンダリスキャンテストや、差動およびAC結合ラインの改善された機能などが含まれます。

最新の規格は、IEEE StandardsAssociationのWebサイトから入手できます。

結論

これで、JTAGとSWDの説明は終わりです。このシリーズを通じて、JTAGがどこから来たのか、どのように機能するのか、デバイスのデバッグとプログラミングにどのように使用されるのかを学びました。商用とオープンソースの両方で利用可能なコネクタとインターフェイスを含む、JTAGの物理的な接続を確認しました。最後に、SWD 2線式インターフェースを含む、一般的なArmプロセッサコアテクノロジのJTAG実装の概要を説明しました。

ここから、外に出て、組み込みデバイスのデバッグおよびプログラミング機能を自信を持って使用し、さまざまな実装の詳細を学習し、時間を最大限に活用することができます。

埋め込み