Integrated Logic Analyzer (ILA) および Virtual Input/Output (VIO) の使用

このチュートリアルでは、Integrated Logic Analyzer (ILA) の使用について説明します および 仮想入出力 (VIO) ザイリンクス Vivado IDE で VHDL デザインをデバッグおよび監視するためのコア。

多くの場合、設計者はオンチップ検証を実行する必要があります。つまり、検証目的で FPGA デザインの内部信号の動作にアクセスできます。

1 つのオプションは、これらの信号を FPGA ピンに送り、それらを LED に接続して、その動作を視覚的に確認することです。このオプションは簡単で高速で、単純なケースではうまく機能しますが、柔軟性、拡張性、または現実的ではありません。

もう 1 つのオプションは、これらの信号の動作を表示および描写できる高度な機能を備えた外部ロジック アナライザーを使用することですが、それには外部の比較的高価な機器が必要です。

Integrated Logic Analyzer (ILA) は、以前の両方のオプションの利点を組み合わせた代替手段です。簡単、高速、柔軟で、設計者が選択した信号の動作をすばやく表示して確認するのに役立つ多くの高度な機能を備えています。

概要

この記事には、Vivado GUI の複数のスクリーンショットが含まれています。 画像をクリックすると大きくなります!

サイドバーを使用して概要をナビゲートします をクリックするか、モバイル デバイスを使用している場合は、下にスクロールして右上隅にあるポップアップ ナビゲーション ボタンをクリックします。

ILA と VIO

ILA および VIO は、ザイリンクスが提供する無料のカスタマイズ可能な IP です。 ILA IP を使用すると、FPGA 内の内部信号を簡単にプローブし、それらをシミュレーションのような環境に持ち込んで監視し、その動作を検証できます。

ILA とは異なり、VIO IP では FPGA 内の内部信号を仮想的に駆動して、RESET 信号を駆動するなど、デザインを刺激または制御できます。

- ザイリンクスの知的財産:統合ロジック アナライザー (ILA)

- ザイリンクスの知的財産:仮想入出力 (VIO)

要件

<オール>Kintex-7 FPGA KC705 評価キットを使用していますが、このチュートリアルで示す方法は、最新のザイリンクス FPGA ボードで動作するはずです。

サンプル プロジェクトをダウンロード

以下のフォームを使用して、サンプル プロジェクトと VHDL コードをダウンロードできます。 Vivado バージョン 2020.2 以降で動作するはずです。

Zip を解凍し、ila_tutorial.xpr を開きます Vivado でファイルを作成してサンプル デザインを表示するか、この記事の残りの部分を読んでゼロから作成する方法を学習してください。

Vivado でプロジェクトを作成

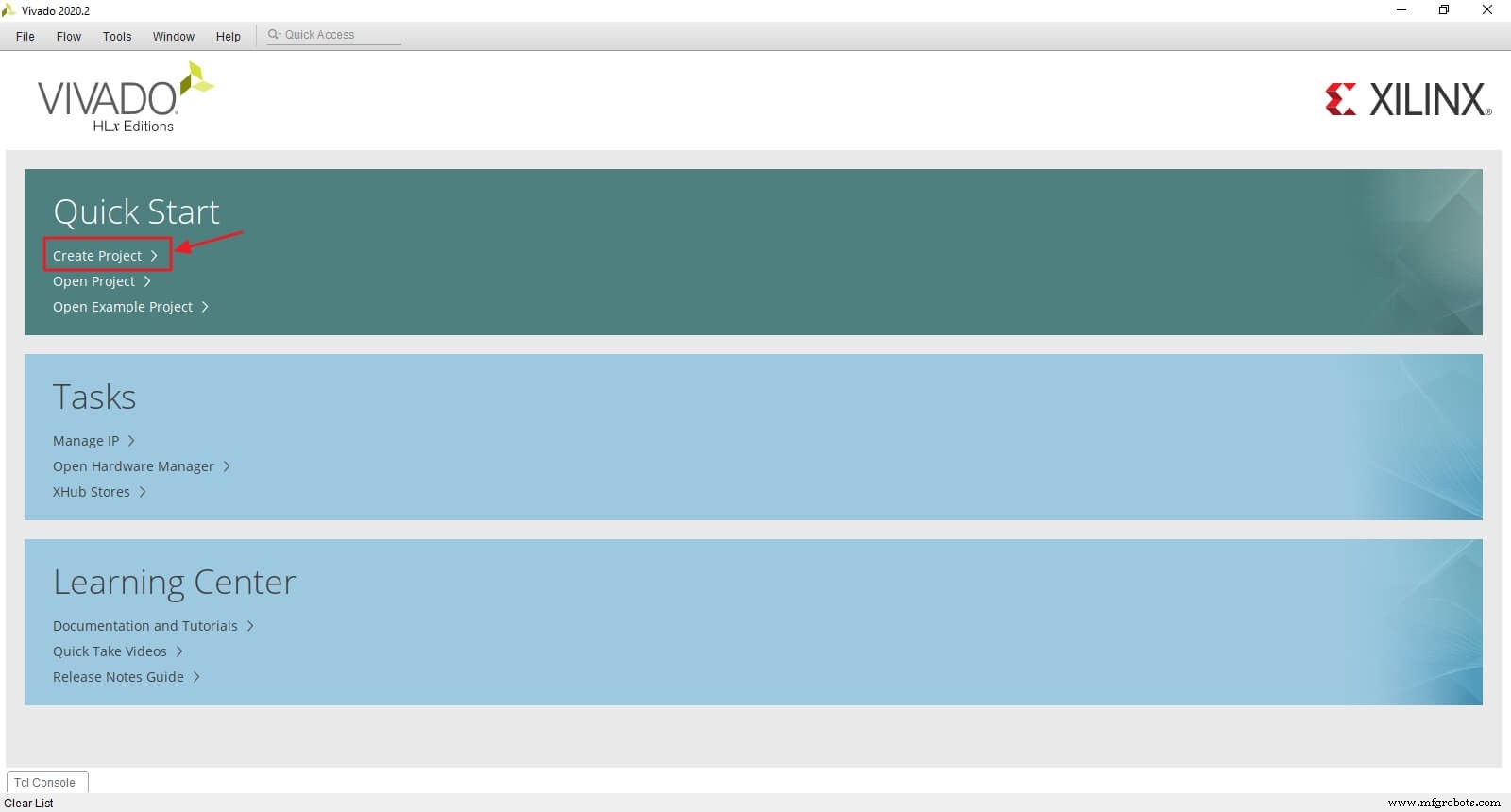

まず、Vivado を開きます。 Vivado のようこそ画面で、[Create Project] をクリックします。 ボタン。

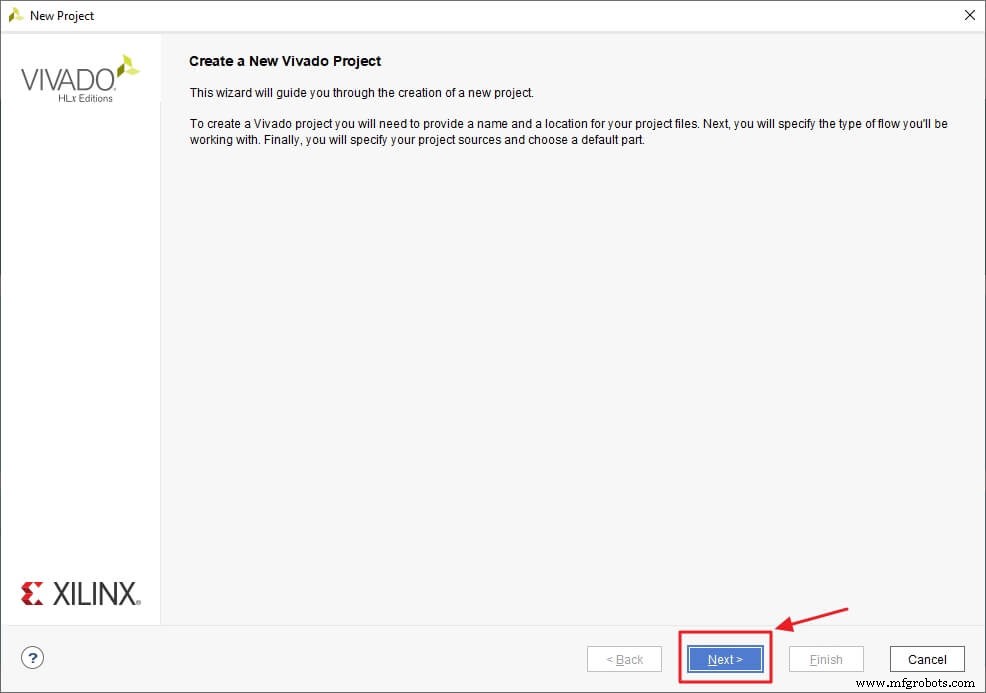

[次へ] をクリックします 続行します。

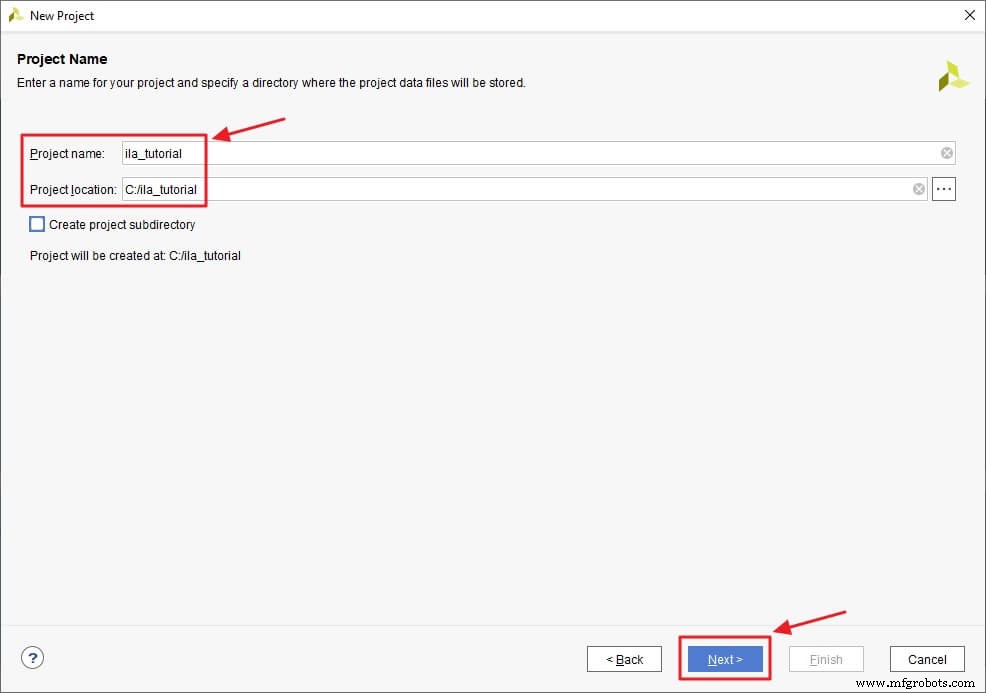

プロジェクトの名前を ila_tutorial に変更します [次へ] をクリックします。

注: プロジェクト名にスペースを使用しないでください。代わりに、アンダースコアまたはダッシュを使用してください。

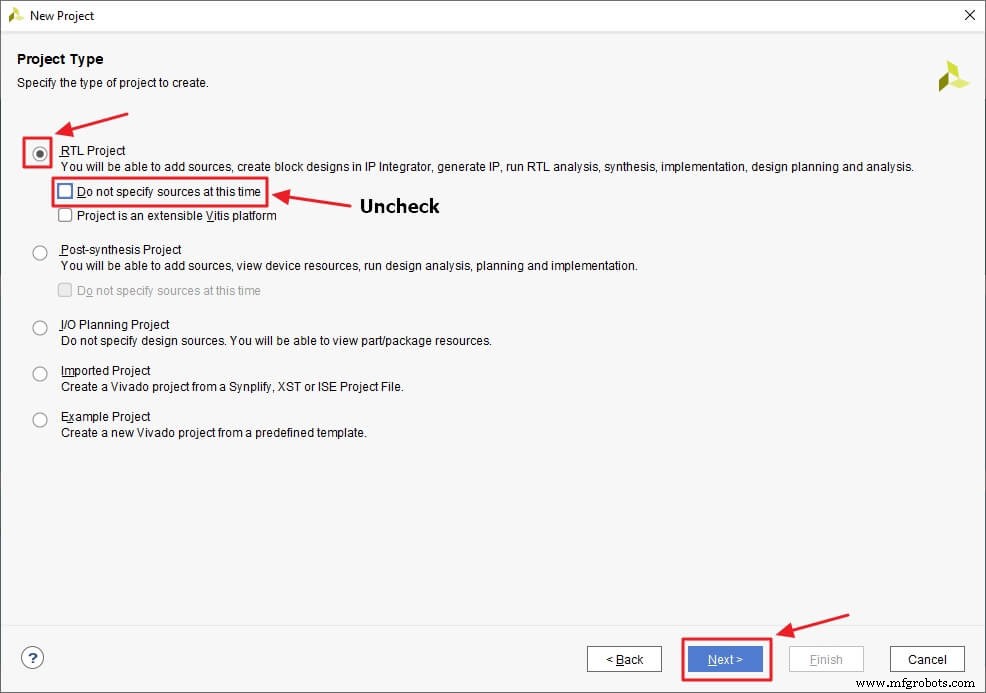

RTL プロジェクトを選択 [今回はソースを指定しない] のチェックを外します [次へ] をクリックします。 続行します。

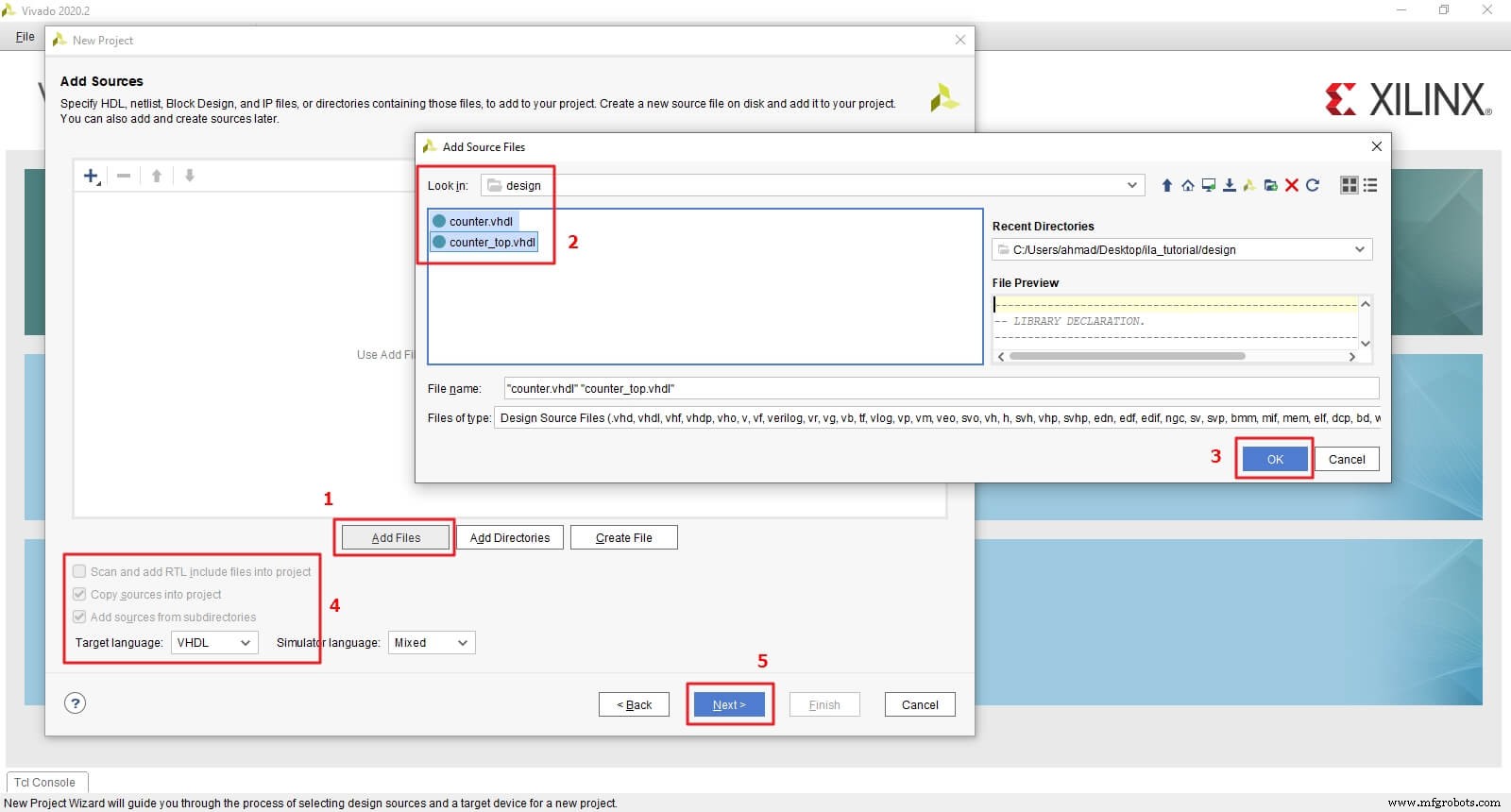

ソース ファイルを追加します。 counter.vhdl および counter_top.vhdl デザインフォルダからVHDL を選択 ターゲット言語用。 ソースをプロジェクトにコピー をチェックします [次へ] をクリックします。 続行します。

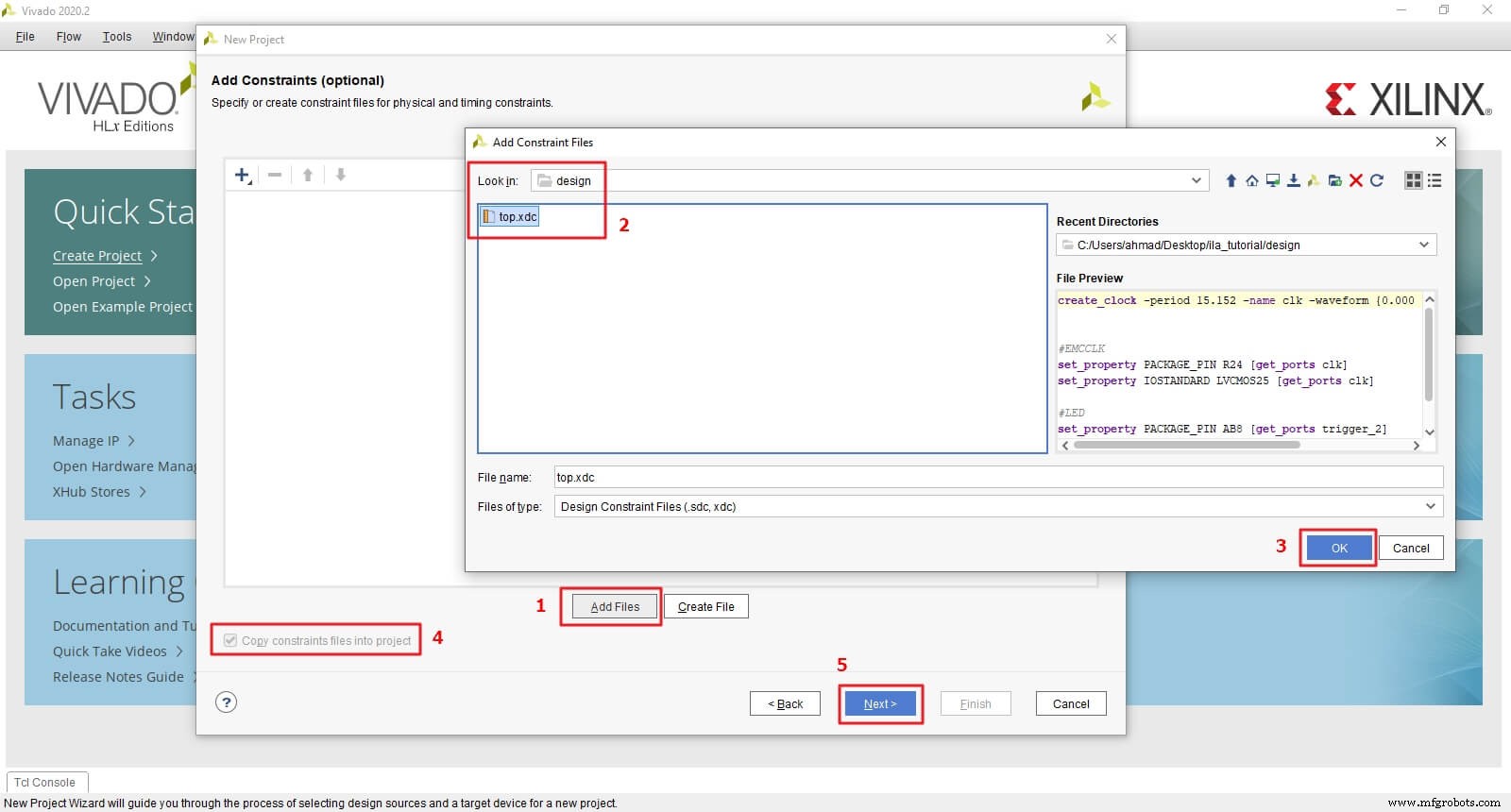

制約ファイル top.xdc を追加します。 デザインフォルダから制約ファイルをプロジェクトにコピー をチェックします [次へ] をクリックします。 続行します。

注: この制約ファイルは KC705 ボードに固有のものです。 clk ピンを変更する必要があります と LED ピン あなたのボードによると。また、ピリオド

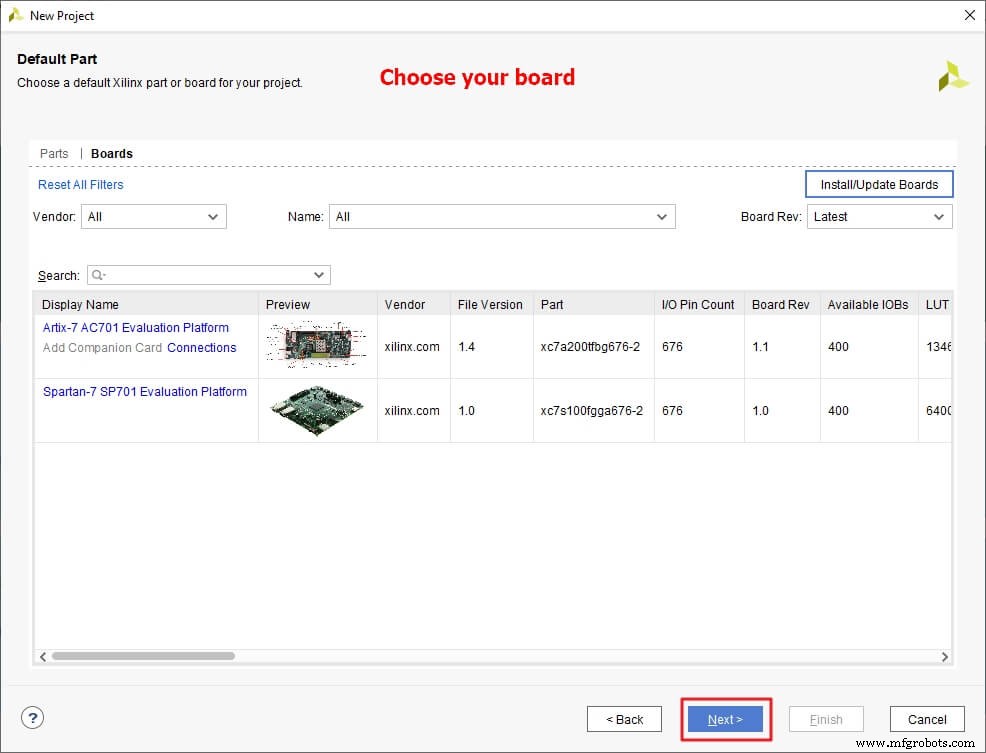

ボードを検索し、リストから選択します。 [次へ] をクリックします 続行します。

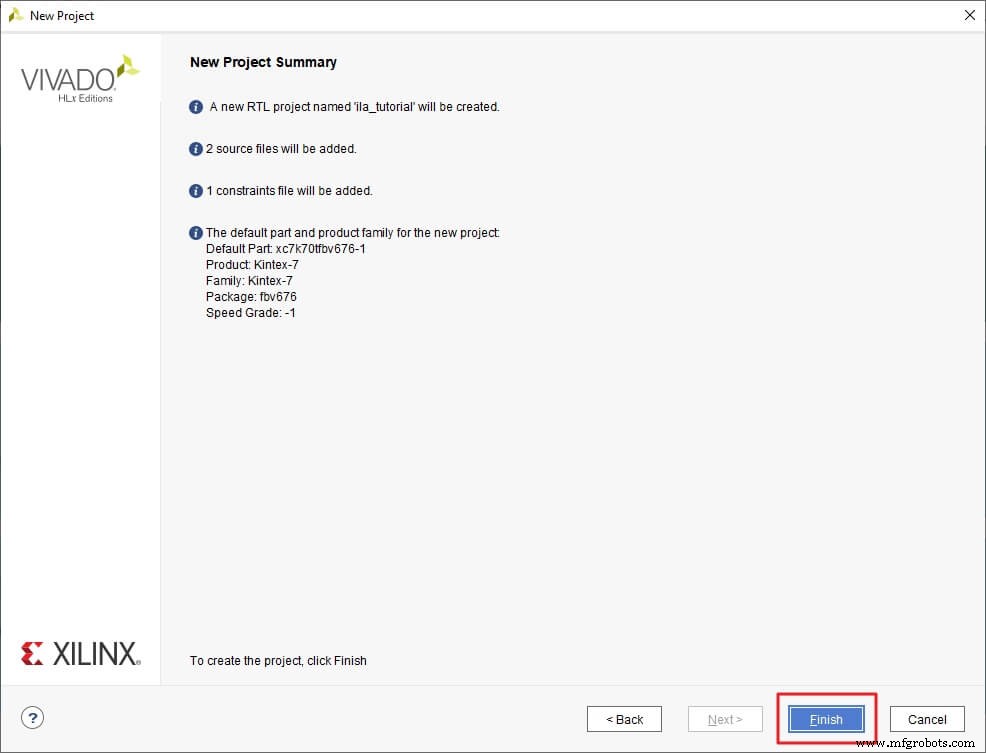

これは、新規プロジェクト ウィザードの最後の画面です。 [完了] をクリックします。 プロジェクトを開きます。

設計例の説明

このチュートリアルでは、単純な 2 つのカウンター チェーンの例を使用します。

counter.vhdl ファイルには、有効にすると 0 から 15 までカウントする簡単な 4 ビット カウンターの RTL コードが含まれています。カウントが 12 ~ 15 の場合、1 ビット出力をアサートします。その他すべての値の場合、出力は 低い「0」 のままです。 .

カウンター モジュールのエンティティ インターフェイスは次のとおりです。

----------------------------------------------------------------------------

-- ENTITY DECLARATION.

----------------------------------------------------------------------------

ENTITY counter IS

PORT(clk : IN STD_LOGIC; -- Main clock

reset : IN STD_LOGIC; -- reset, active_high

enable : IN STD_LOGIC; -- enable the next counter

trigger : OUT STD_LOGIC -- trigger the next counter

);

END ENTITY;

カウンターの設計には 2 つの内部信号があります:count とtrigger_o .

– 数 カウント機能を実装するために使用されます。

– および trigger_o 出力ポートトリガーを接続するための中間信号です .

ATTRIBUTE について心配する必要はありません 、後で説明します。

----------------------------------------------------------------------------

-- ARCHITECTURE DECLARATION.

----------------------------------------------------------------------------

ARCHITECTURE rtl OF counter IS

-- INTERNAL SIGNALS DECLARATION --

SIGNAL count : UNSIGNED(3 DOWNTO 0) := (OTHERS => '0');

SIGNAL trigger_o : STD_LOGIC := '0';

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

以下のリストでは、カウンターの実装を確認できます。 seq_proc プロセスは、入力ポート clk の立ち上がりエッジでトリガーされます 入力ポートが リセット するとリセット モードになります。 高い「1」です。

カウント 入力ポートが enable の場合、信号がインクリメントされます 高い「1」で、trigger_o 信号の値が count になると、信号は High にアサートされます は 12 から 15 の間です。

seq_proc: PROCESS (reset, clk)

BEGIN -- for seq_proc

IF (reset = '1') THEN

count <= (OTHERS => '0');

trigger_o <= '0';

ELSIF rising_edge(clk) THEN

IF (enable = '1') THEN

count <= count + 1;

IF (count > x"B" AND count <= x"F") THEN

trigger_o <= '1';

ELSE

trigger_o <= '0';

END IF;

END IF;

END IF;

END PROCESS;

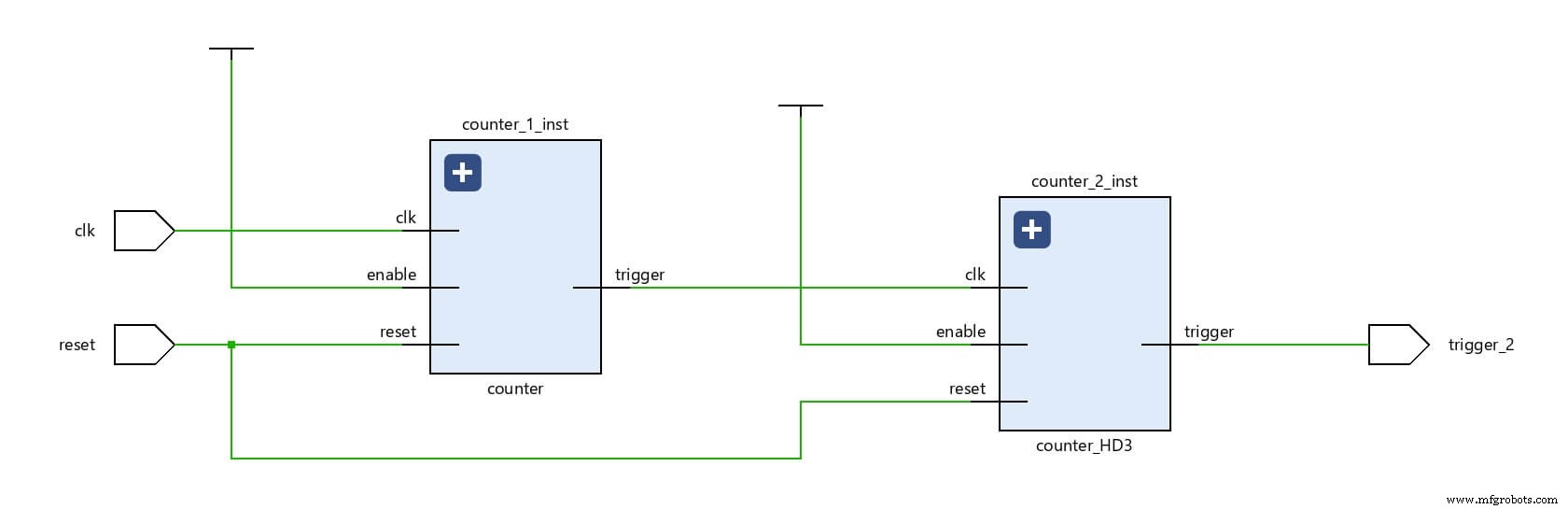

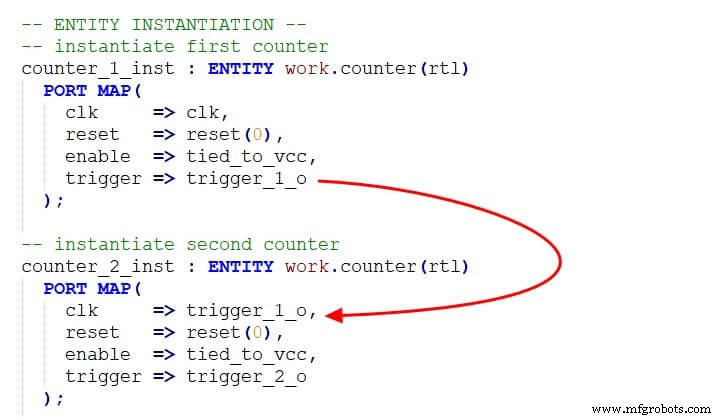

ファイル counter_top.vhdl 連続して接続されたカウンターの 2 つの瞬間を含みます。

– counter_1_inst 常に有効で、counter_2_inst をクロックします。 .つまり、出力ポートのトリガー counter_1_inst のうち 入力ポート clk に接続されています counter_2_inst の .

– 結果の動作は、counter_1_inst です。 counter_2_inst をアクティブにします 16クロックサイクルのうち4つだけです。したがって、 counter_2_inst は、16 カウントごとにカウンターを 4 回インクリメントします。

RESET 用の VIO コアの作成

設計例を理解したので、入力ポート reset を制御する VIO を作成します。 .これにより、Vivado IDE からリセットを操作 (トグル) できるようになり、カウンターを開始/停止するタイミングを手動で制御できるようになります。

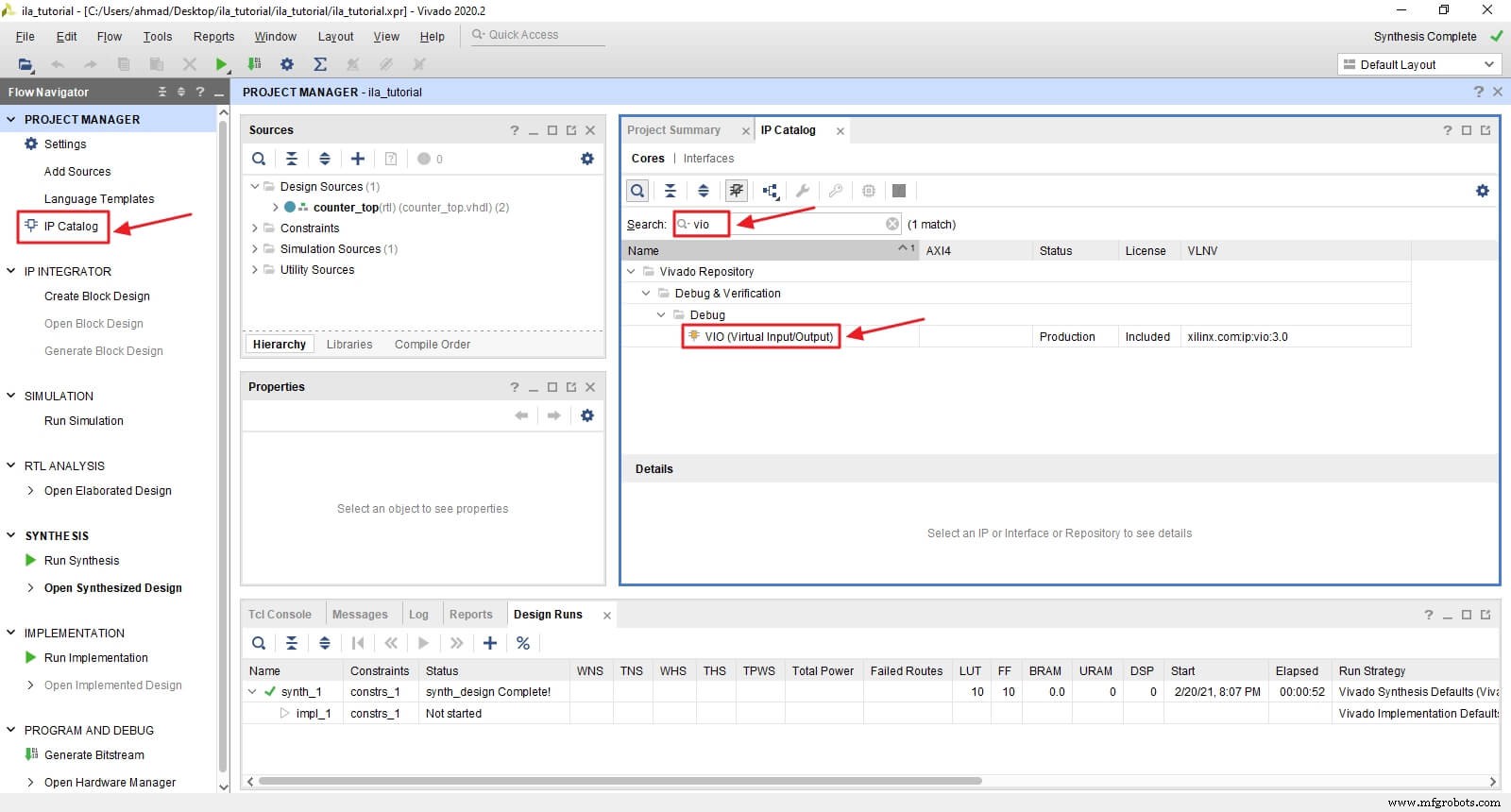

IP カタログをクリックします 、次に VIO を検索します 、VIO (Virtual Input/Output) をダブルクリックします。 .

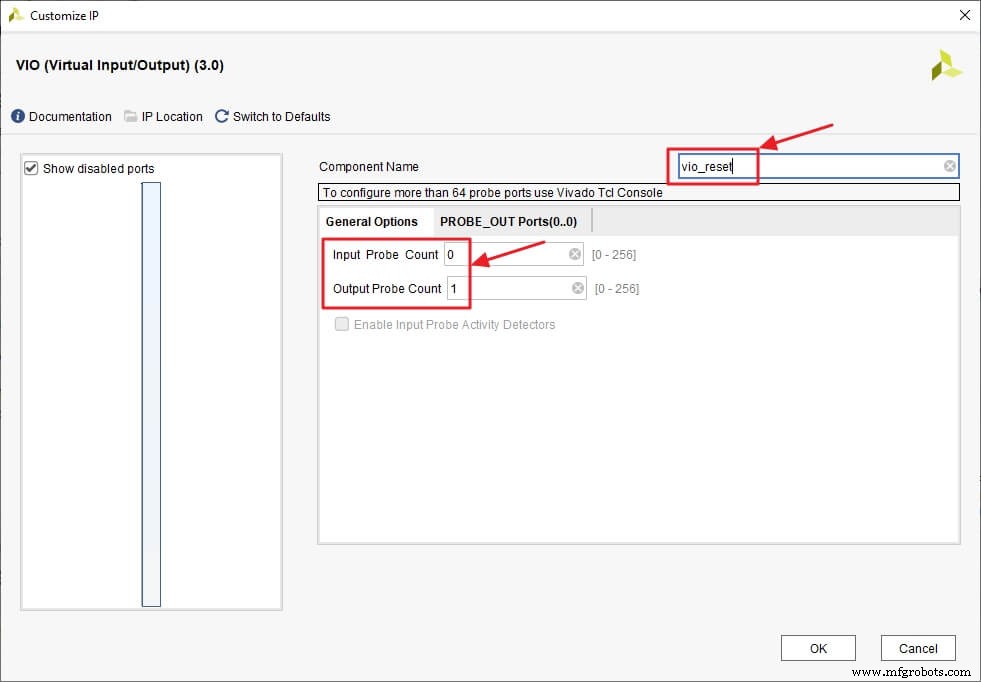

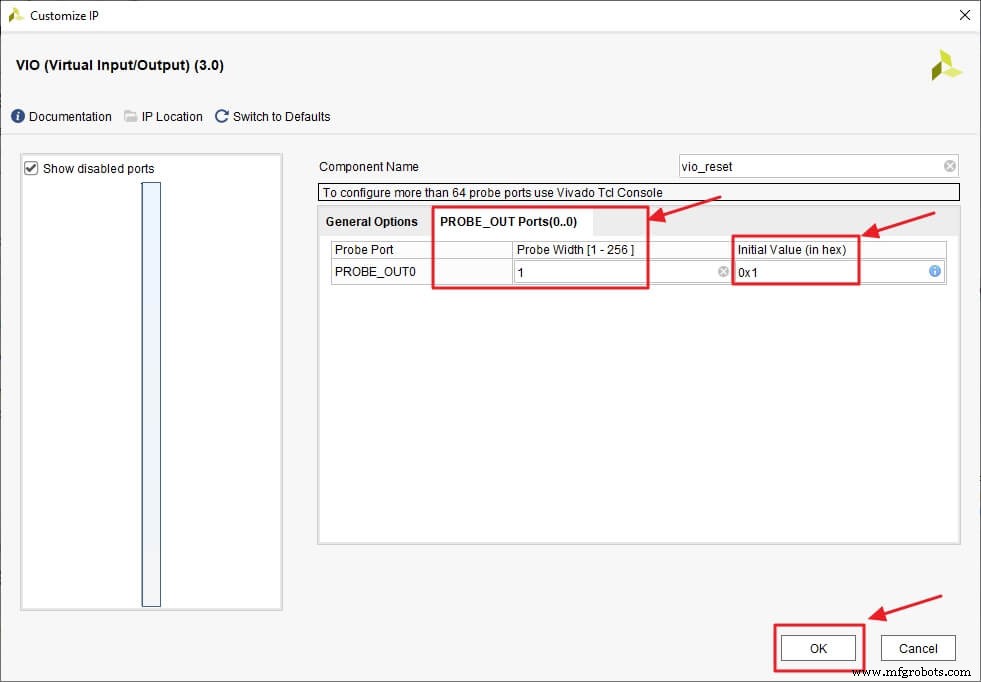

まず、名前を vio_reset に変更します .

次に、リセット用の出力ポートのみが必要なので、入力プローブ カウント ボックスに 0 を入力します。 出力プローブ カウント ボックスに 1 を入力 .

PROBE_OUT をクリックします ポートタブ。リセットは 1 ビット信号なので、probe_width ボックスに 1 を入れます。 また、初期値ボックスに 0x1 を入力します。 高い「1」から始まります。 [OK] をクリックします。 そして生成 . Vivado は VIO の合成を開始します。

Vivado が VIO の合成を終了したら、VIO のコンポーネントを宣言し、counter_top.vhdl でインスタンス化することにより、VIO をデザインに追加する必要があります。 以下のようにファイルしてください。

まず、vio_reset のコンポーネント宣言を追加します counter_top.vhdl のコンポーネント宣言セクション ファイル。

-- Declare vio_reset

COMPONENT vio_reset

PORT(

clk : IN STD_LOGIC;

probe_out0 : OUT STD_LOGIC_VECTOR(0 DOWNTO 0)

);

END COMPONENT;

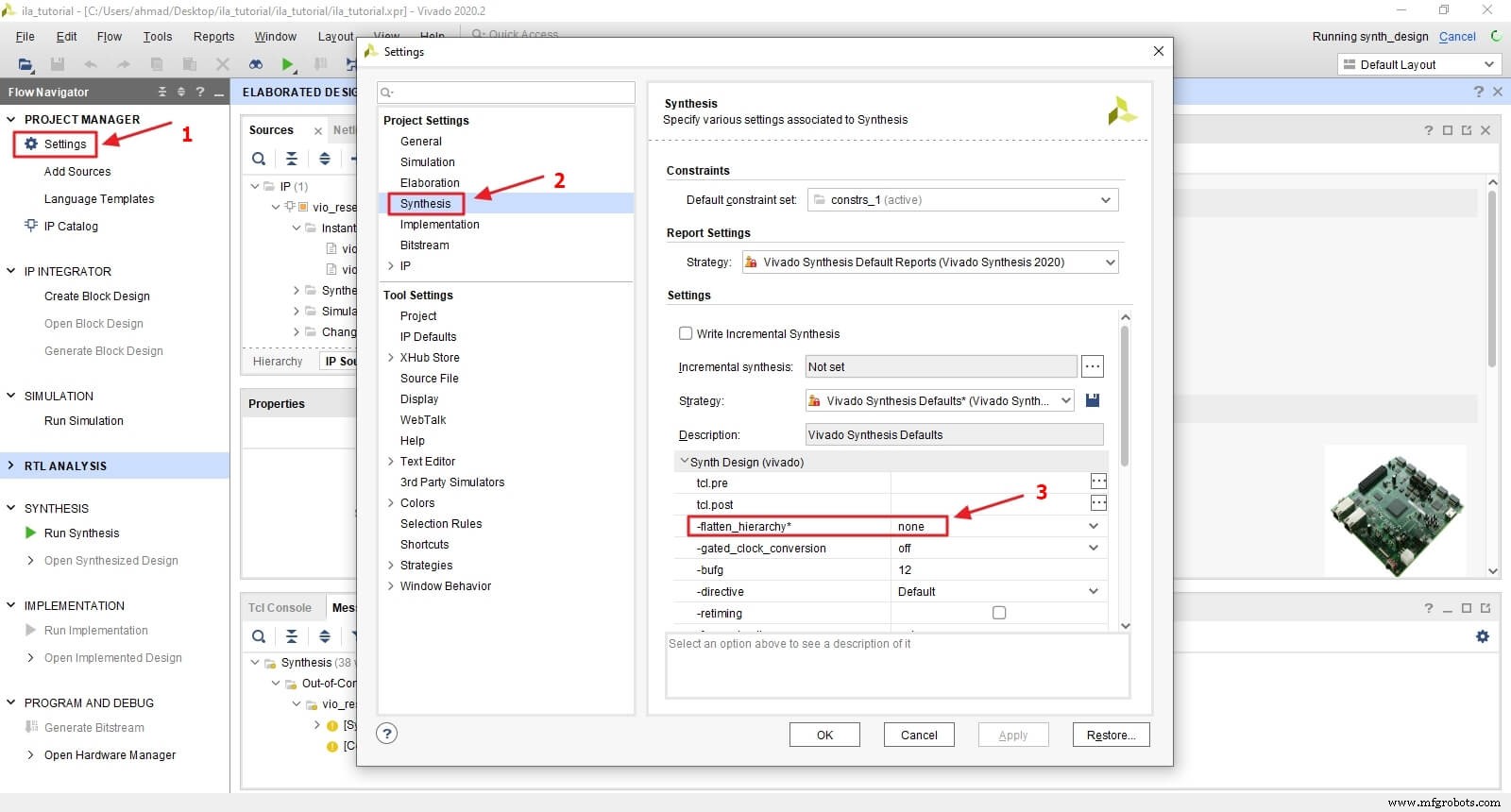

これで VIO が完成し、デザインを合成する準備が整いました。しかしその前に、統合設定 flatten_hierarchy を変更する必要があります なし .

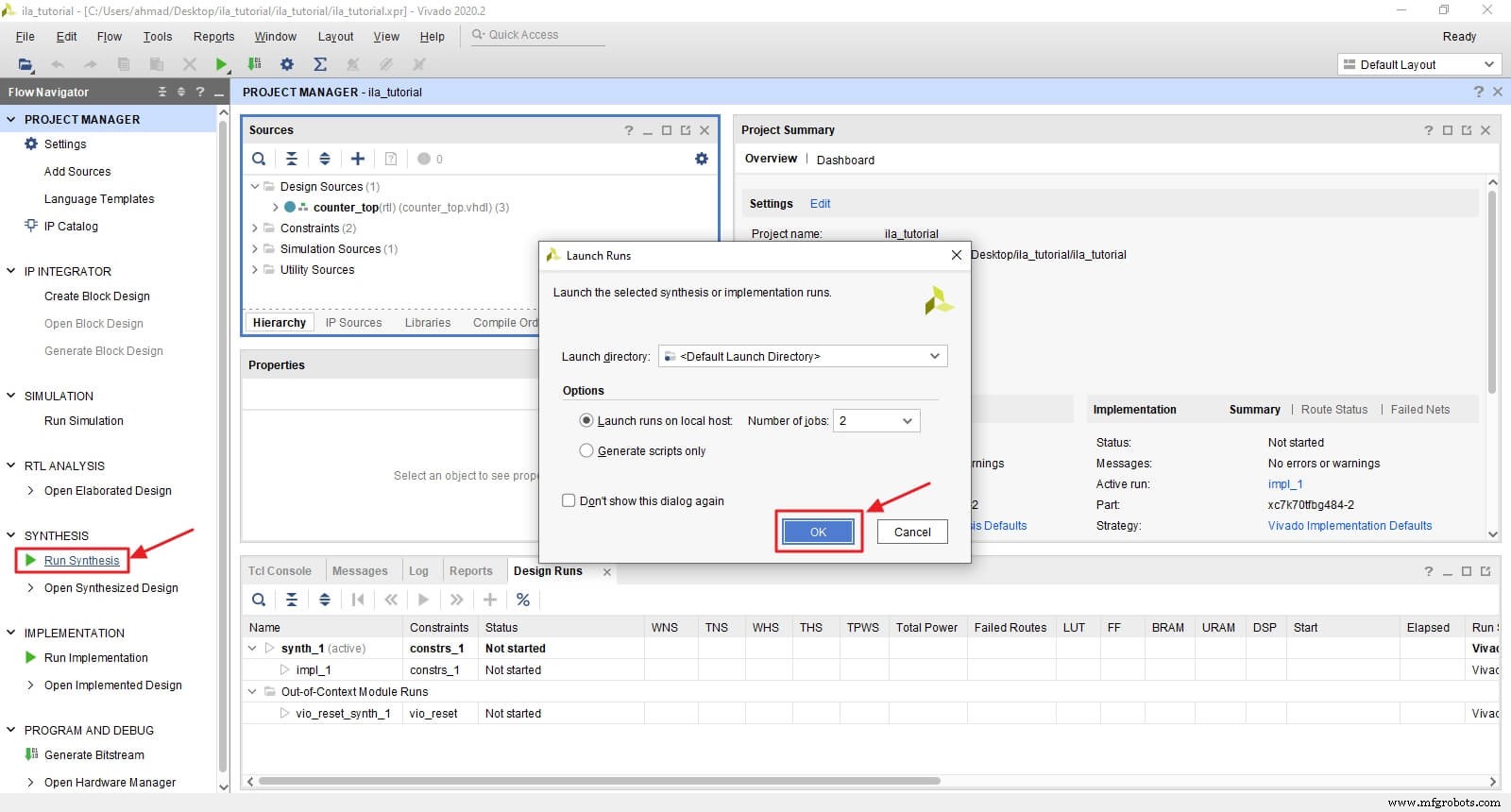

合成の実行 をクリックします。 そしてOK .

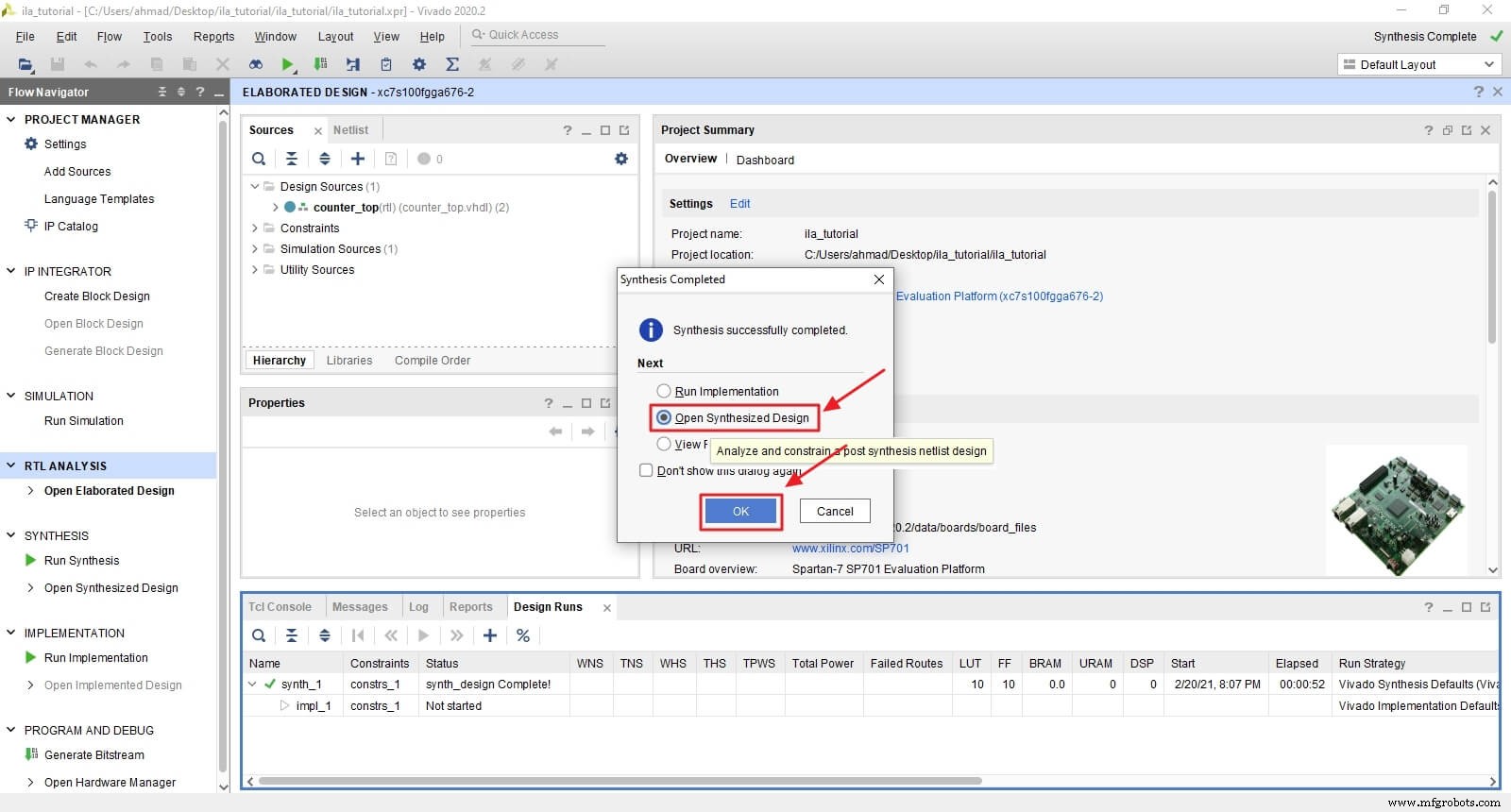

Vivado が合成を終了したら、[Open Synthesized Design] をクリックします。 .

レイアウトを debug に変更します レイアウト をクリックして そしてデバッグ .

デバッグ プローブ フローの挿入

合成されたデザインに vio_reset が含まれるようになりました 次に、プローブするシグナルを指定します。それには 3 つの方法があります:

<オール>最初の 2 つの方法を使用し、3 番目の方法は後のチュートリアルに残します。

VHDL ファイルからの挿入

この方法は、特に複合タイプ (配列またはレコード) の場合に、プローブを挿入する最も簡単で最速の方法です。ただし、実際の製品では冗長な VHDL コードである設計ファイルにコードを追加する必要があります。

次の方法で、VHDL デザイン ファイルにプローブを挿入できます。

<オール>

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

注: 各 VHDL デザイン ファイルで属性を 1 回宣言するだけでよく、複数の信号にアタッチできます。

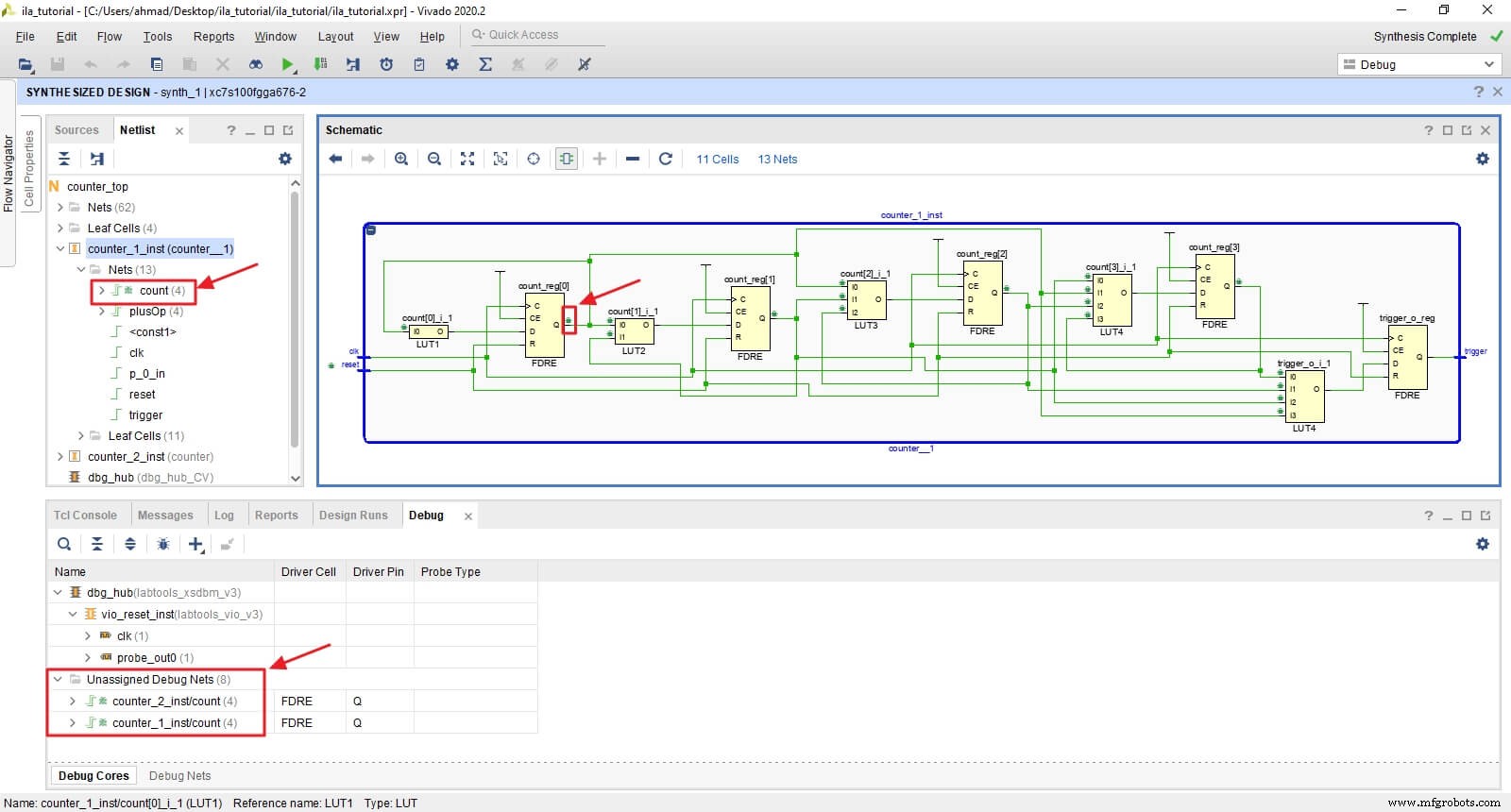

合成されたデザインから、信号がカウントすることがわかります counter_1_inst の両方で と counter_2_inst Unassigned Debug Nets の下にリストされています ネットリストの両方にバグ アイコンが付いています と回路図 .

ネットリストからの挿入

この挿入方法も簡単ですが、最初にデザインを合成し、次に各信号を手動でクリックしてデバッグ用にマークする必要があります。設計が大きく、多くの信号を監視したい場合、それは大変なことです。

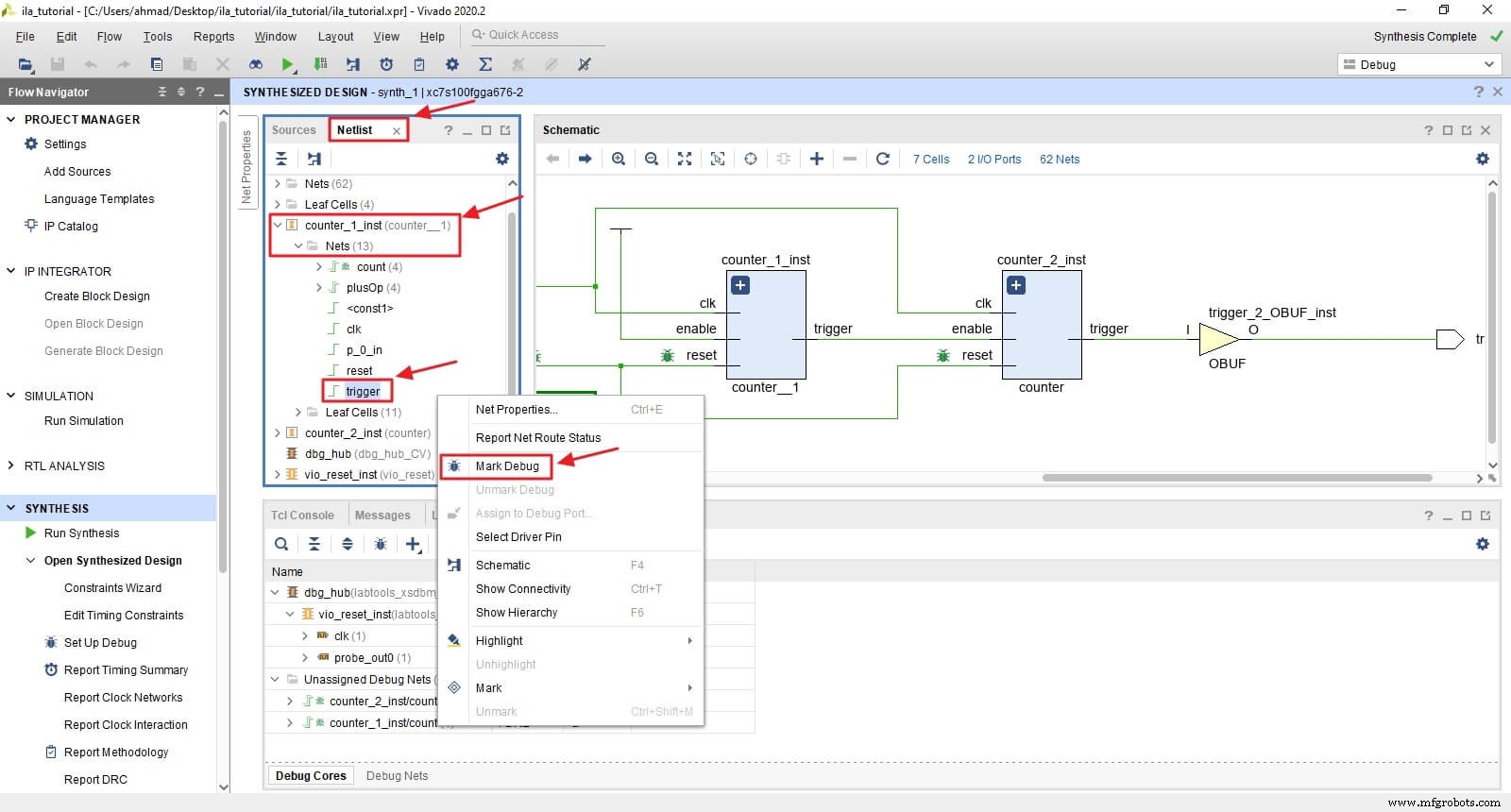

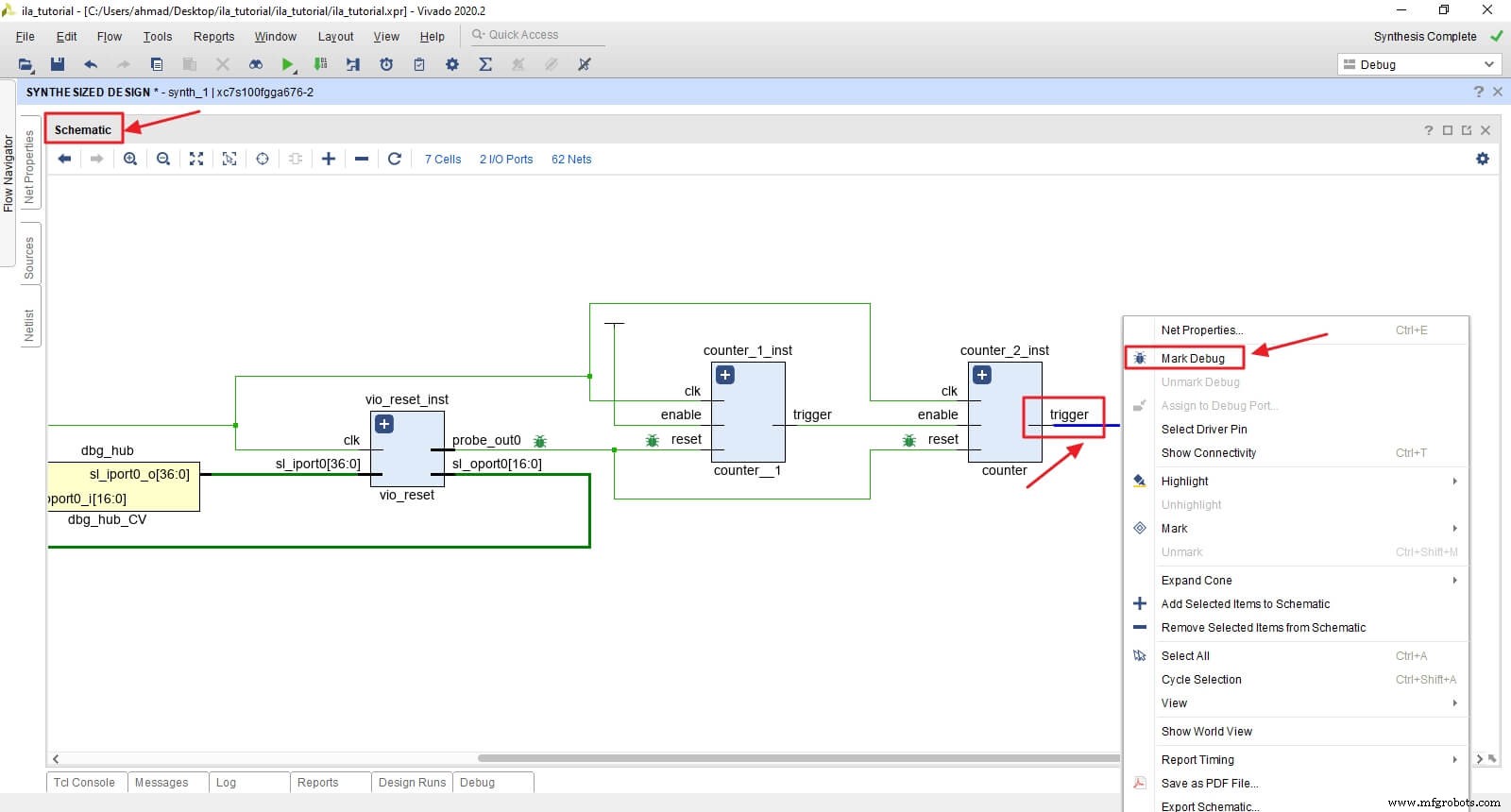

出力ポートのトリガーを調べます ネットリストを使用して両方のカウンターで .これは、ネットリスト ウィンドウから行うことができます または 回路図 信号ネットを見つけて右クリック その上で、[Mark Debug] を選択します。 .

ネットリスト ウィンドウから、トリガー を見つけます。 counter_1_inst → ネット → の下 トリガー .次に、それを右クリックして [Mark Debug] を選択します。 .

Schematic ウィンドウから trigger を見つけます counter_2_inst からの出力 .次に、それを右クリックして [Mark Debug] を選択します。 .

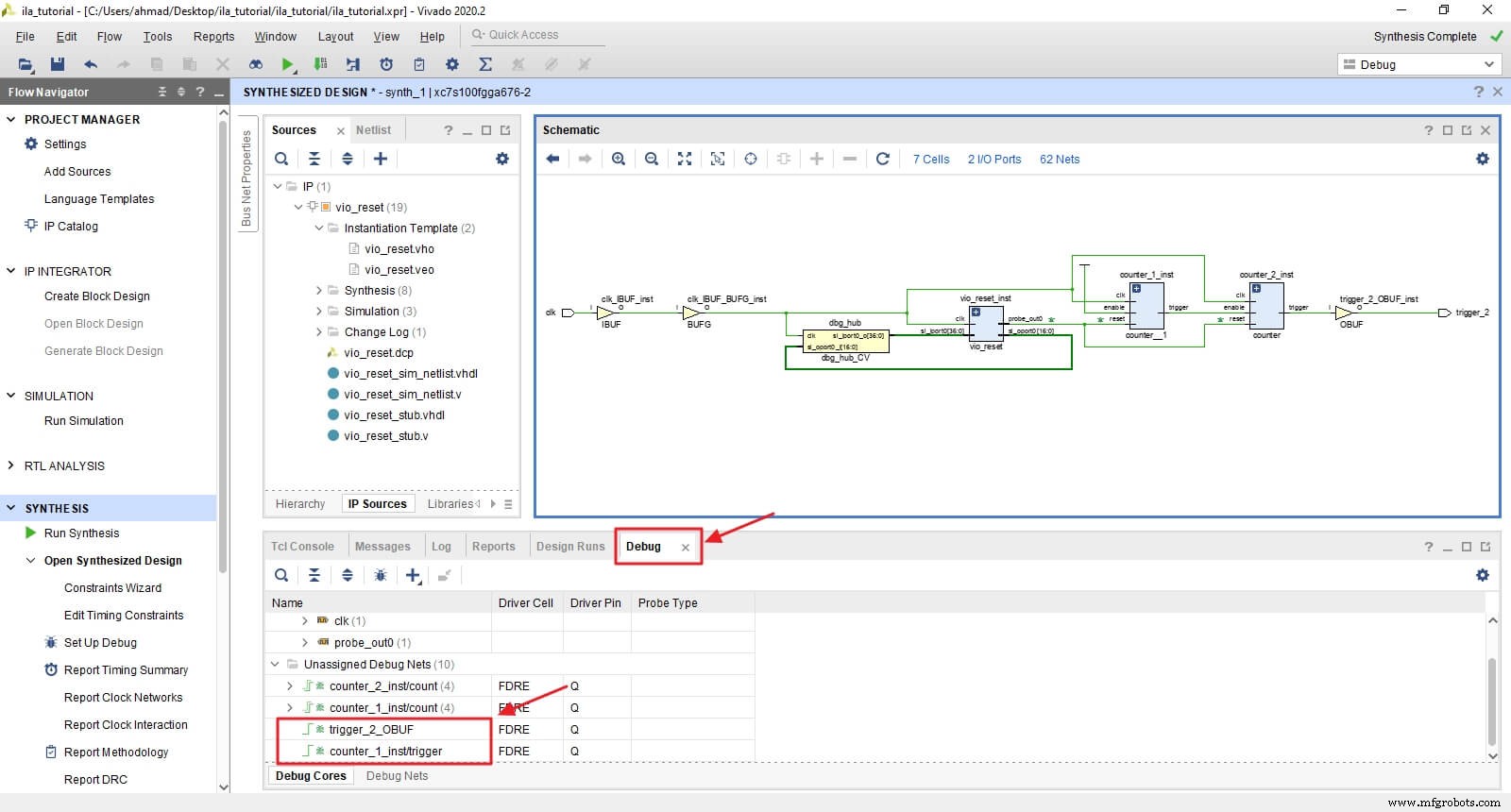

Unassigned Debug Nets の下にリストされていることがわかります。 .

ILA デバッグ コアの作成

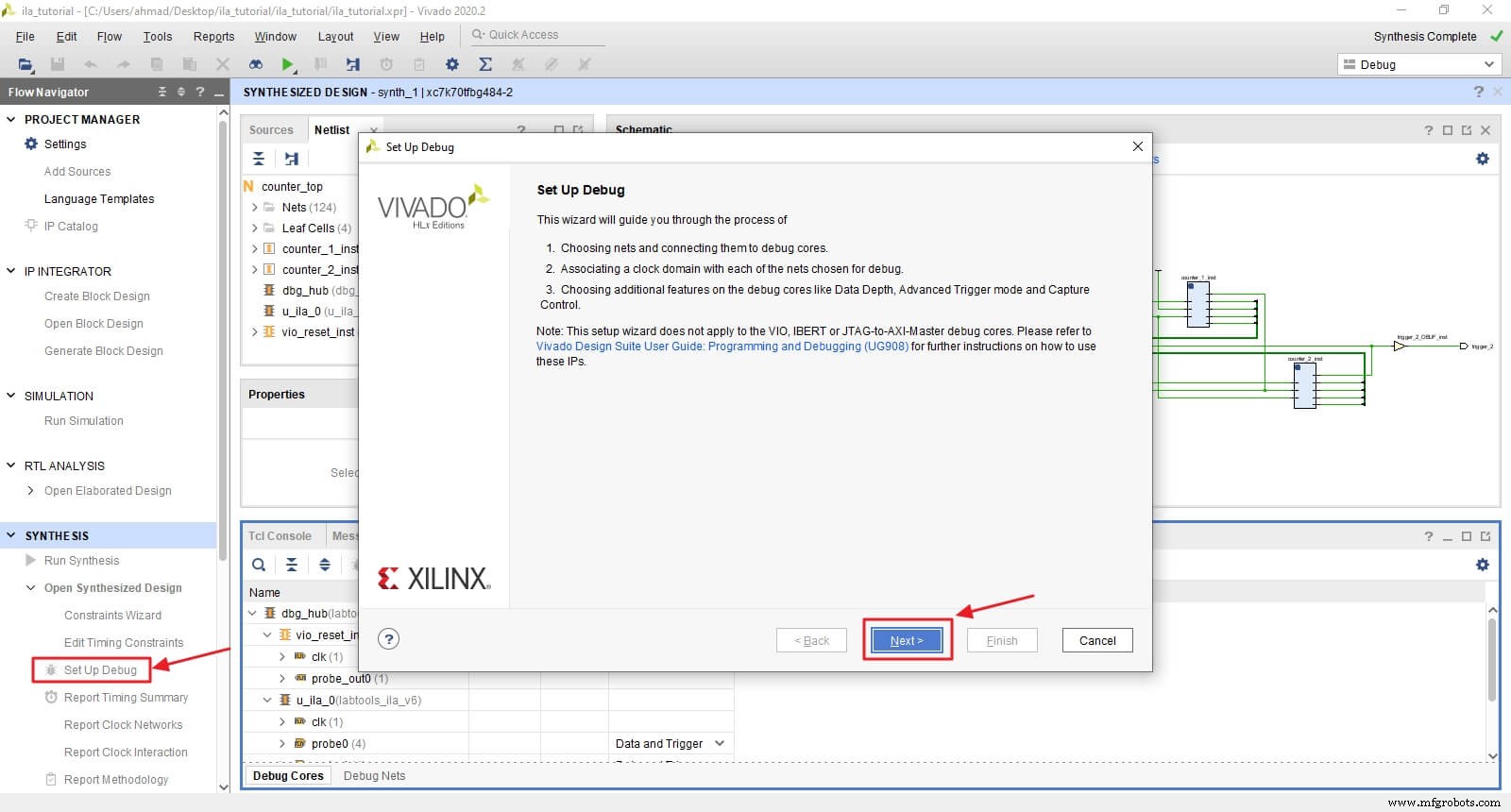

次に、ILA デバッグ コアを作成します。分析したい信号ごとにプローブを作成する必要があります。最も簡単な方法は、Vivado ウィザードの [Set Up Debug] を利用することです。 .

デバッグの設定 をクリックします [次へ] をクリックします。 .

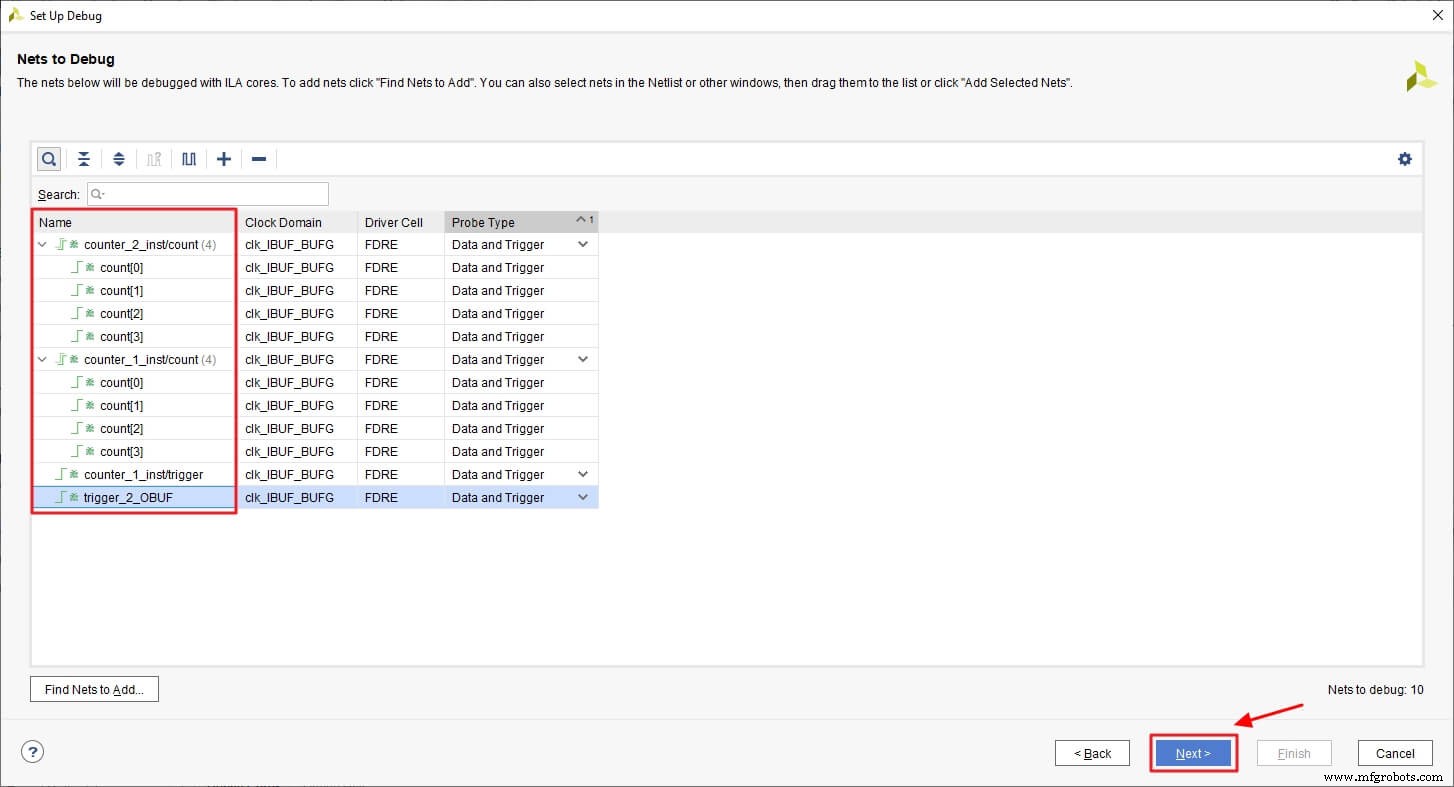

Vivado では、すべてのデバッグ信号がリストされ、クロック ドメインが自動的に取得されます。ここでは、4 つのシグナルがリストされていることがわかります。興味のないシグナルを削除したり、余分なシグナルを追加したりできますが、それらはすべて使用されます。

注: デバッグとしてマークしたすべてのシグナルを使用する必要はありません。

[次へ] をクリックします .

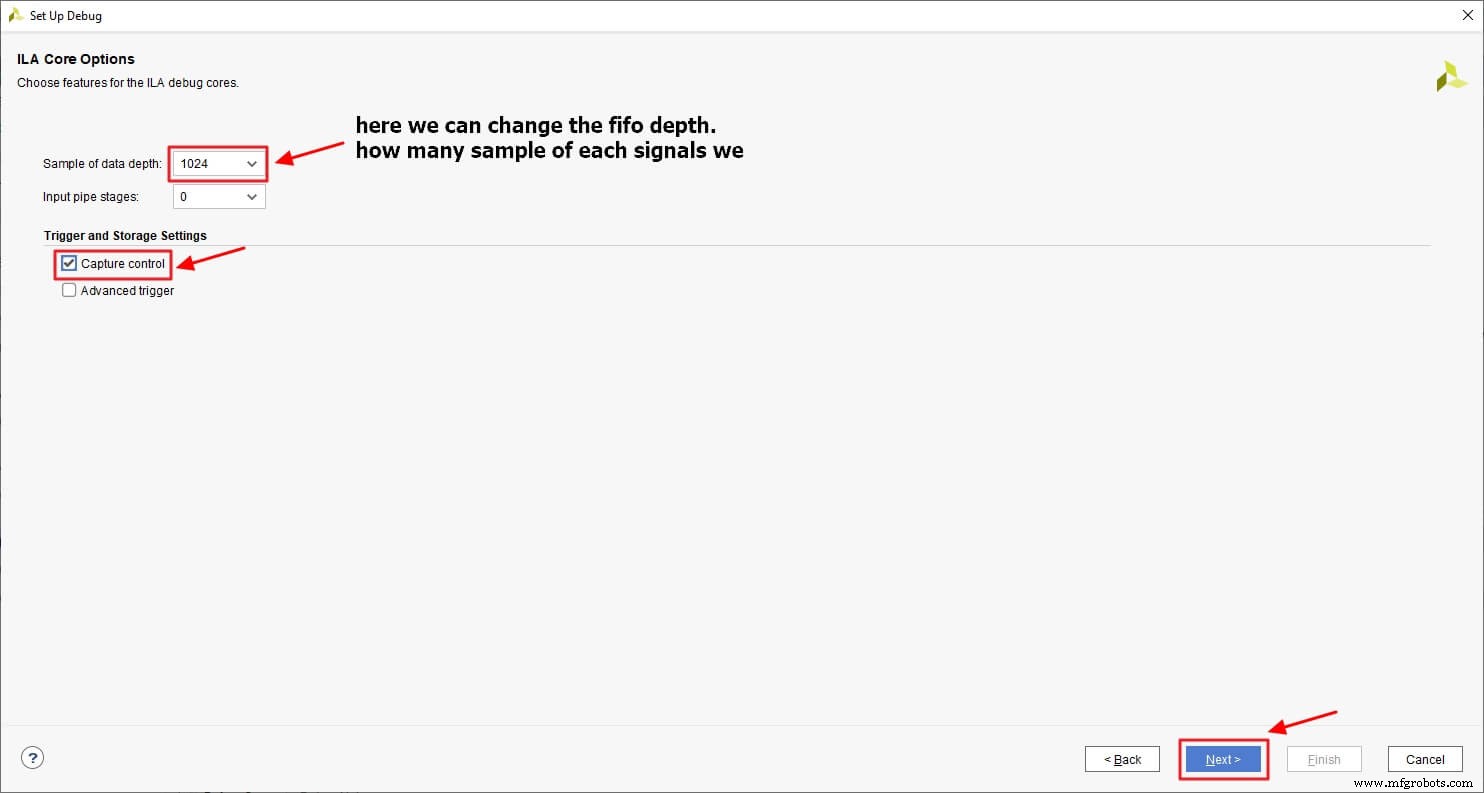

FIFO の深さを選択して ILA を設定します。 キャプチャ コントロールのチェック .この例では十分な深さであるため、FIFO を 1024 のままにしておくことができます。

[次へ] をクリックします .

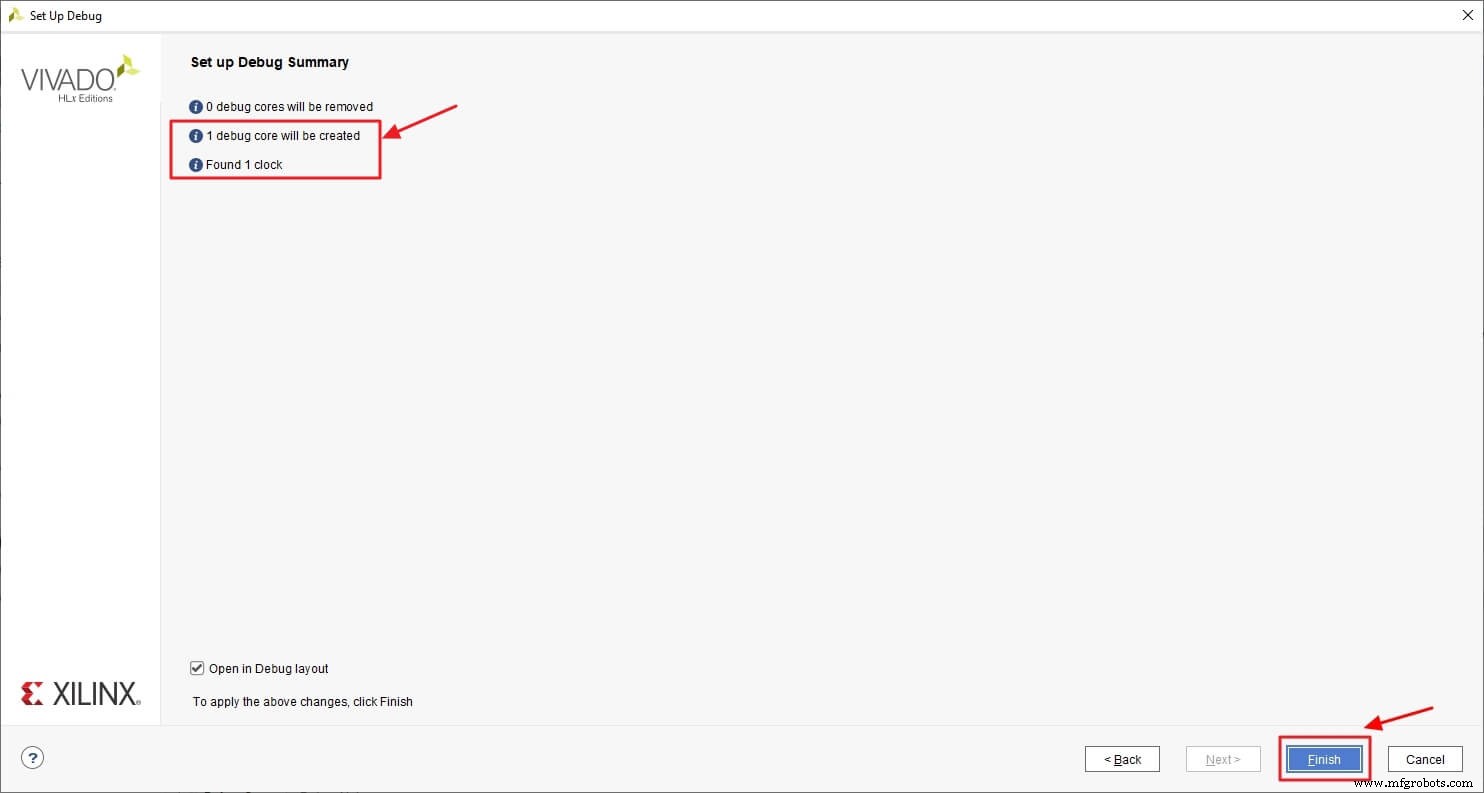

Vivado が 1 つのクロックを検出し、1 つのデバッグ コアを作成することがわかります。

終了をクリックします .

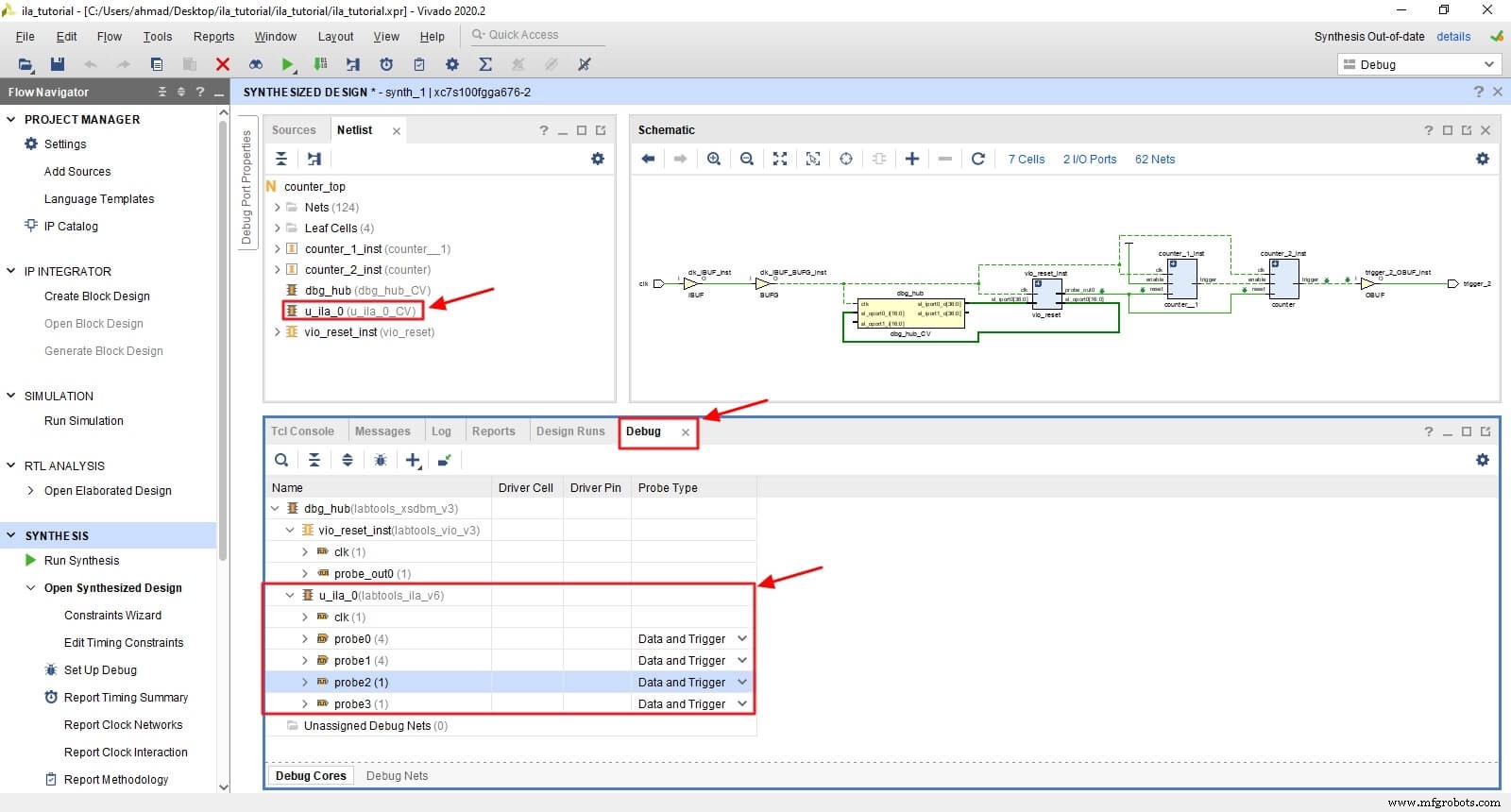

debug タブに 4 つのプローブが追加された ILA デバッグ コアが表示されます。 ネットリスト ウィンドウ .

重要: デザインに追加できるように、この段階で制約を保存することが非常に重要です。そうしないと、ILA コアを失う危険があります。

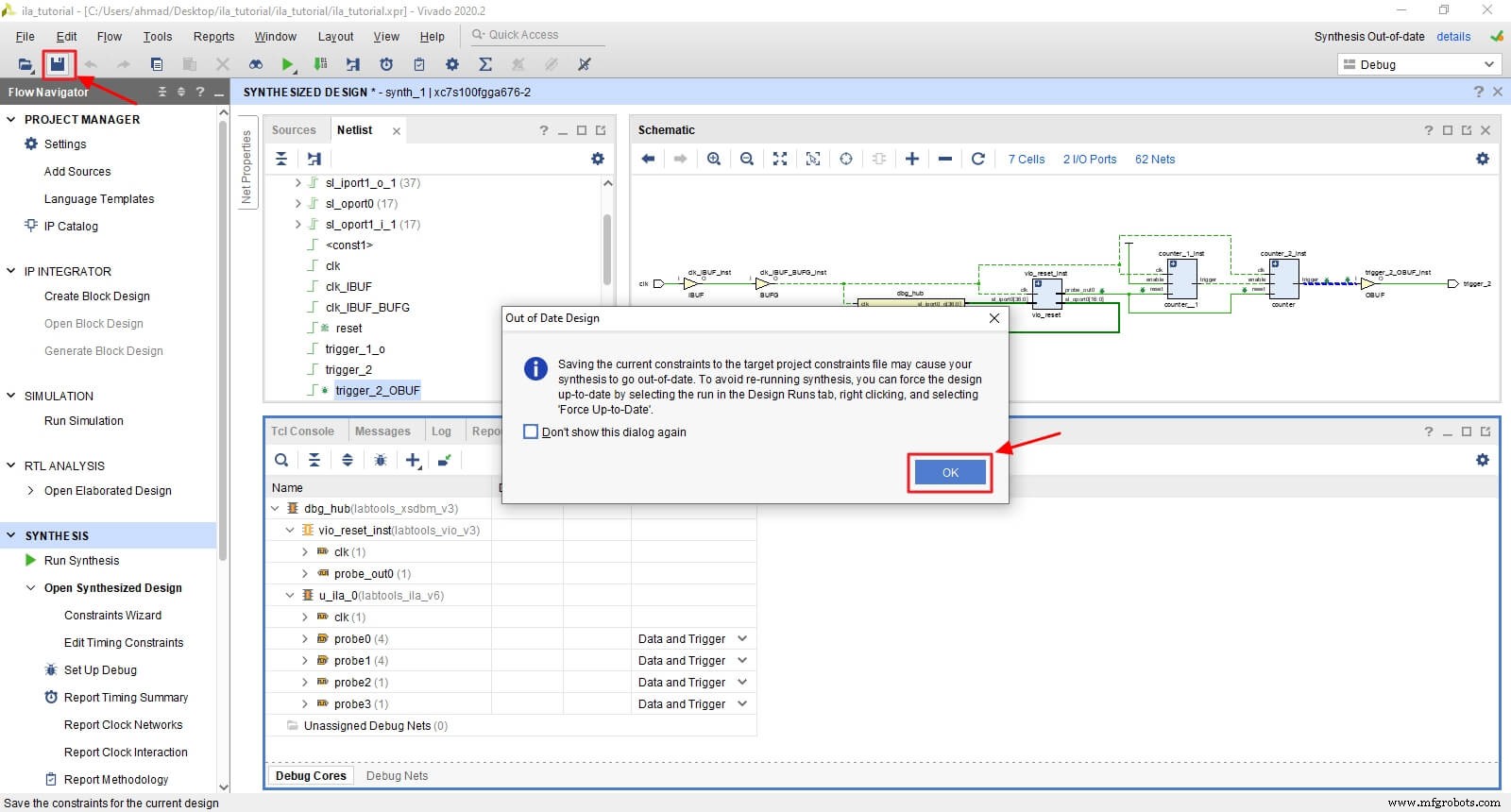

[保存] をクリックします アイコンを押すか、Ctrl+S を押します。

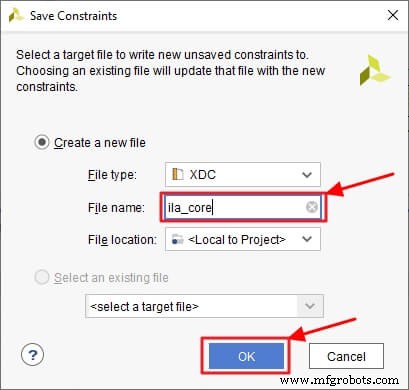

ファイルに ila_core という名前を付けます [OK] をクリックします .

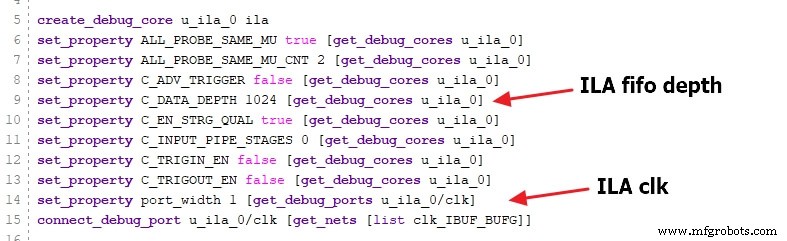

ila_core.xdc ファイルが制約に追加され、ILA のコードと設定が含まれます。

ファイルの内容を見てみましょう。ファイルを開くには、ソース ウィンドウ → 制約フォルダーを展開 → constr_1 を展開 します。 .

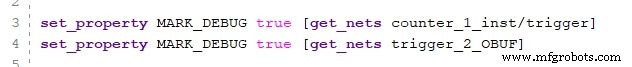

まず、ネットリスト挿入を使用してデバッグとマークした信号に、ファイルがデバッグ属性を追加していることがわかります。

次に、ILA コアの作成と構成について説明します。

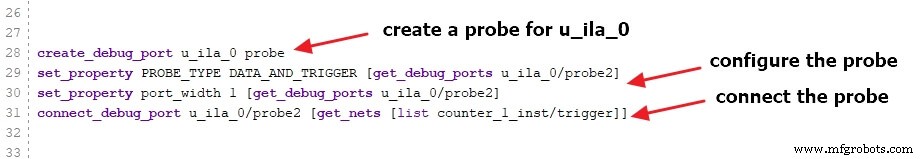

次に、各プローブの作成、構成、および接続を確認します。

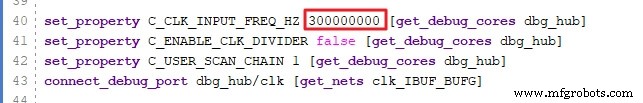

次に、デバッグ ハブ (dbg_hub) の作成を確認します。 ).

デバッグ ハブは、Vivado IDE とデバッグ コア (ILA および VIO) 間の通信を担当します。クロック周波数を定義していることがわかります (デフォルトは 300 MHz)。そのクロックをクロック周波数に合わせて変更し、ファイルを保存する必要があります。

注: ILA および Debug_hub に接続されているクロックは、フリーランニング クロックである必要があります。

これで ILA が完成し、保存されました。 ILA を合成済みデザインに追加できるように、合成を再実行する必要があります。

合成の実行をクリックします そしてOK .

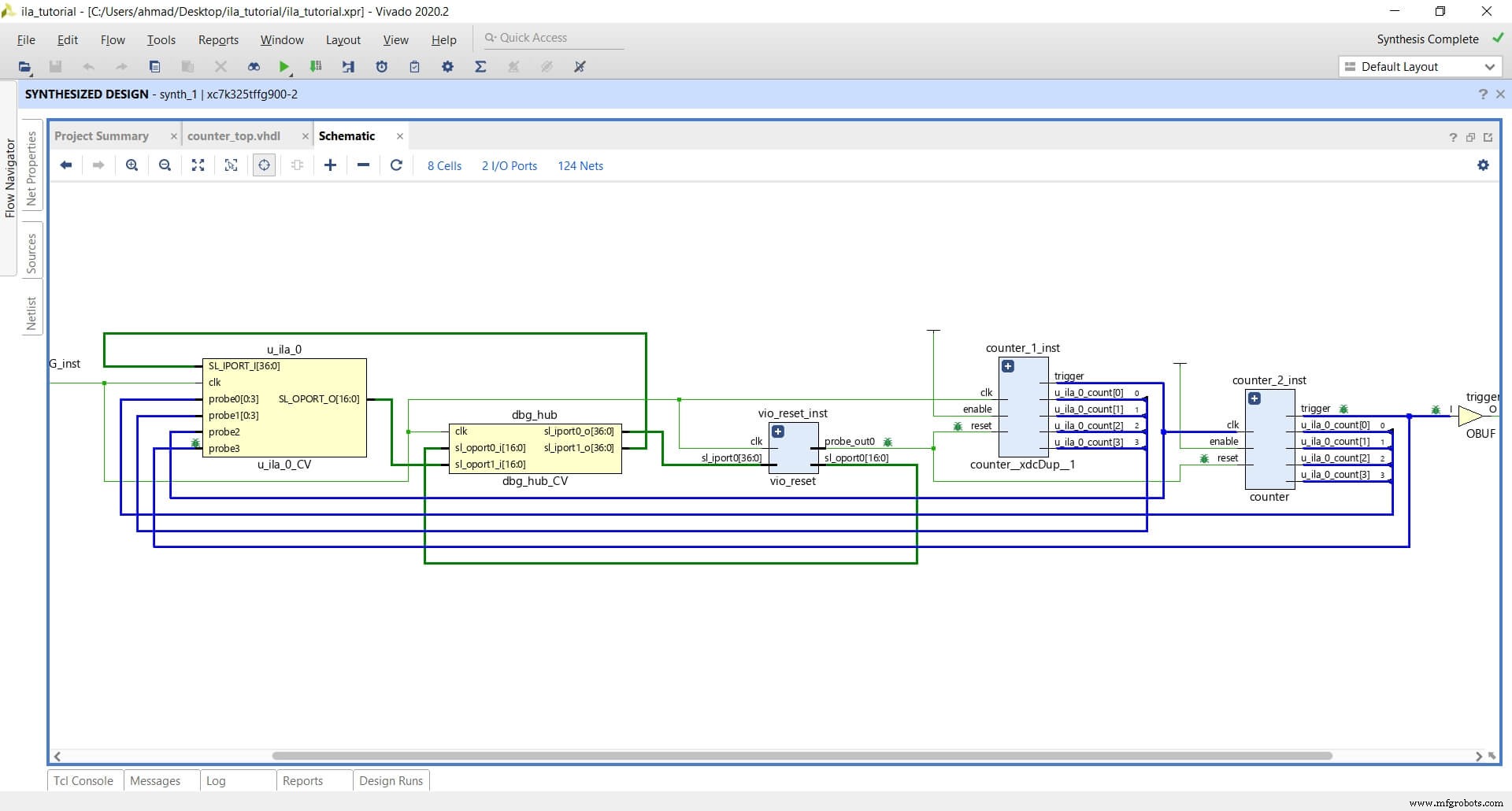

Vivado が合成の実行を終了したら、[Open Synthesized Design] をクリックします。 そして回路図 .

Vivado が ILA と Debug_Hub をデザインに追加し、デバッグ信号を ILA プローブに接続したことを確認できます。

これで、デザインを実装してビットストリームを生成し、デザインをテストする準備が整いました。

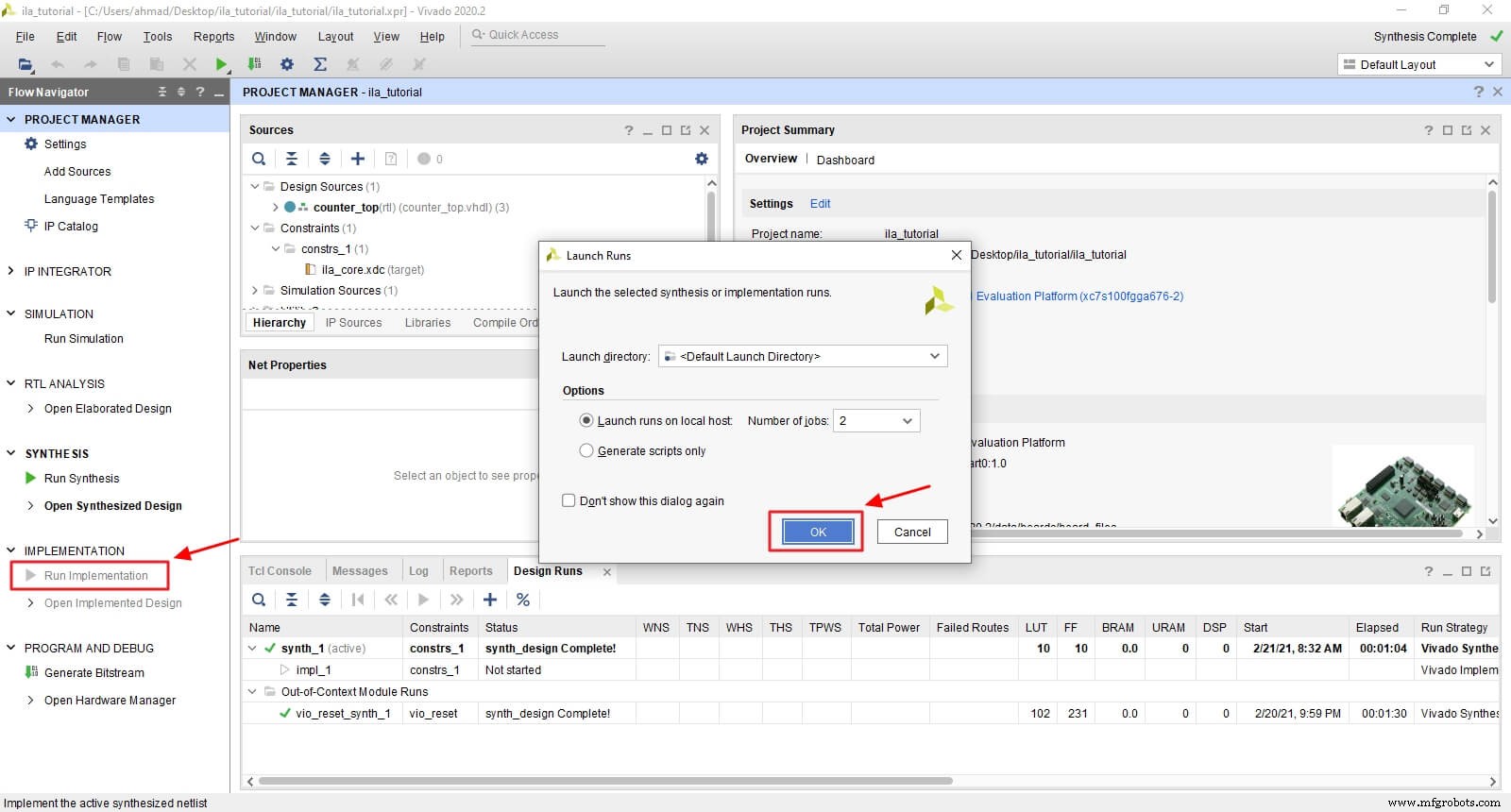

[実装の実行] をクリックします。 そしてOK .

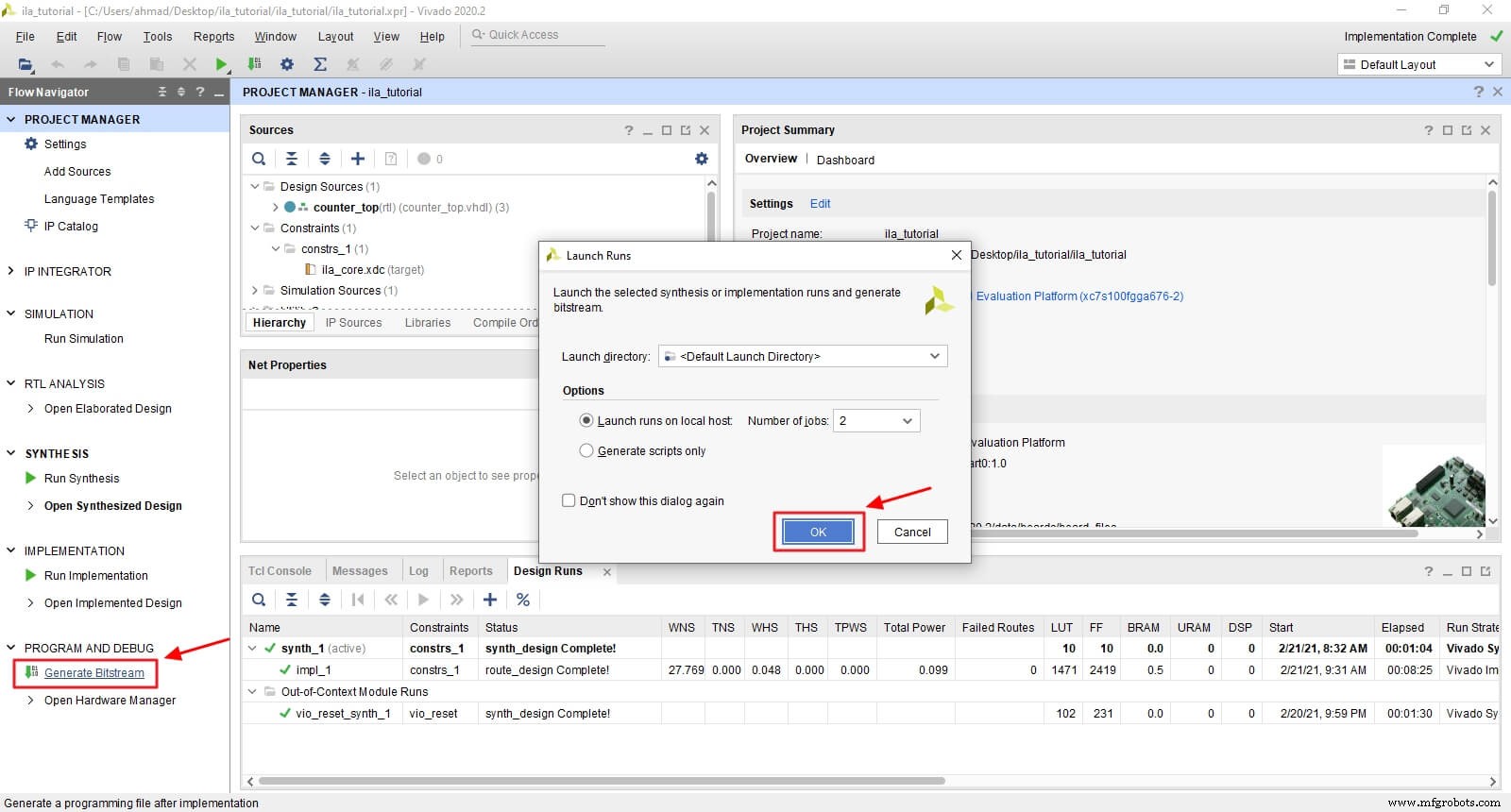

Vivado でインプリメンテーションの実行が終了したら、[Generate Bitstream] をクリックします。 そしてOK .

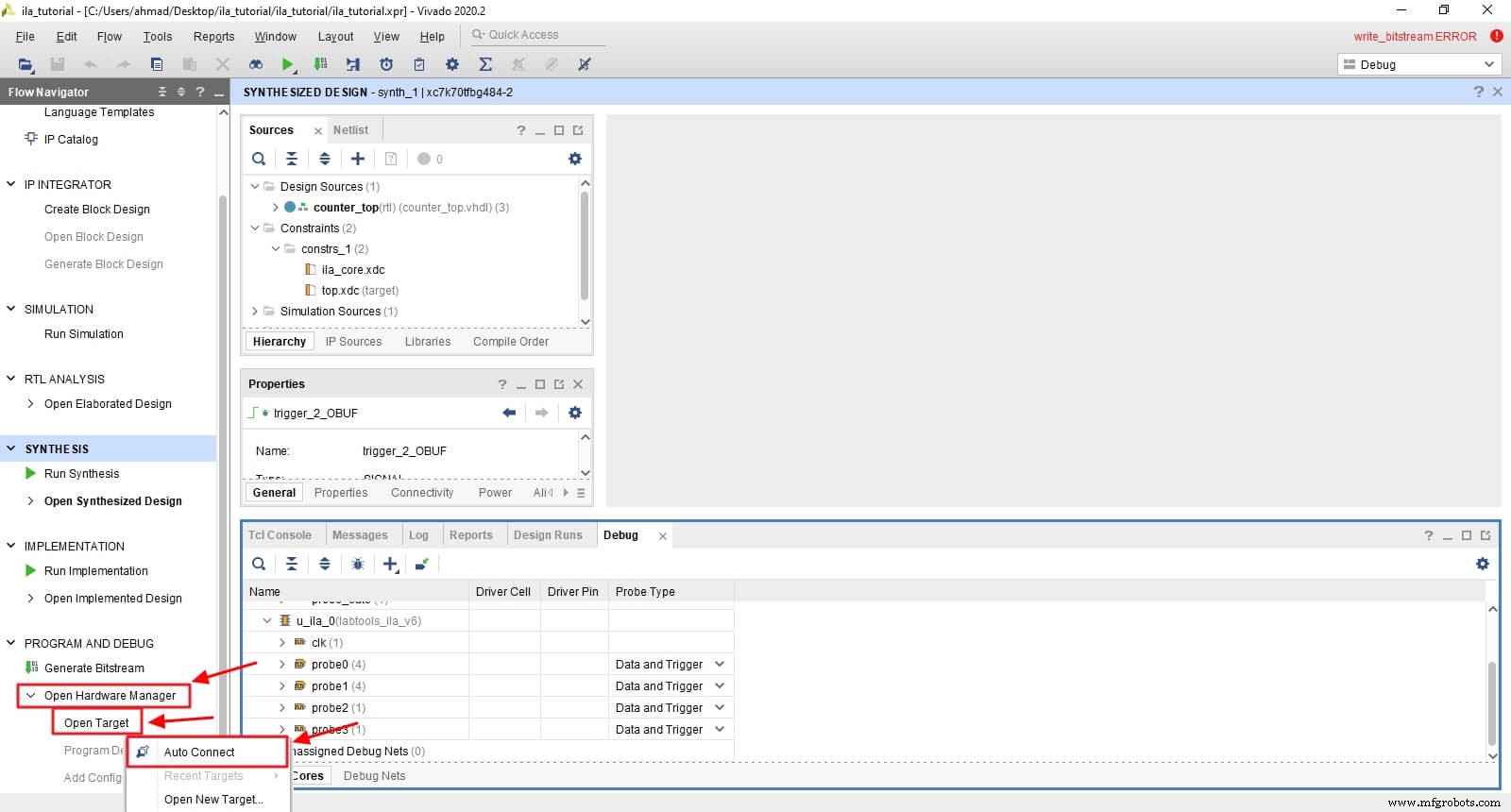

Vivado によるビットストリームの生成が終了したら、[Open Hardware Manager] をクリックします。 ターゲットを開く そして最後に 自動接続 .

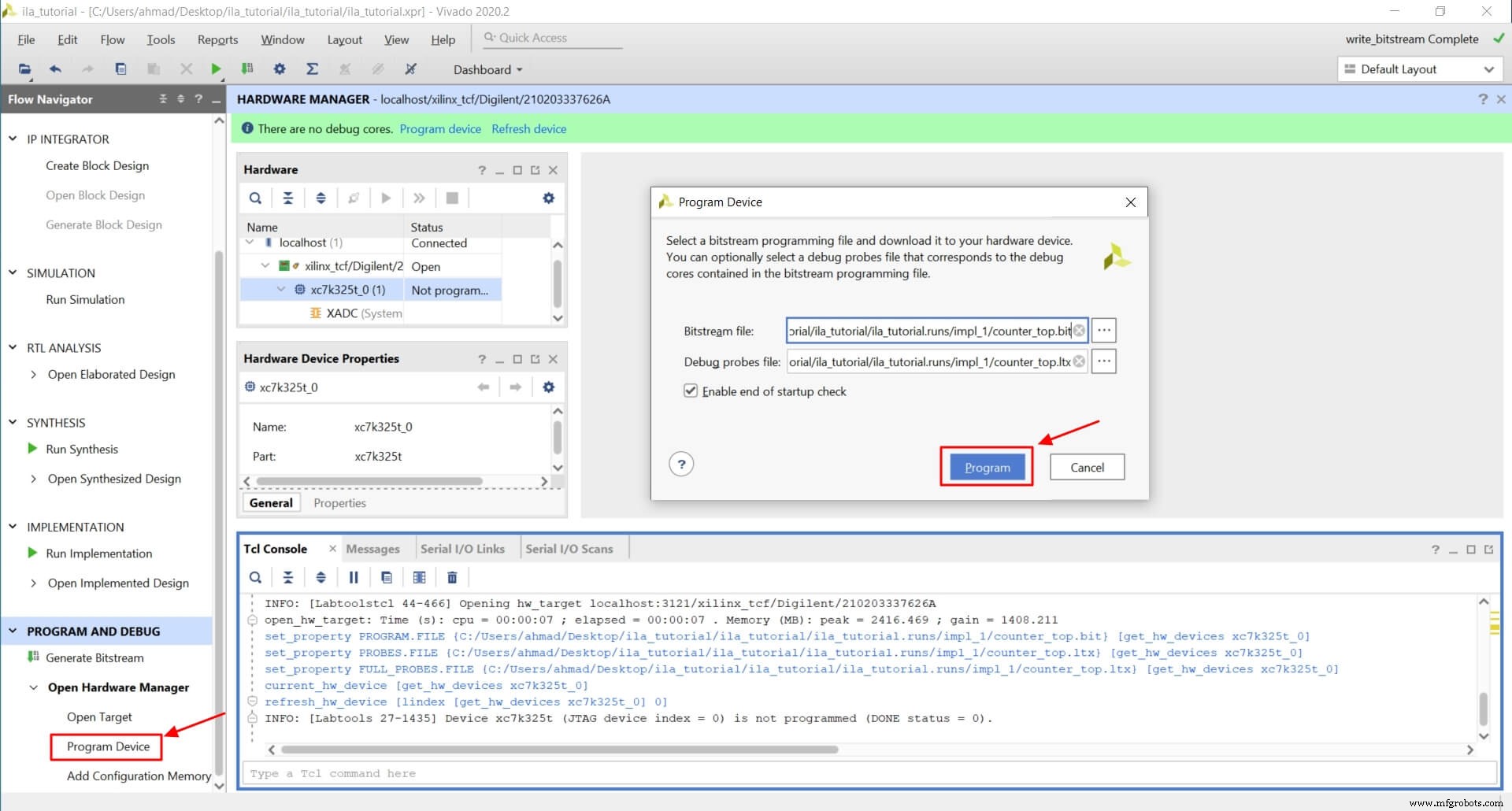

次に、ビット ファイル (*.bit) とデバッグ プローブ ファイル (*.ltx) を使用して FPGA をプログラムする必要があります。 Vivado が自動的に検索します。

プログラム デバイスをクリックします そして プログラム .

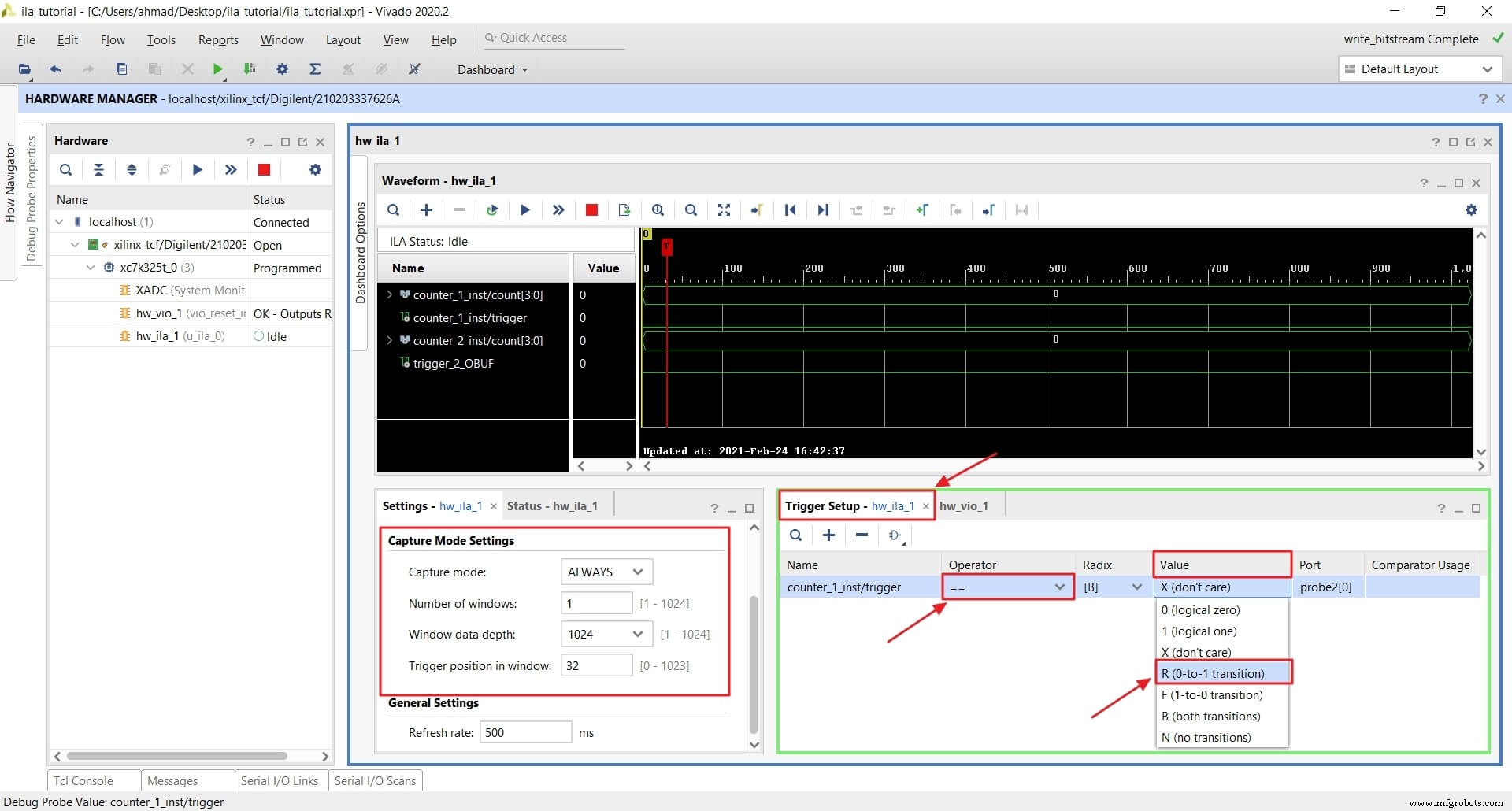

ILA トリガーの設定

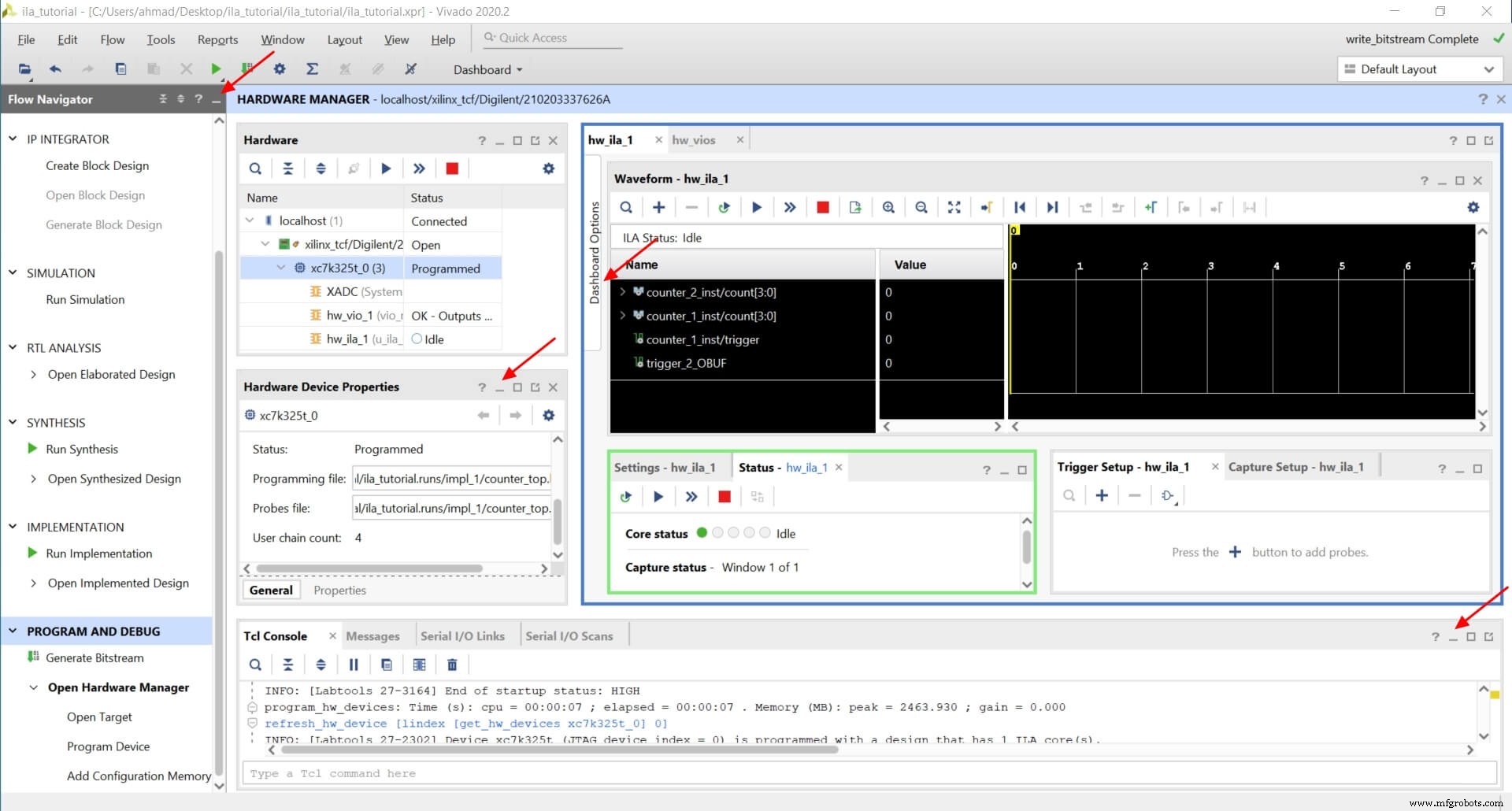

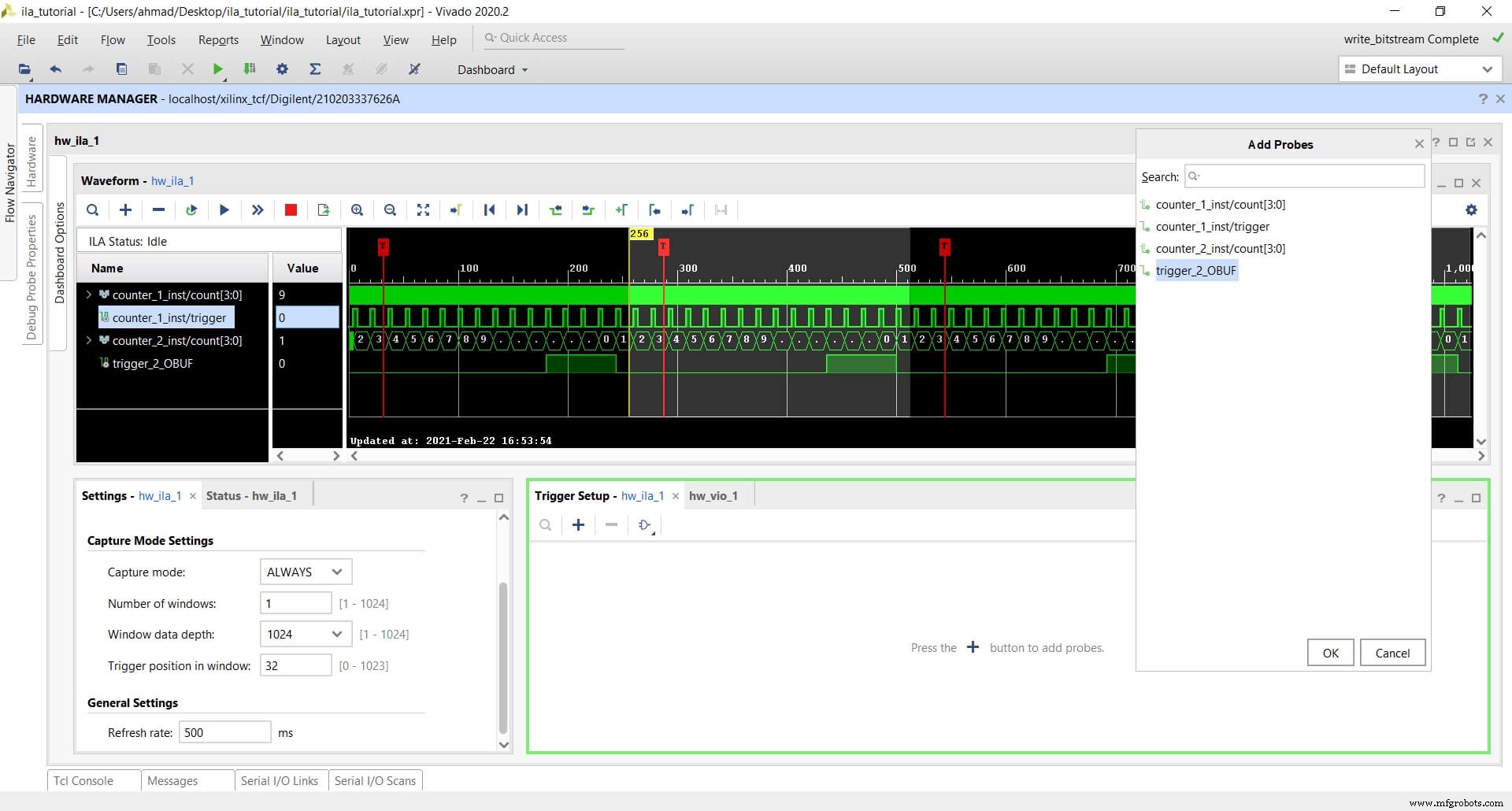

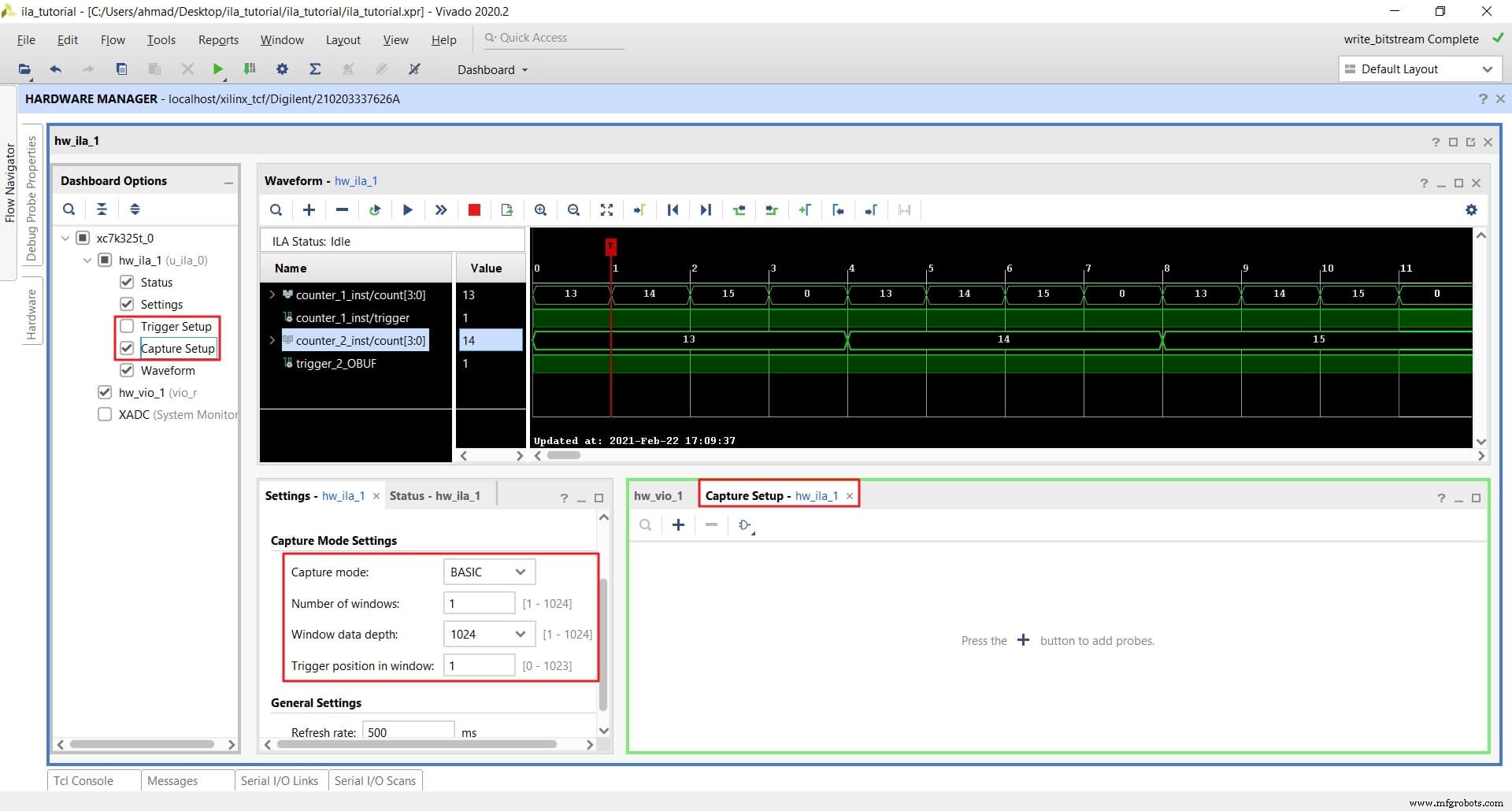

デバイスをプログラムすると、Vivado の GUI レイアウトが変更され、新しい hw_ila_1 ダッシュボードが開き、いくつかのウィンドウが含まれています。

快適に作業できるように、不要なウィンドウを最小化します。

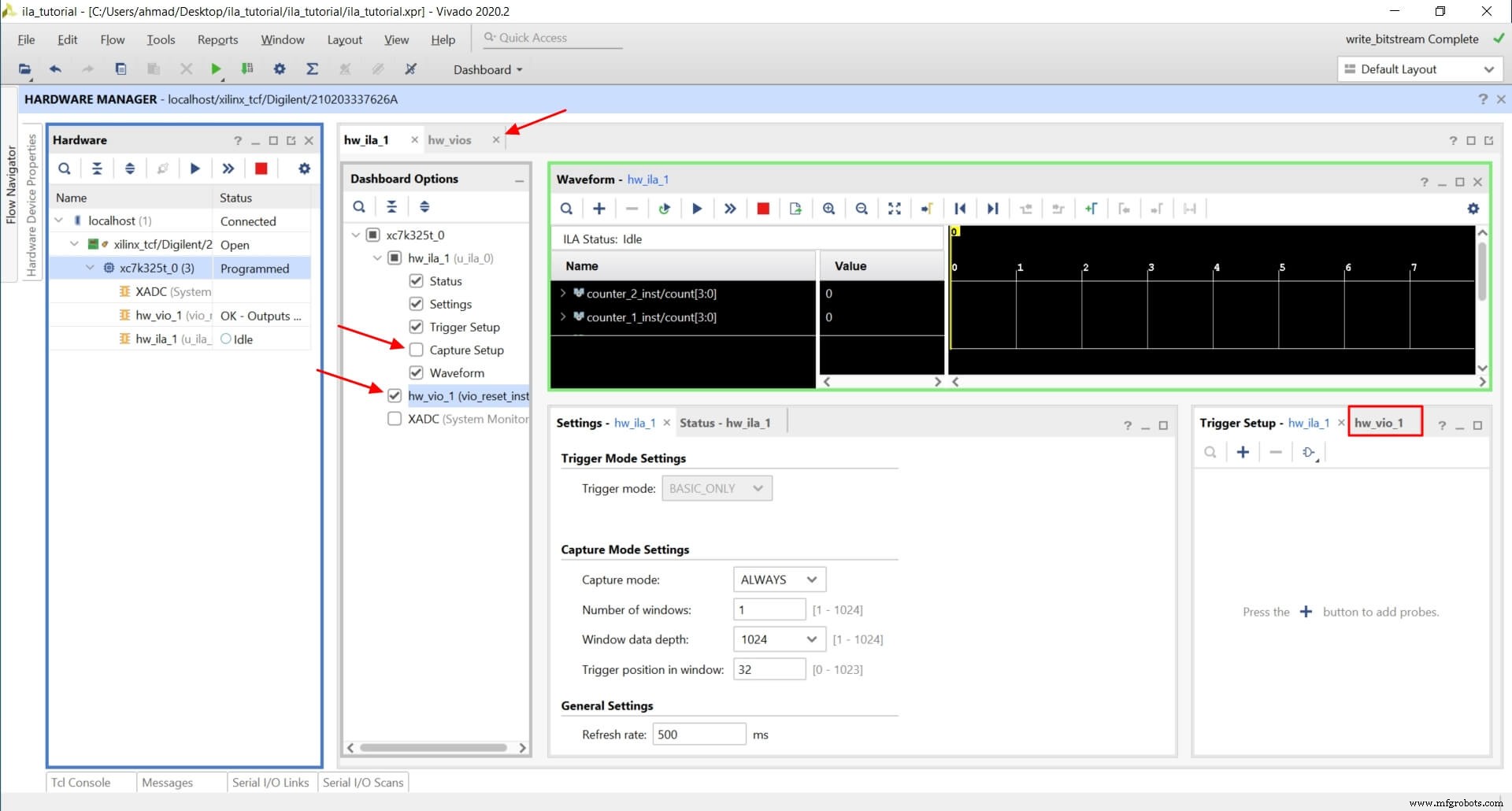

ダッシュボードのオプションから、hw_vio_1 を確認します キャプチャ設定のチェックを外します .

また、hw_vios を閉じます hw_vio_1 をチェックしたときのタブ 、トリガー設定に追加されました ウィンドウ。

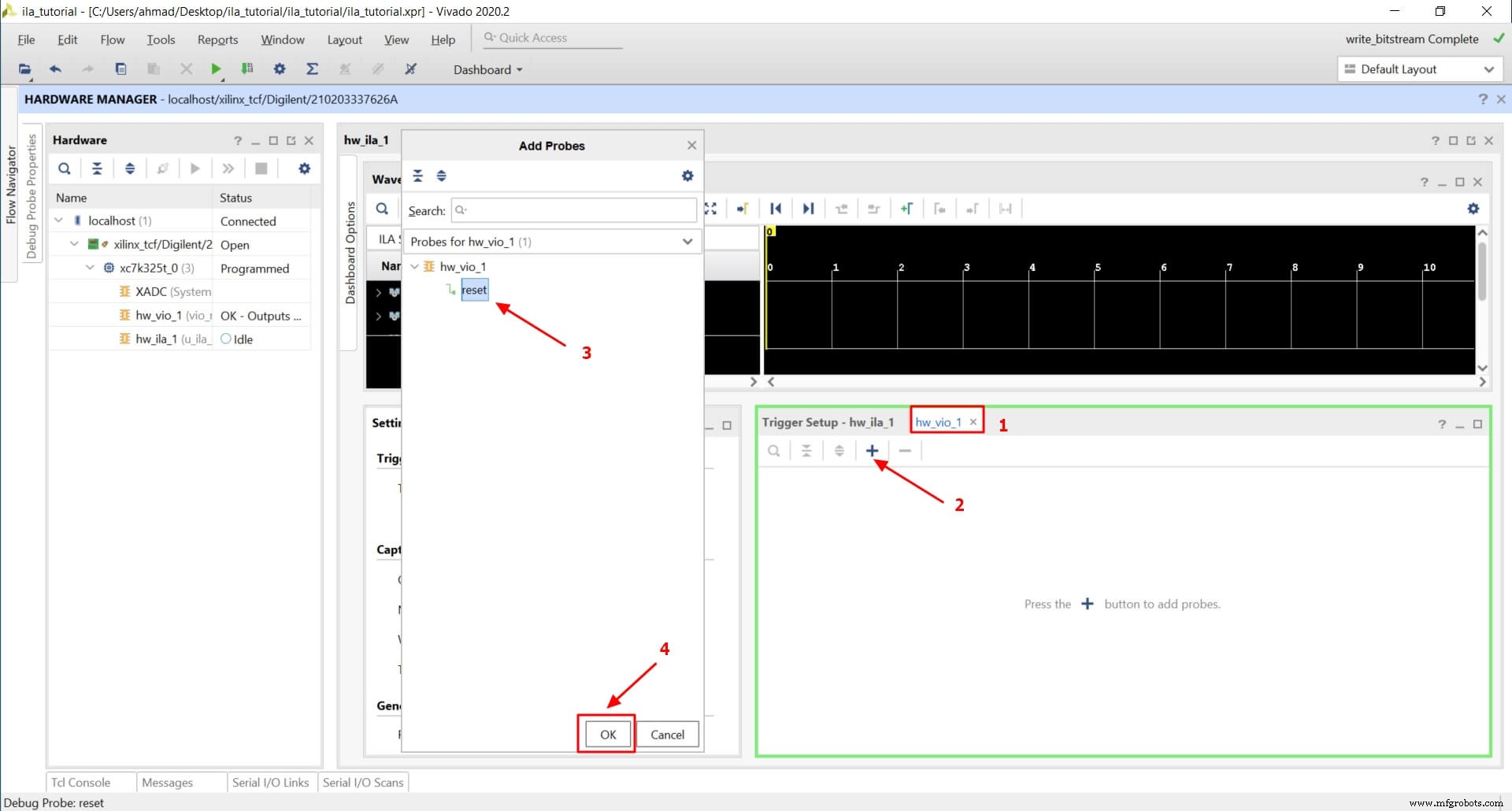

ここで、リセットを追加する必要があります リセットを制御できるように VIO へのボタン .

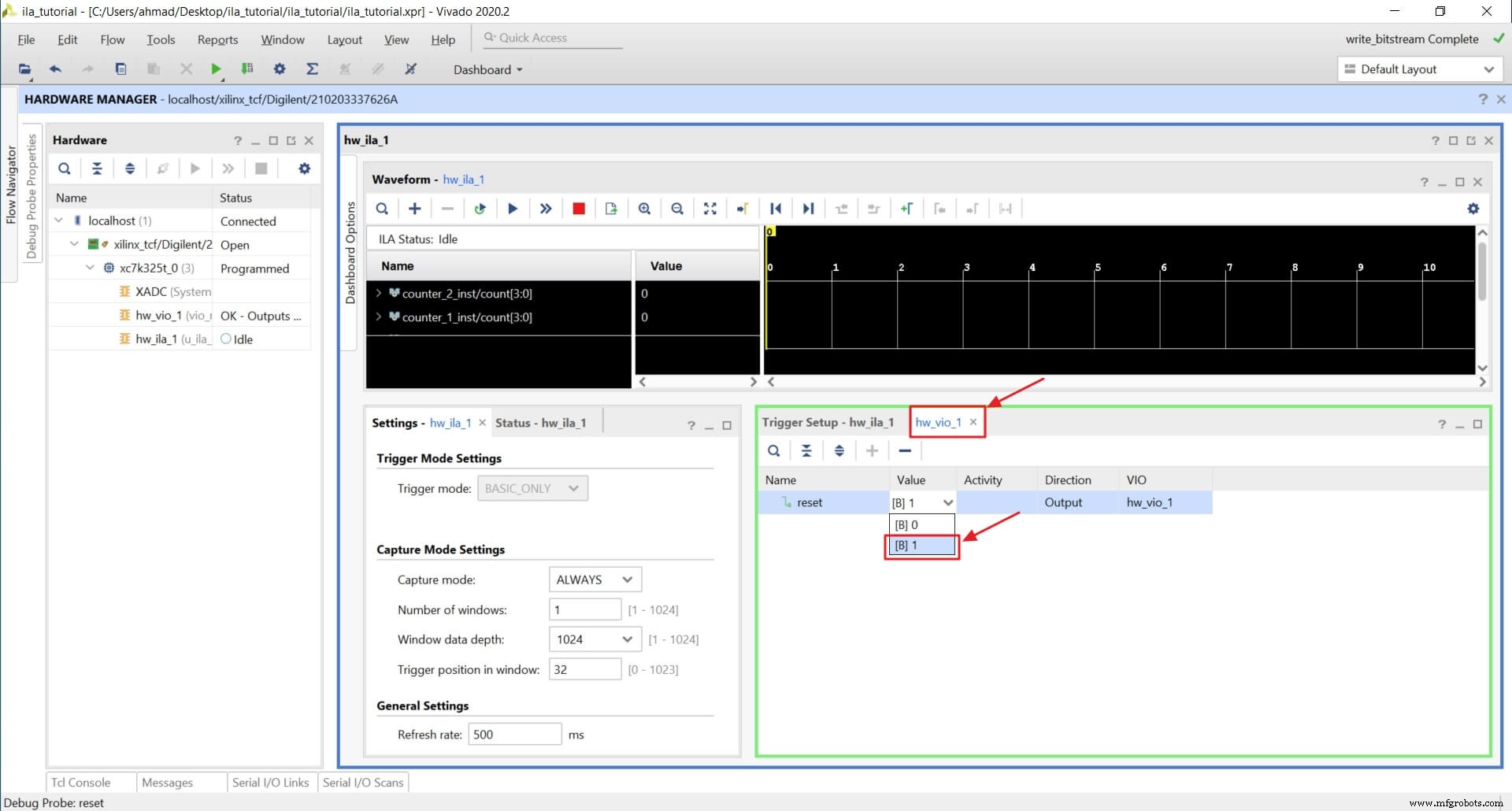

hw_vio_1 をクリックします リセットを追加します 下の図に示すように。

hw_vio_1 であることがわかります リセットが含まれるようになりました

リセットの値を変更します 1 でない場合は、vio_reset で 1 にします。

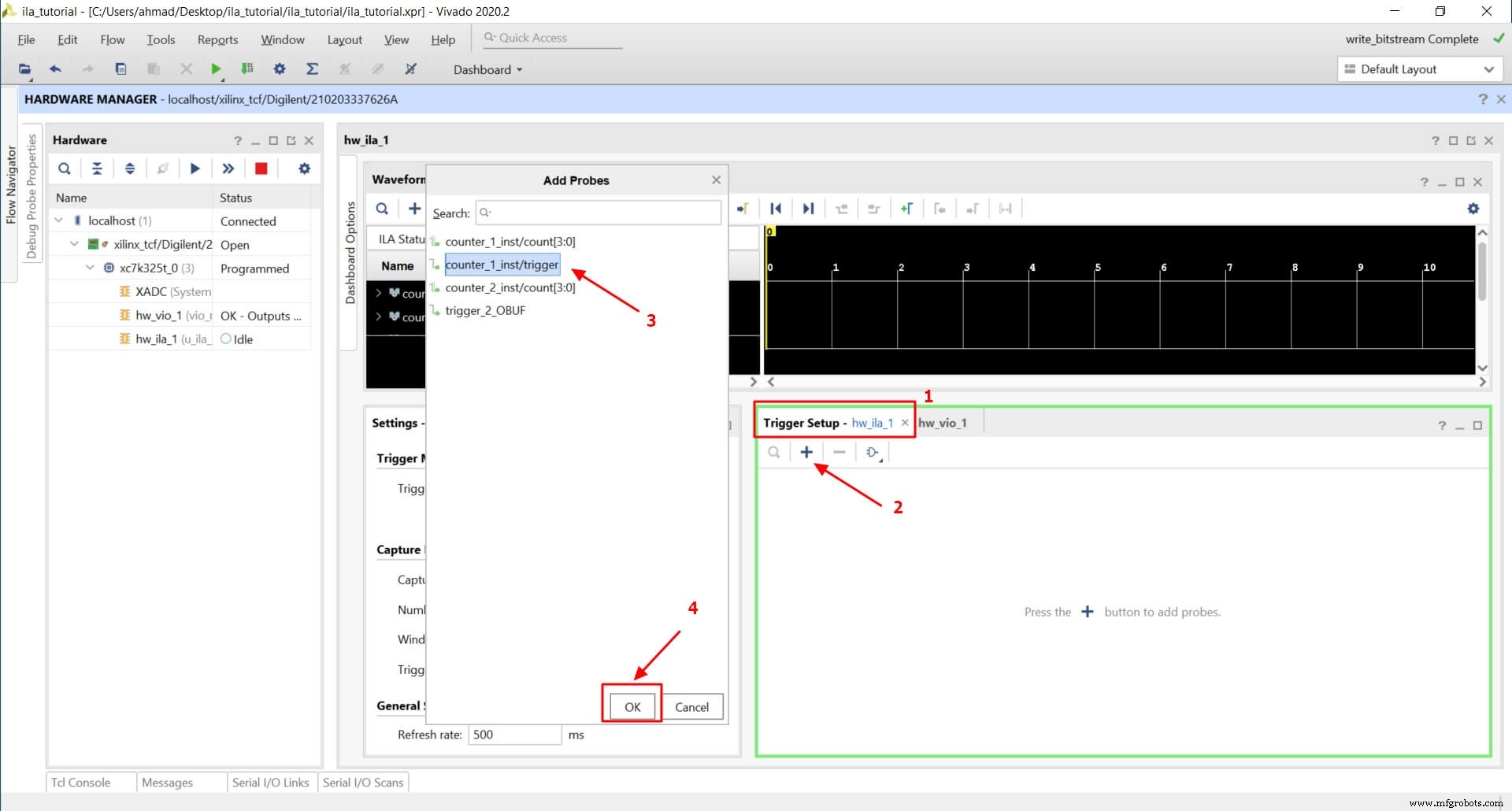

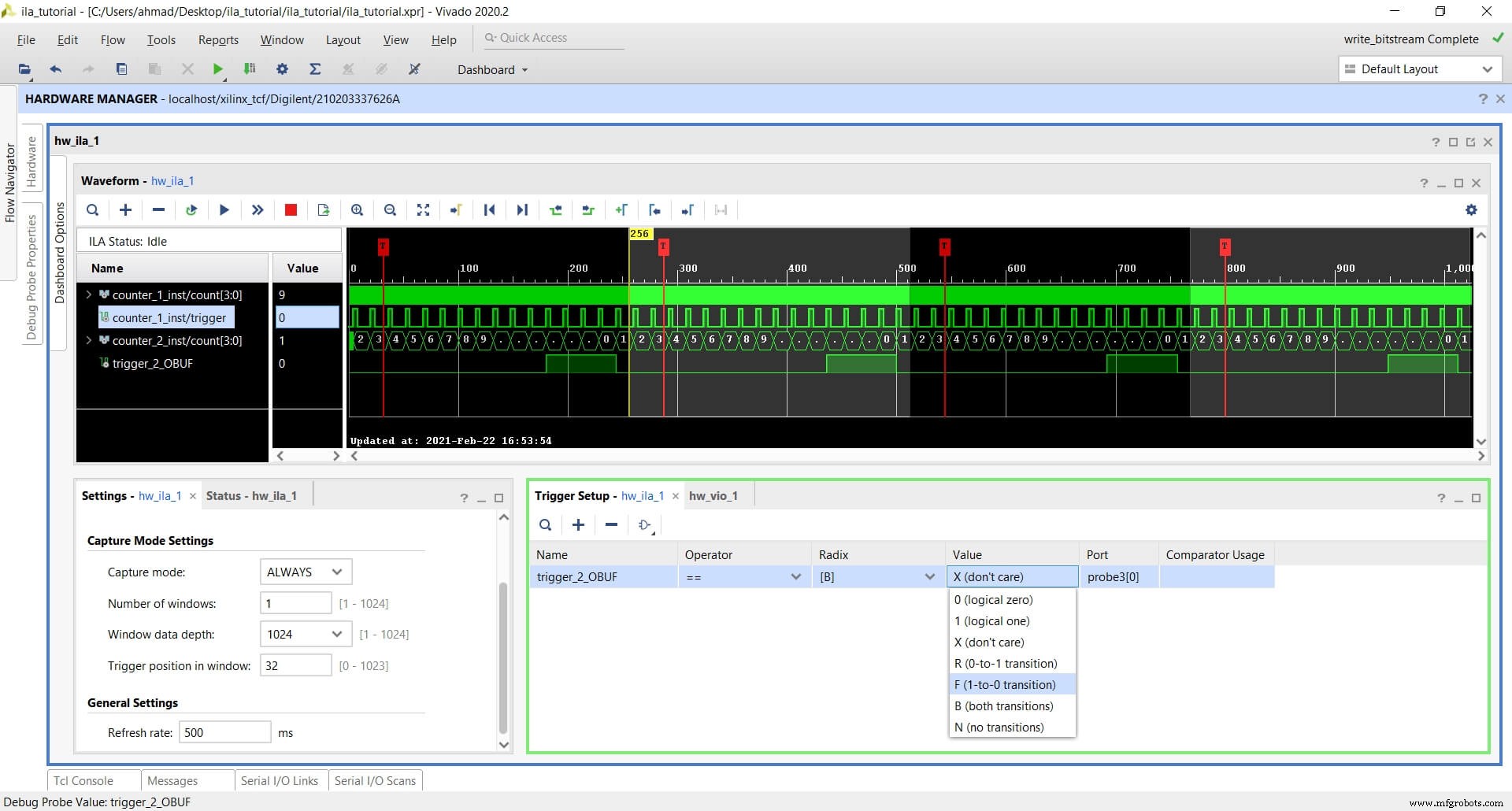

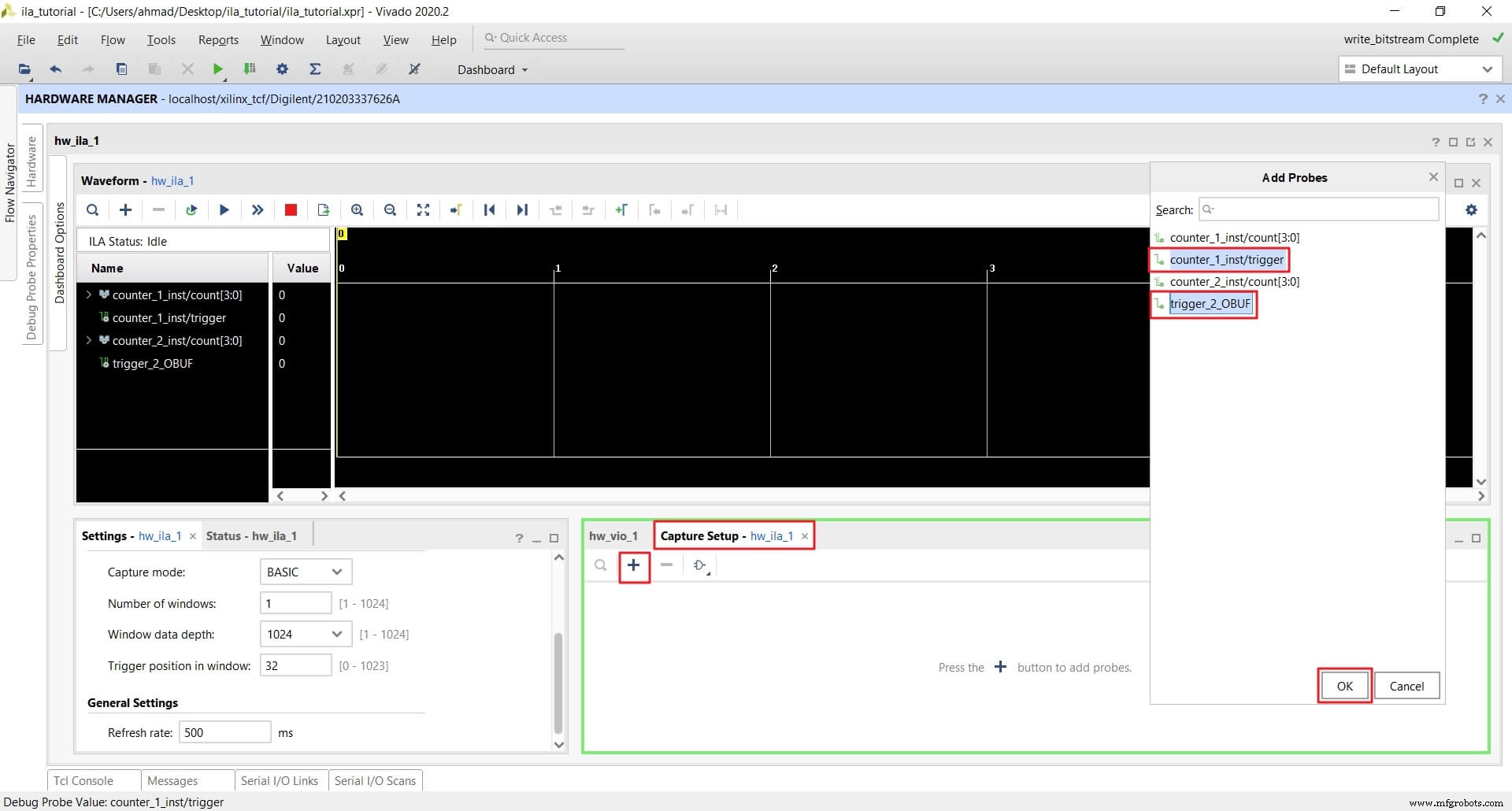

次に、使用するトリガーを追加します。トリガー信号の値を変更すると、ILA はプローブされた信号の記録を開始します。

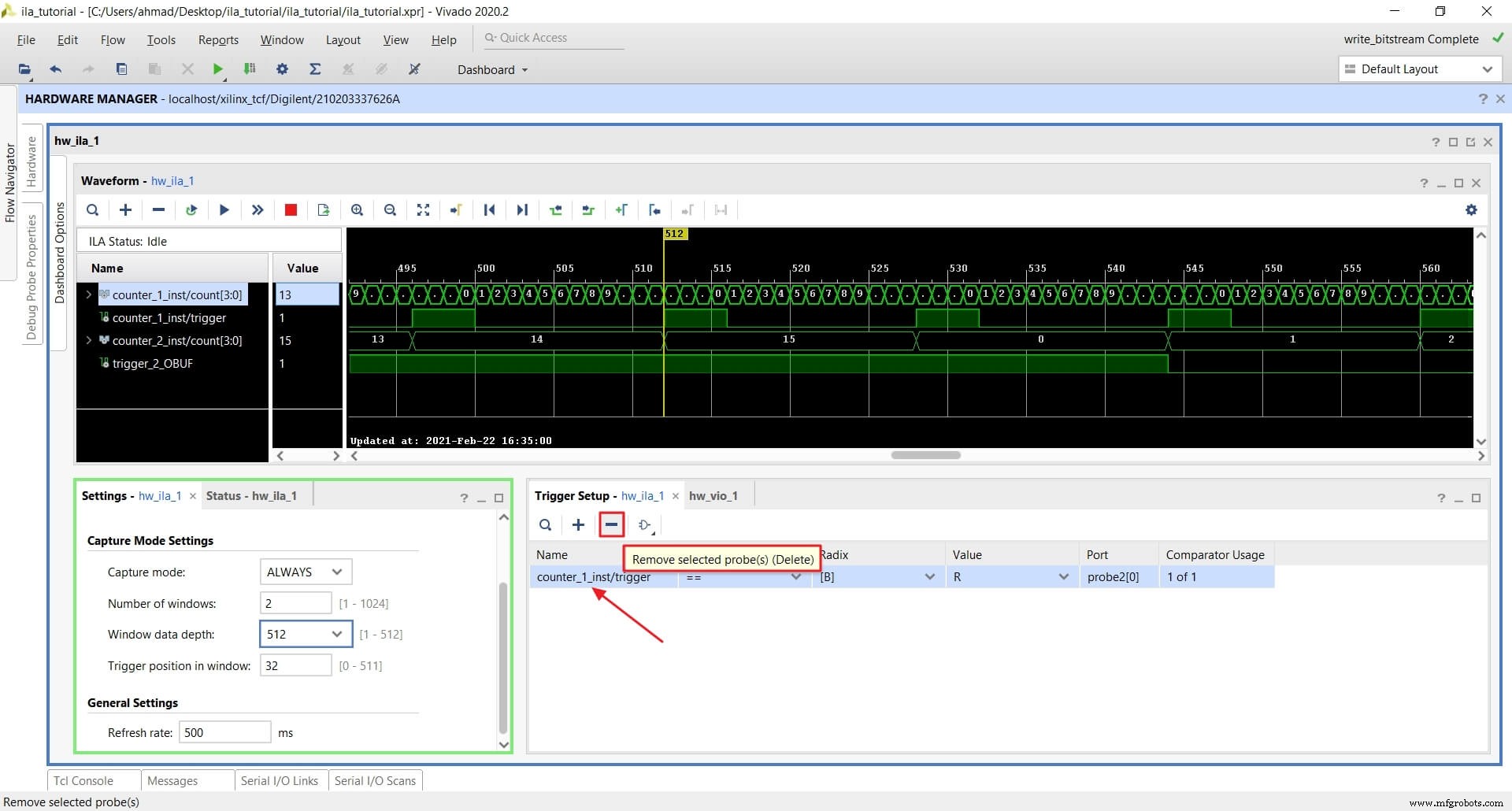

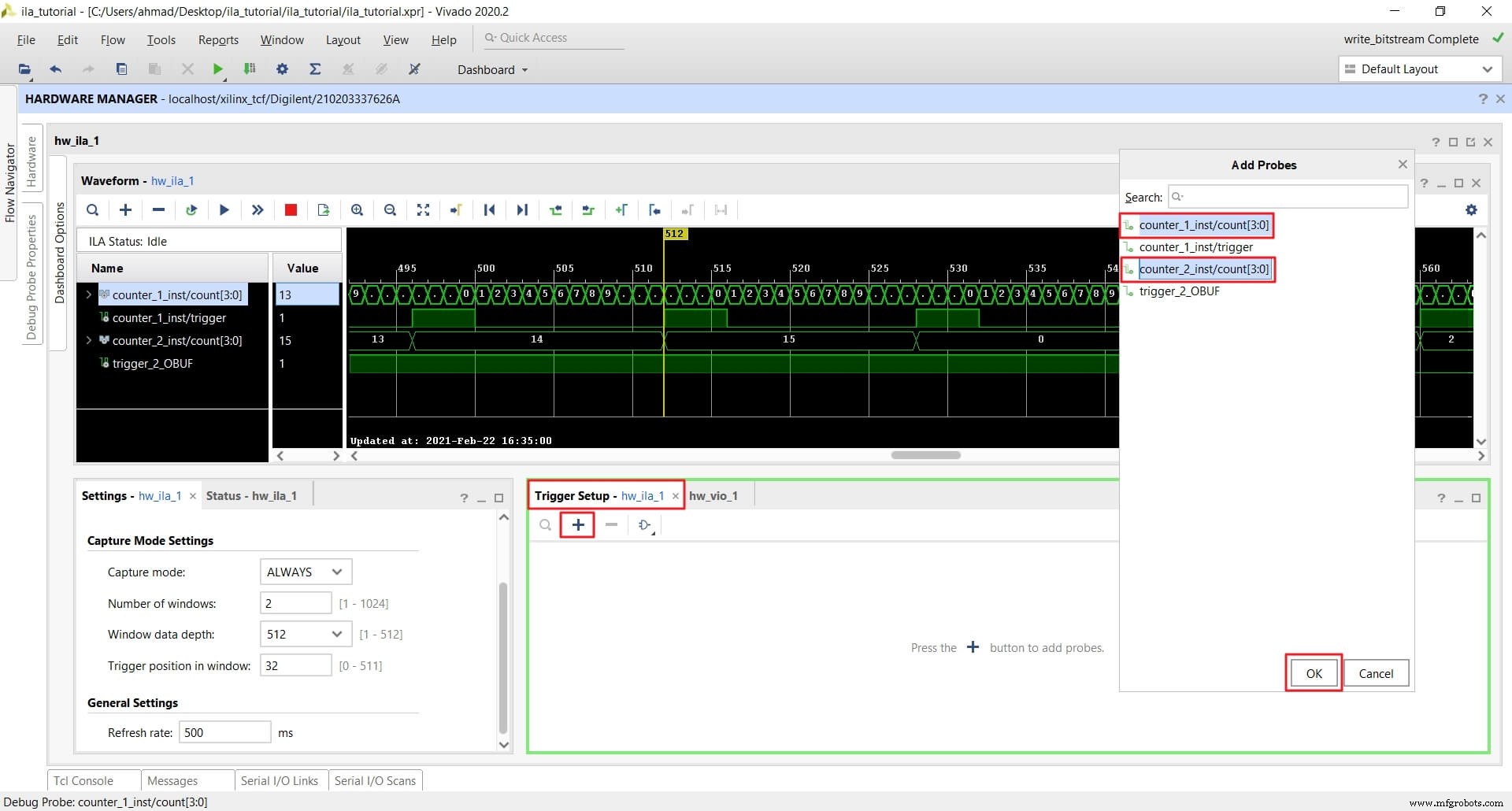

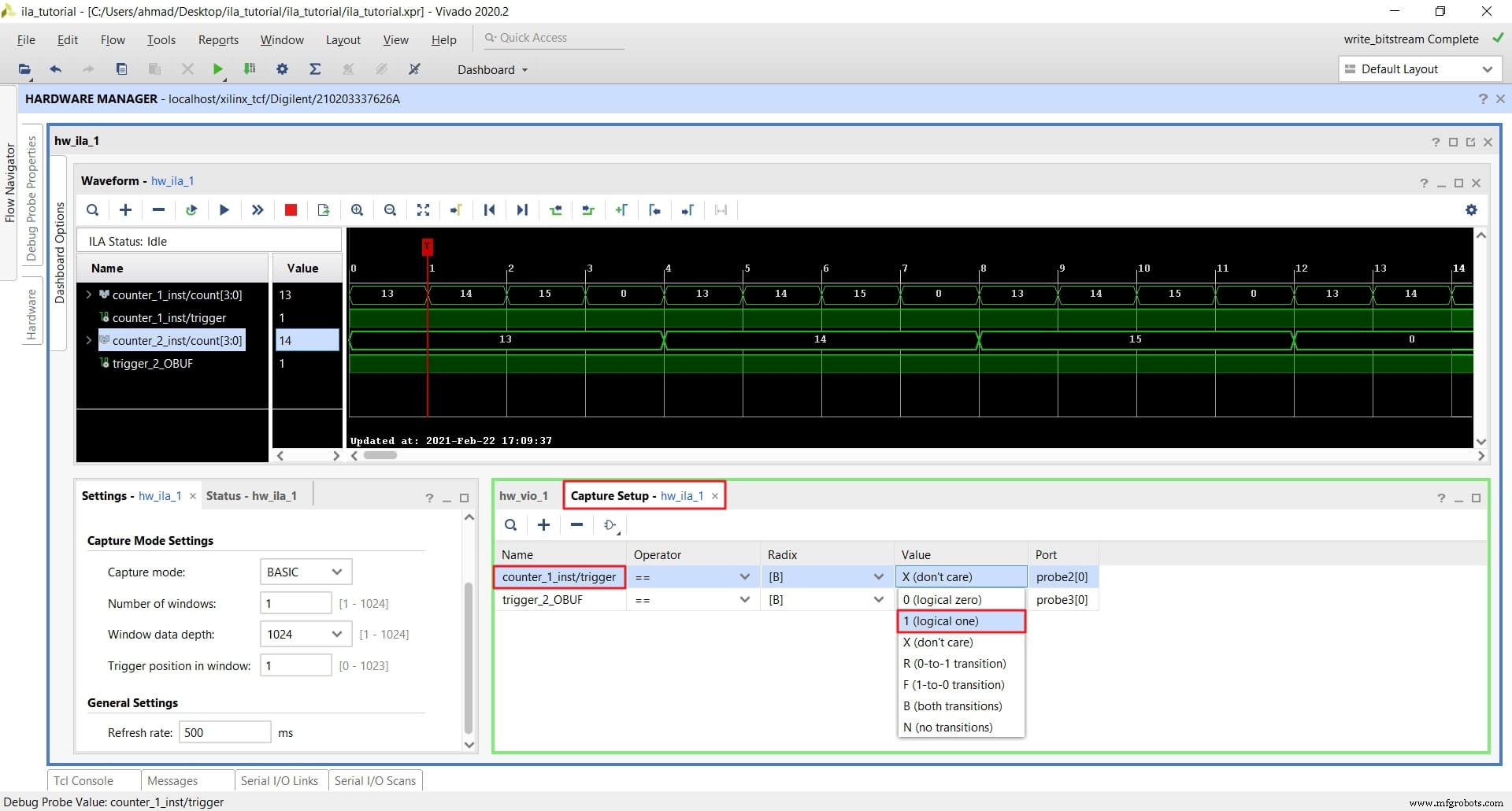

出力ポート trigger の立ち上がりエッジでトリガー (記録を開始) したいとします。 counter_1_inst の .これを行うには、次の手順に従います。

<オール>

また、トリガー位置を 32 に変更します。つまり、トリガー イベントの前に 32 サンプルを記録し、その後に来るサンプルも記録します。

これで、トリガーがセットアップされ、武装する準備が整いました。

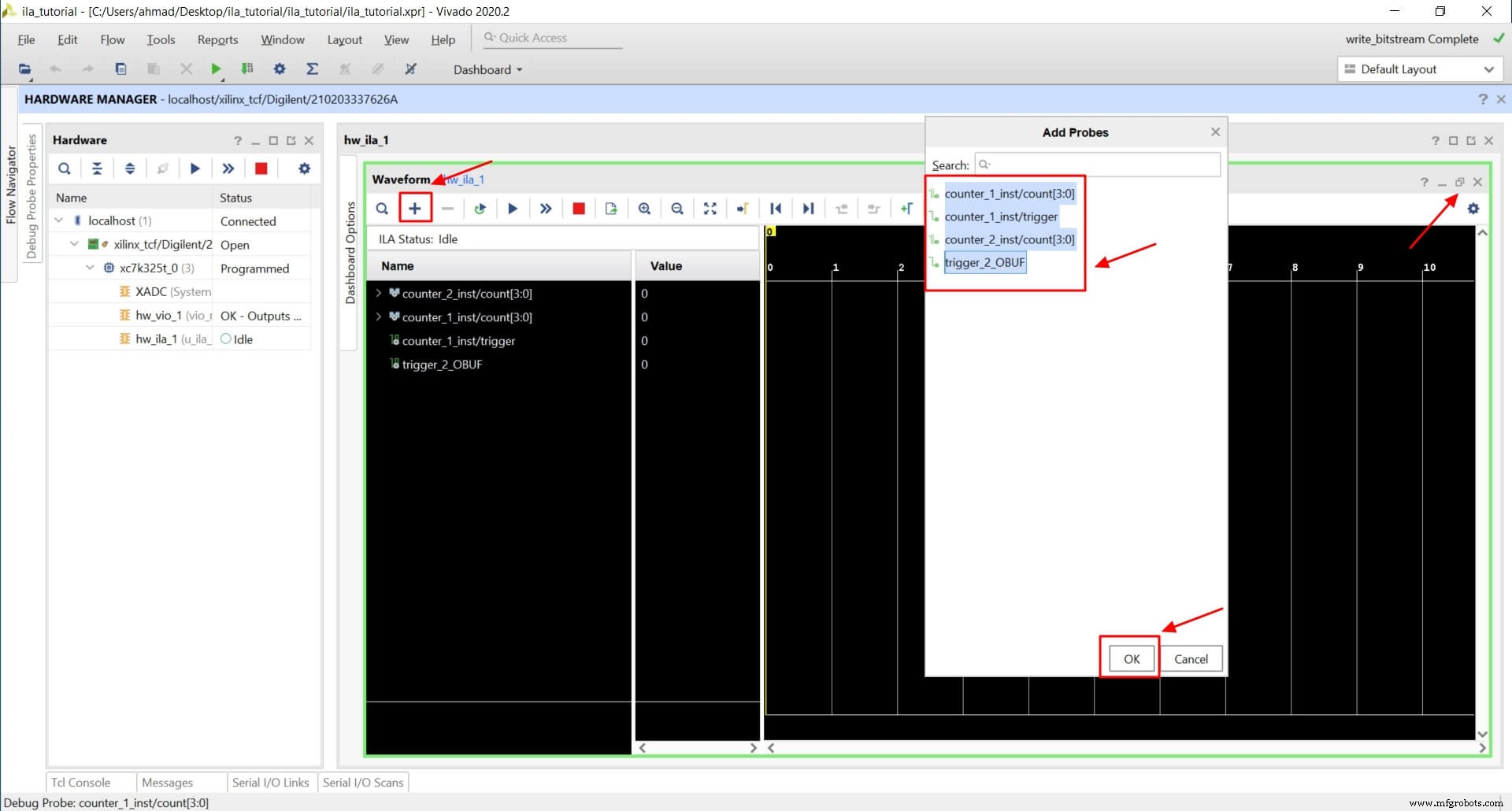

波形ウィンドウに移動します 表示したい信号を追加します。まず、内側のウィンドウを最大化して見やすくしましょう。

次に、不足している信号をプローブに追加する必要があります。 Vivado は通常、割り当てられたすべての信号を自動的に追加しますが、この場合は追加しませんでした。

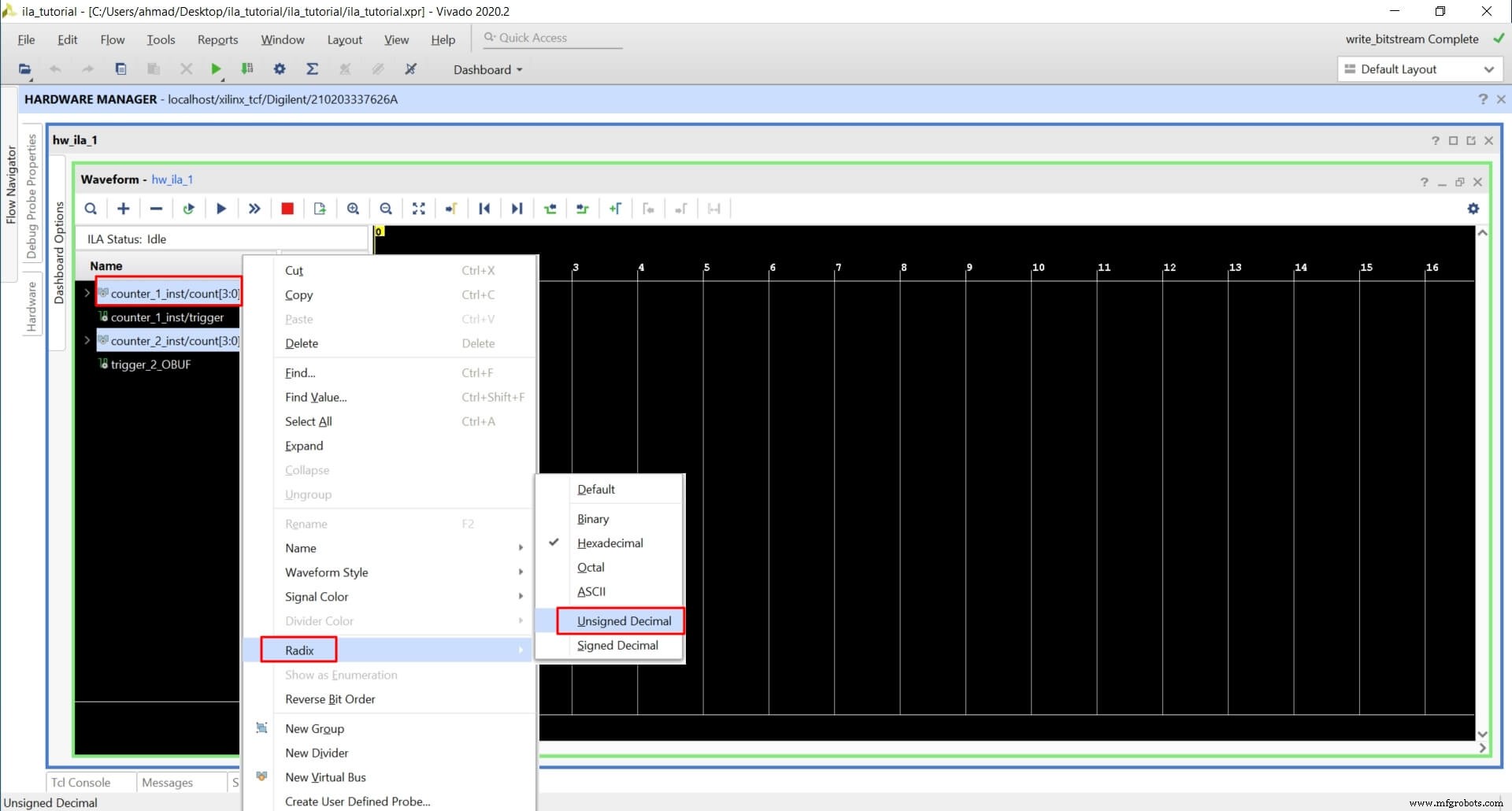

ここで、count の基数を変更します Unsigned の方が追跡しやすいので、信号を送ります。

カウントを右クリック 信号名を選択し、radix を選択します そして無署名 .

ILA と VIO の実行

これで、ILA の構成とカスタマイズが完了し、実行する準備が整いました。

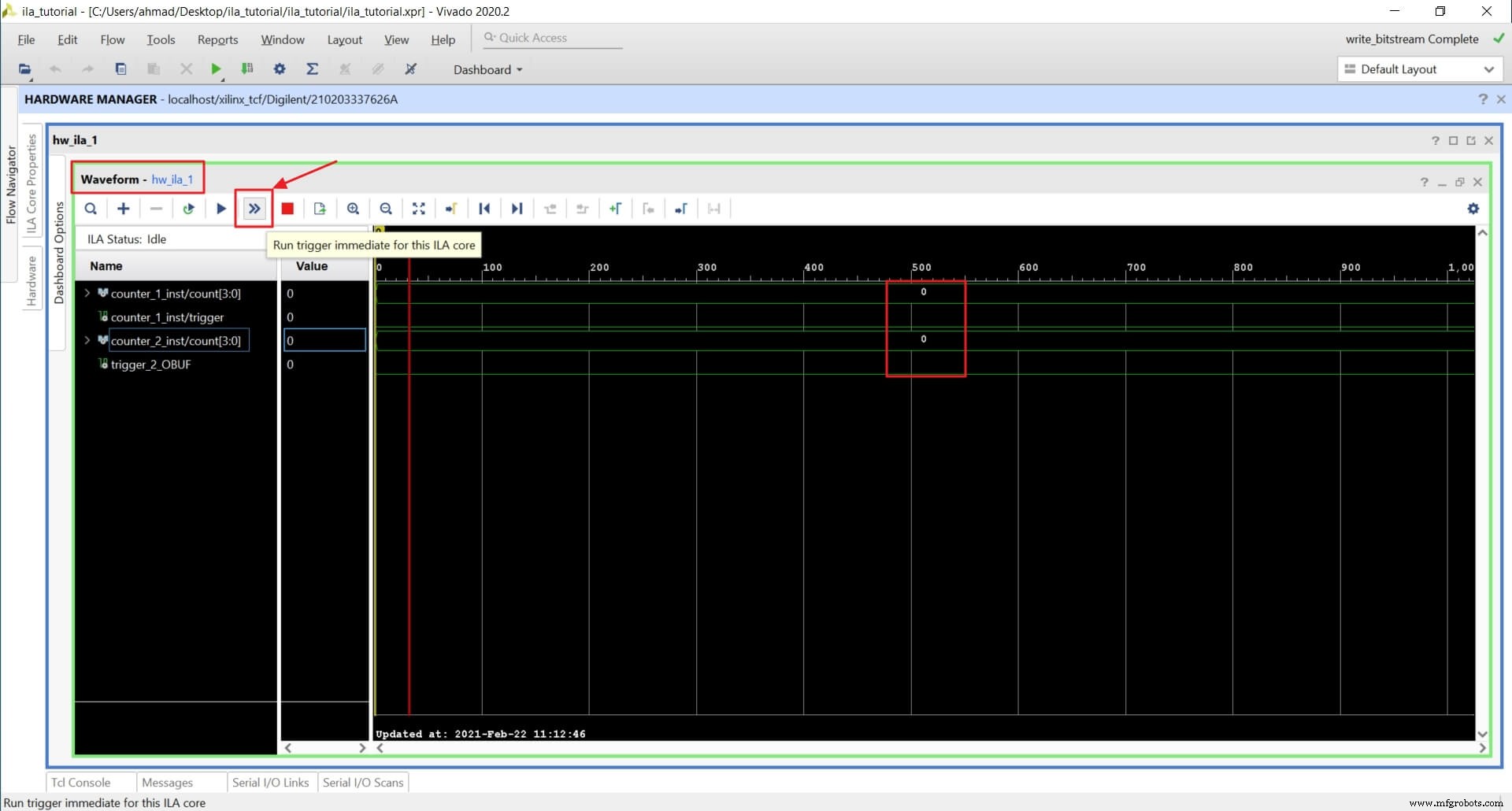

ILA には 2 つの実行モードがあります:即時 とトリガー .

即時モード

即時モードでは、ILA がすぐにトリガーされ、FIFO がいっぱいになるまで直接サンプルの記録が開始されます。

[すぐにトリガーを実行] をクリックします ボタン。

波形ウィンドウに記録されたサンプルが表示されます。両方がカウントすることがわかります シグナルは 0、 両方のトリガー 信号は低い「0」です リセット

トリガーモード

トリガー モードでは、少なくとも 1 つのトリガーの条件を設定し、それを準備する必要があります。 ILA は、アームされたトリガーの条件が真になるのを待ち続け、FIFO がいっぱいになるまで直接サンプルの記録を開始します。

すでにトリガーを追加して、R(0 から 1 への移行) に設定しています。 .

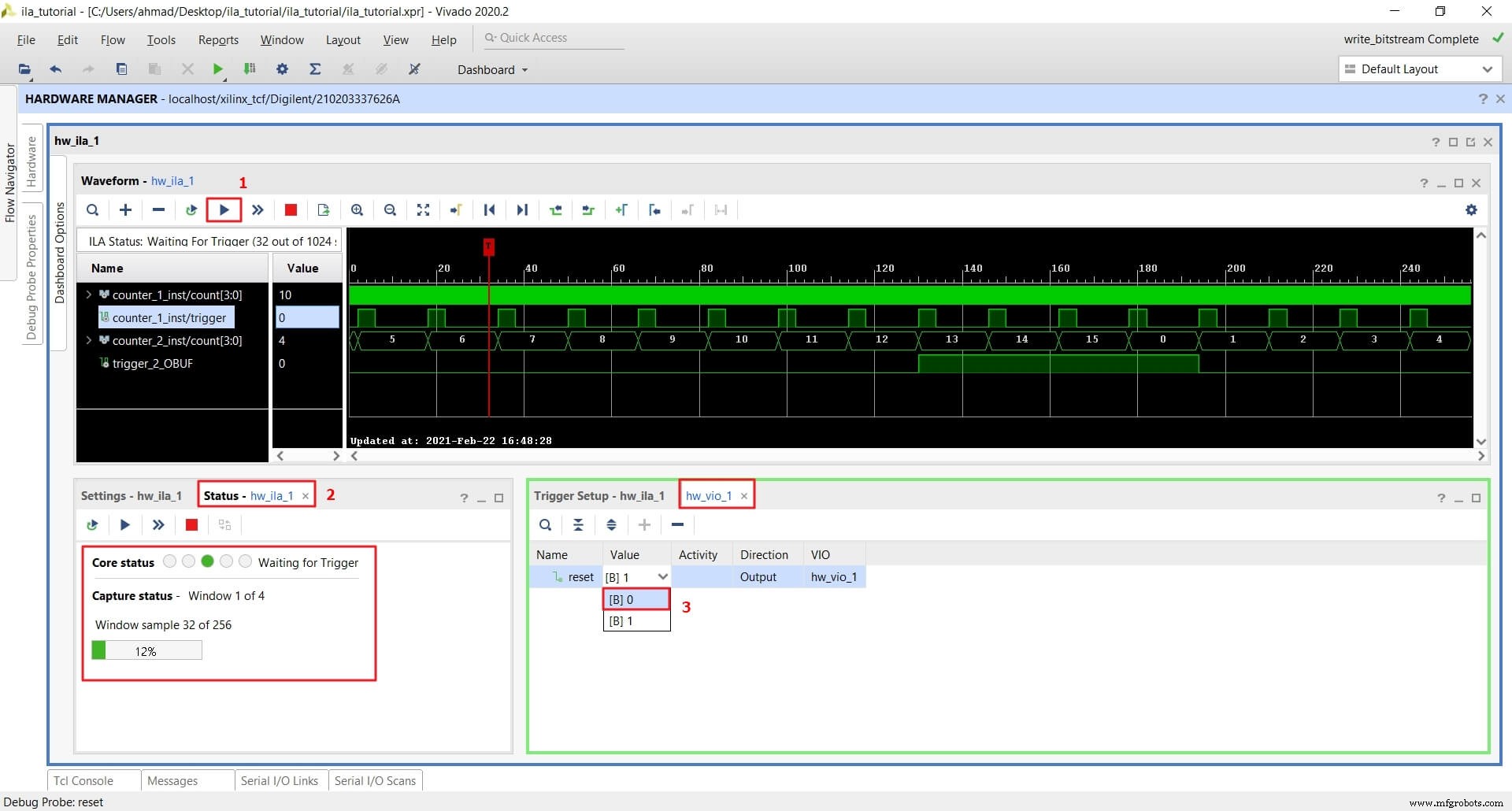

1 つのトリガーで ILA を実行する

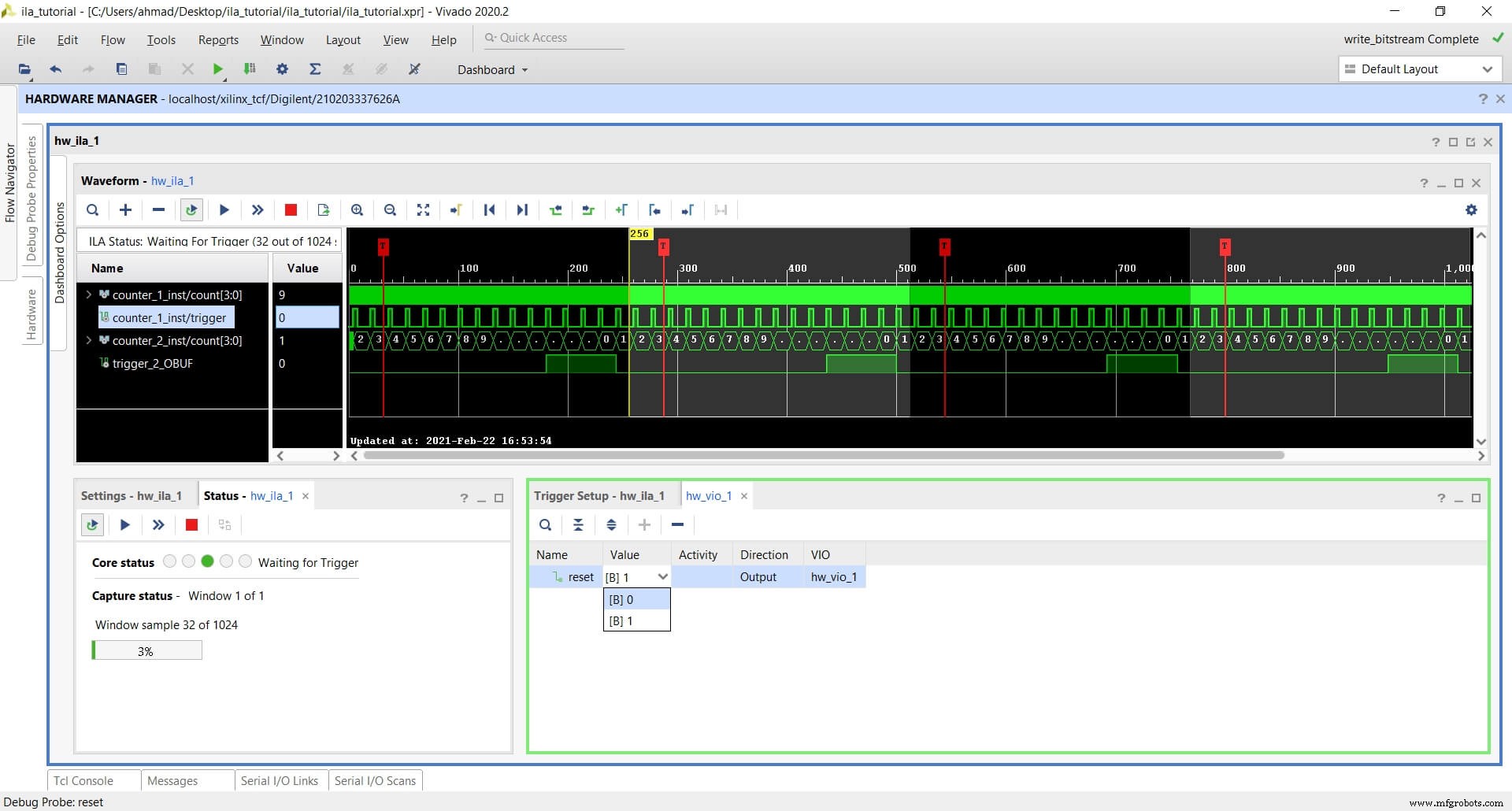

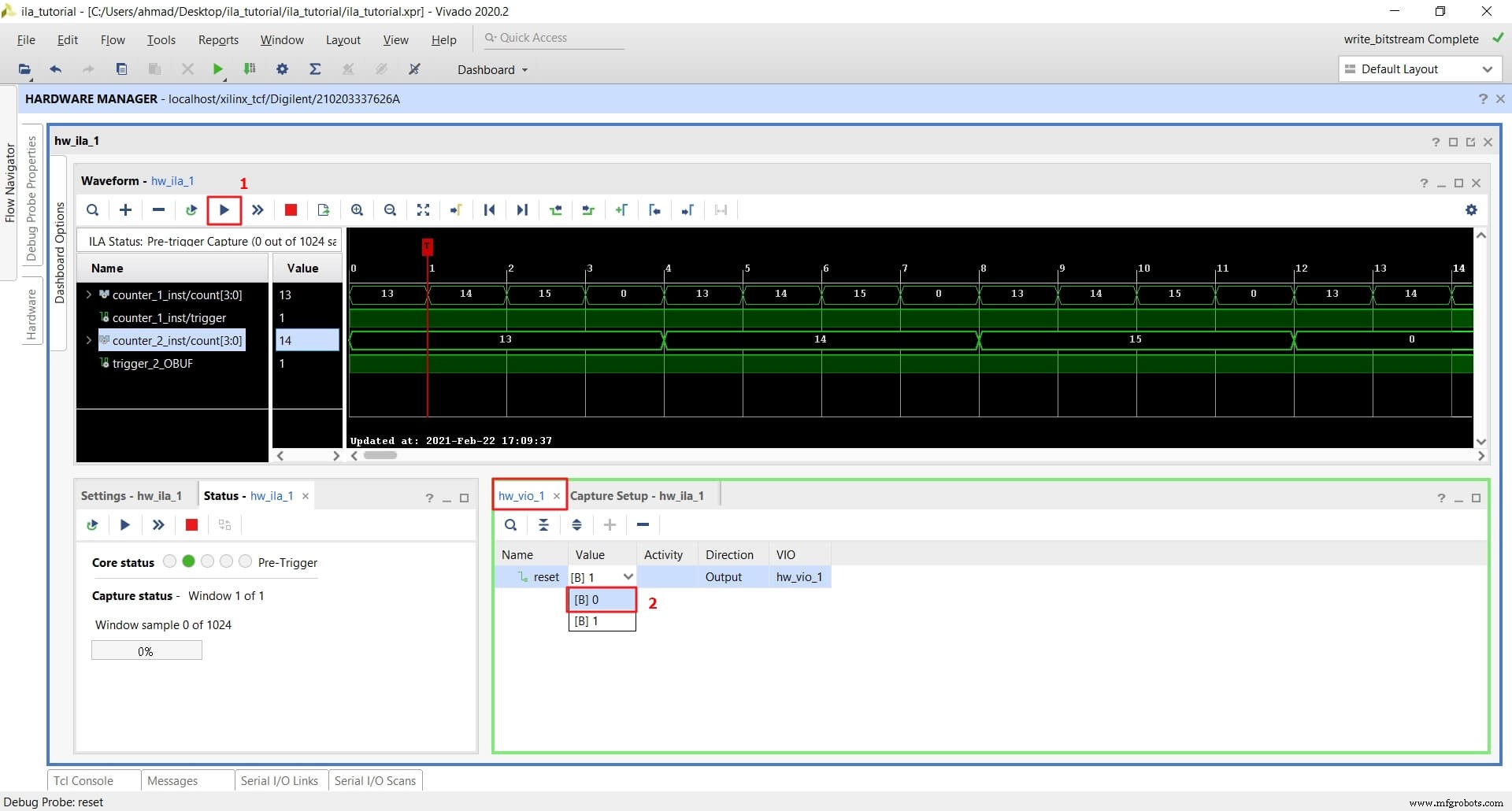

変更 リセット 1 に戻る vio_reset から .

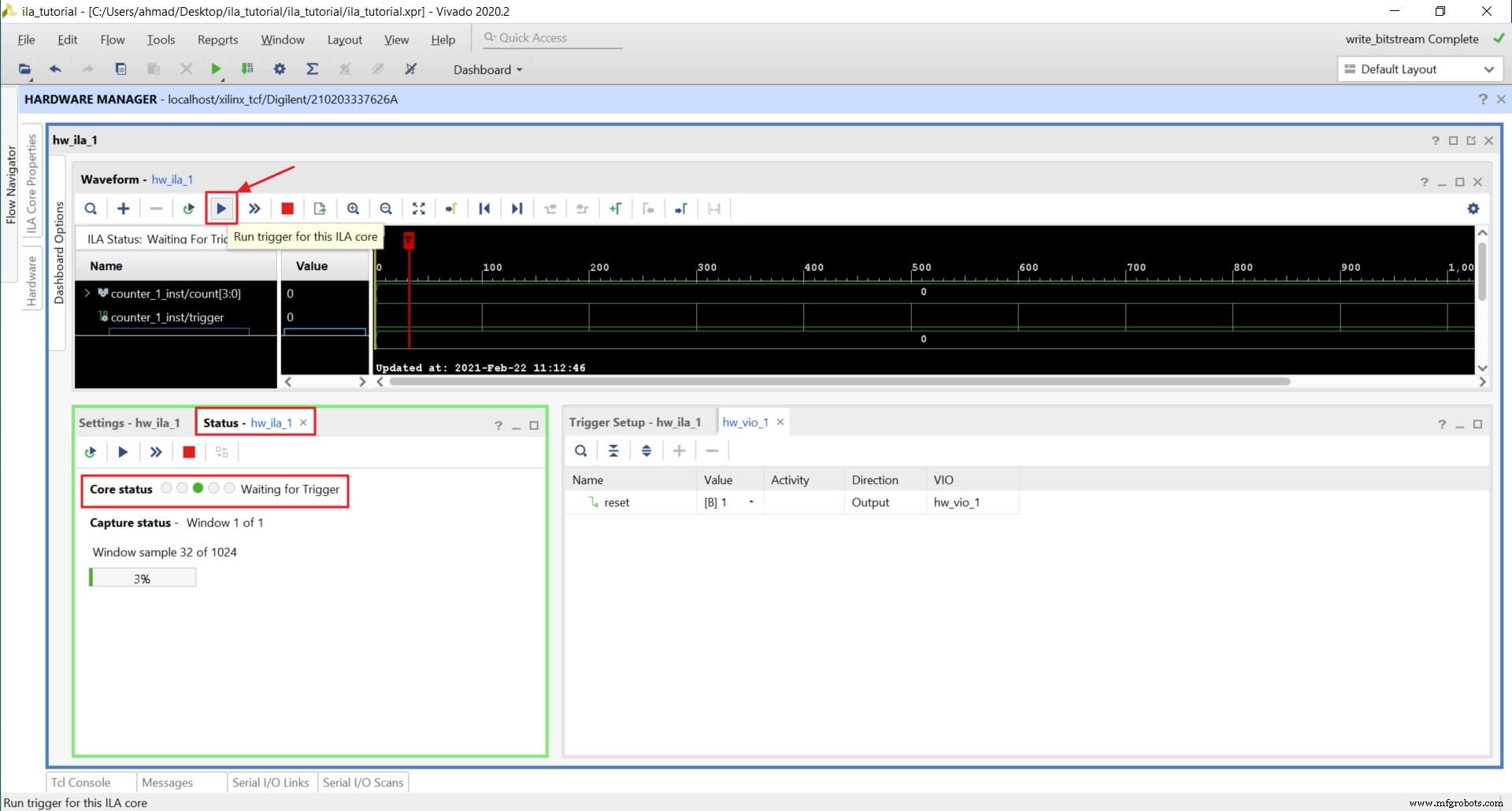

ウィンドウをクリックします Status hw_ila_1 .コア ステータスが Idle であることがわかります トリガーが装備されていないためです。 実行トリガー をクリックします ボタンをクリックすると、トリガーが作動します。

コア ステータスが トリガー待機中 に変わったことがわかります . リセットとして が高く、トリガー信号にアクティビティはありません (ポート trigger counter_1_inst の )、そして ILA が待っています。

リセットを変更しましょう 0まで カウンターが働き始めるように。

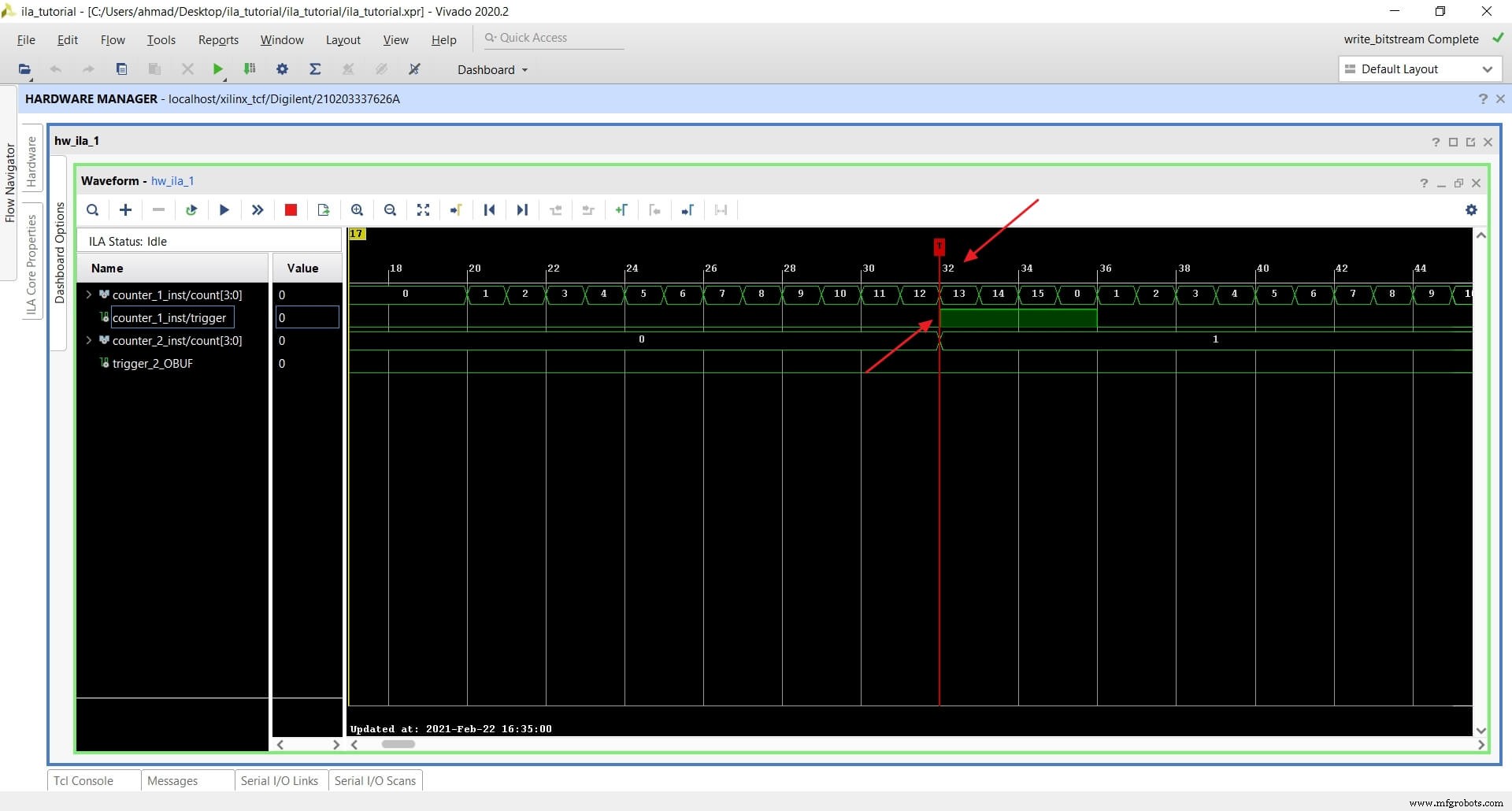

ILA がトリガーされ、サンプルが記録され、コア ステータスが Idle に戻りました。 .

トリガー信号の立ち上がりエッジに赤い縦線 (マーカー) が表示されます (ポート trigger counter_1_inst の )、32 位にあります .また、信号が count であることも確認できます。 正しく動作しており、シグナル counter_1_inst/trigger 12 から 15 の間の 4 クロック サイクルの間ハイになります (出力は 1 クロック サイクル遅れます)。

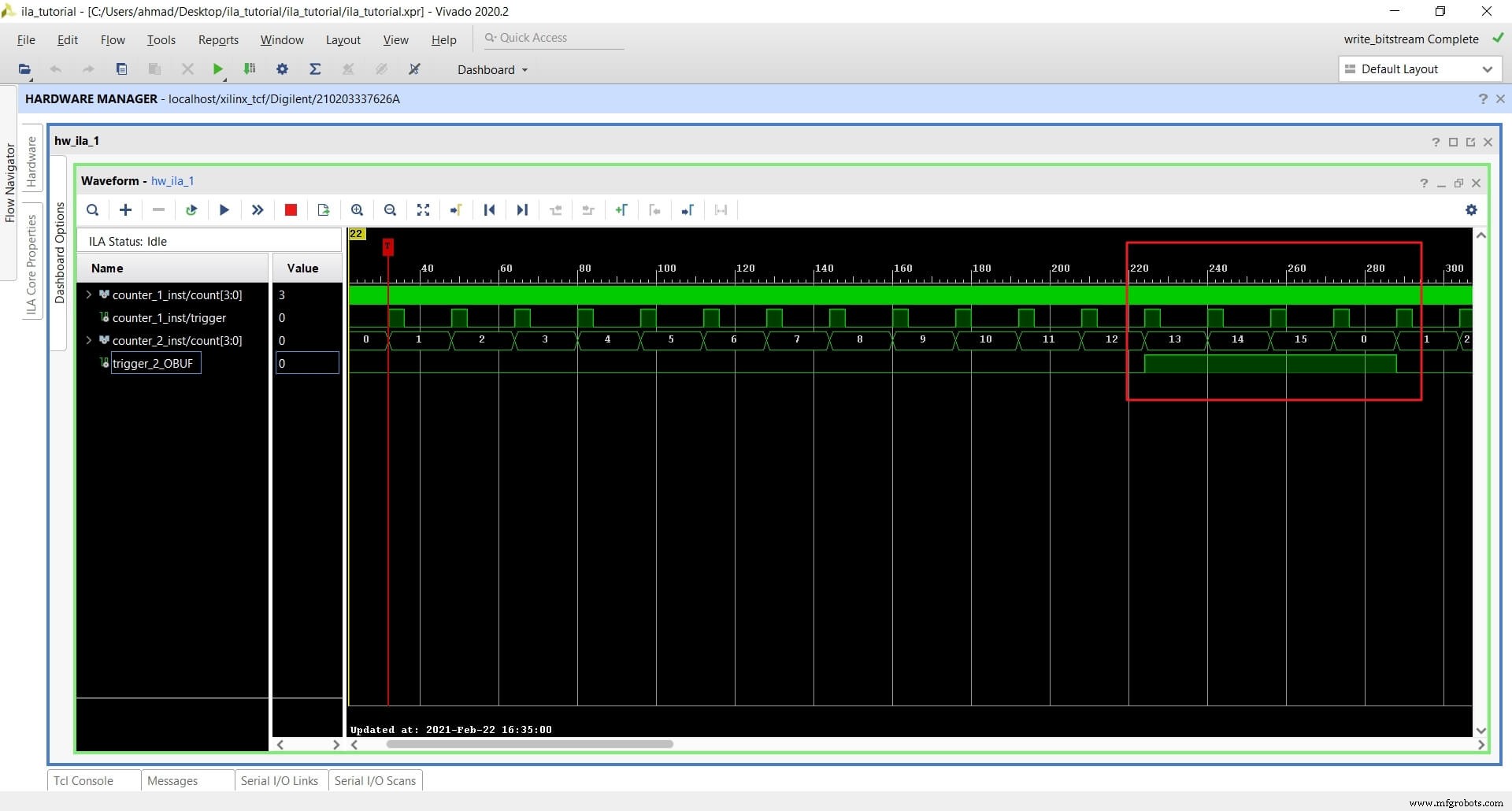

少しズームアウトすると、 count の動作も確認できます とトリガー counter_2_inst のシグナル .

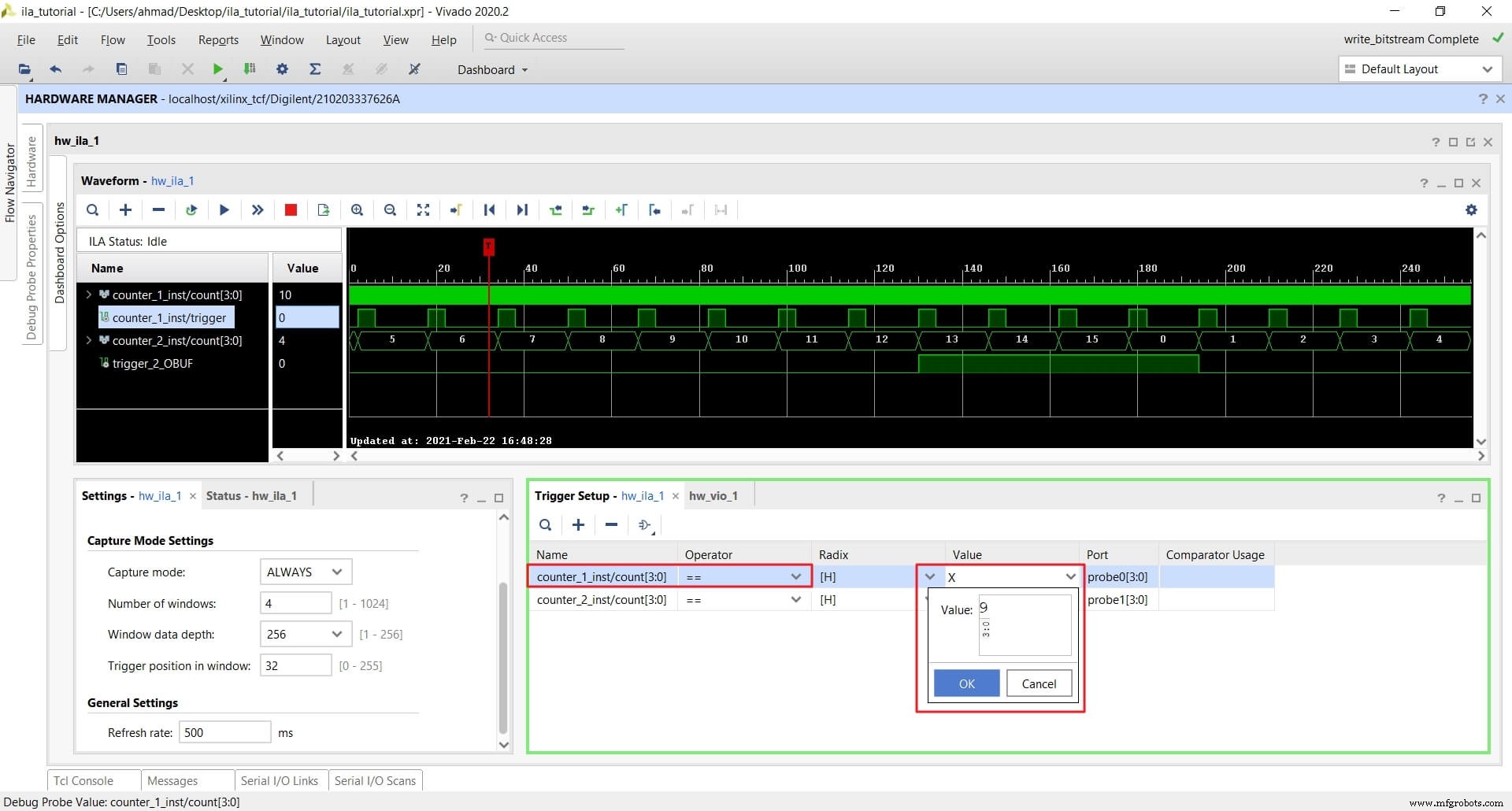

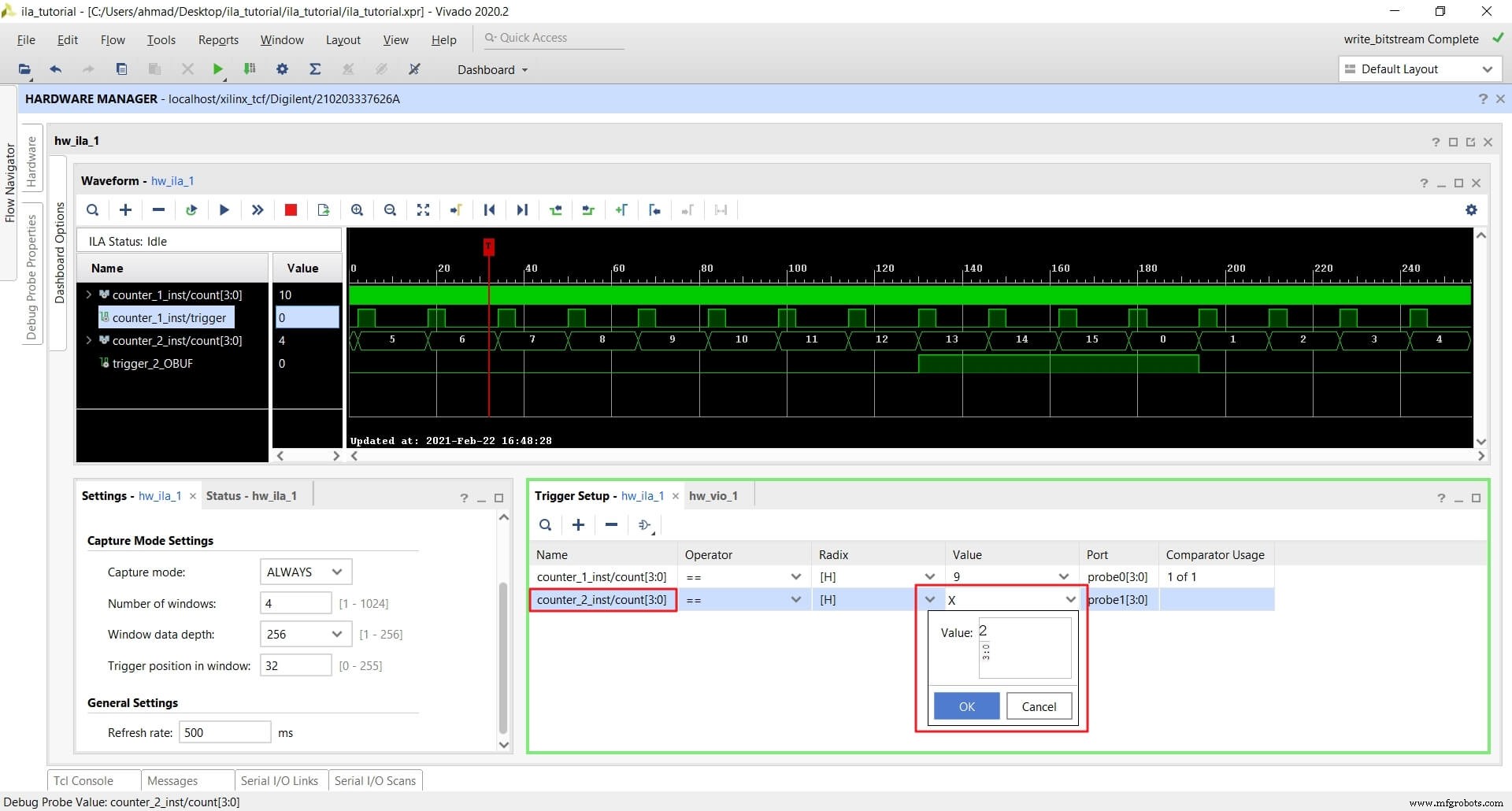

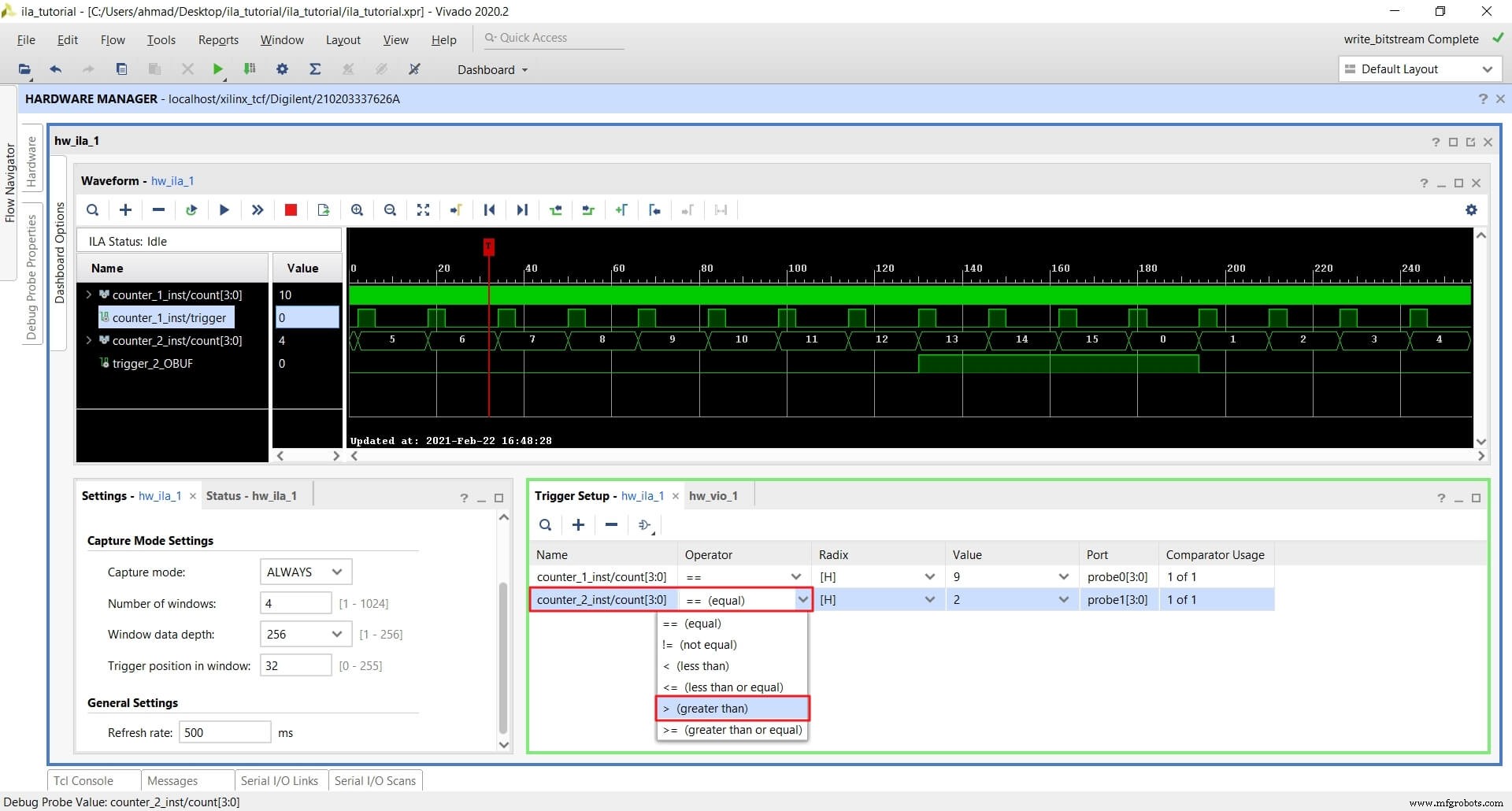

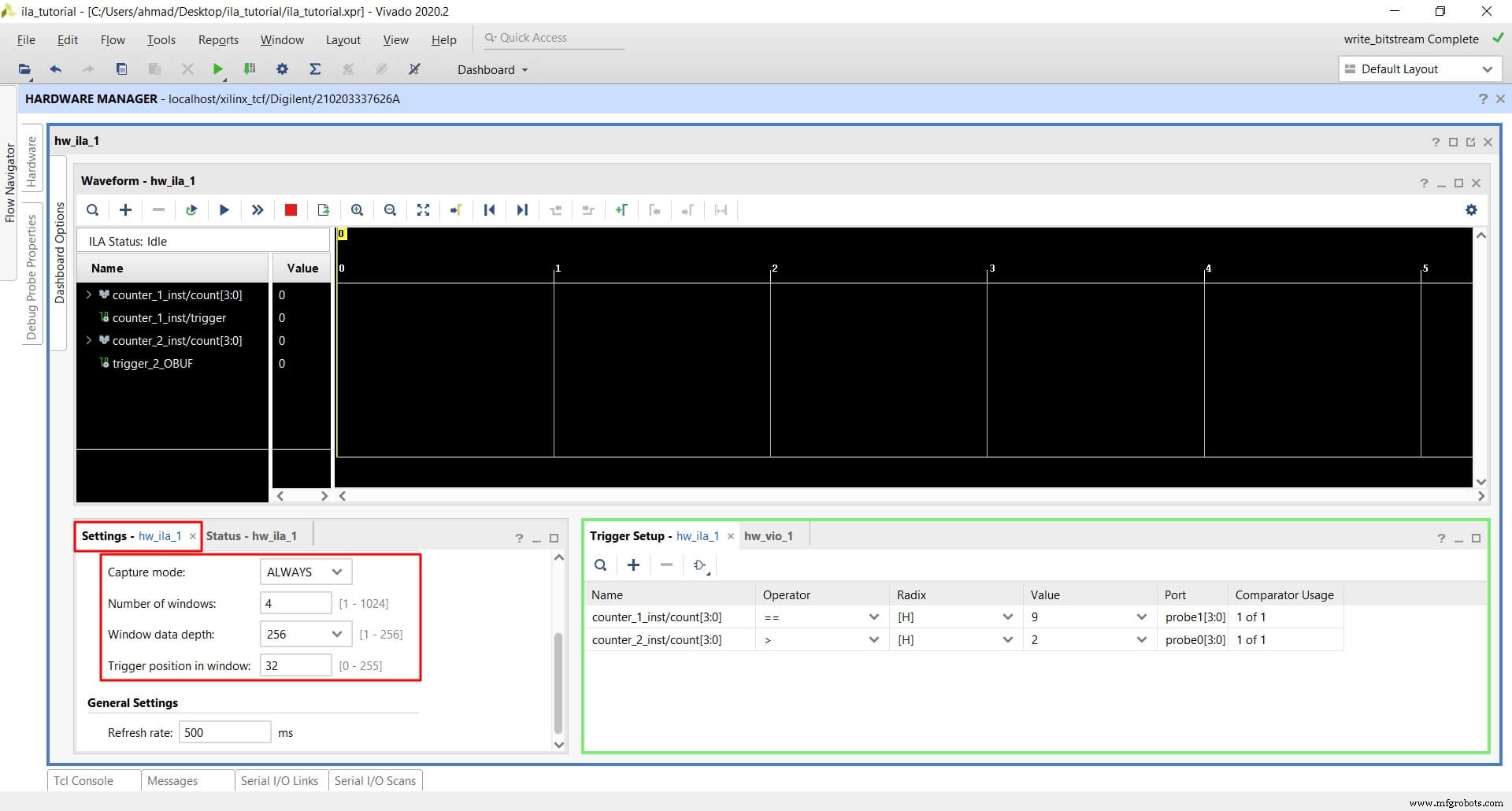

複数のトリガーを使用した ILA の実行

複雑な条件または高度な条件には、トリガーの組み合わせを使用できます。同じ波形でいくつかのバラバラな時間フレームをキャプチャするには、繰り返し起動する複数のトリガーを使用できます。

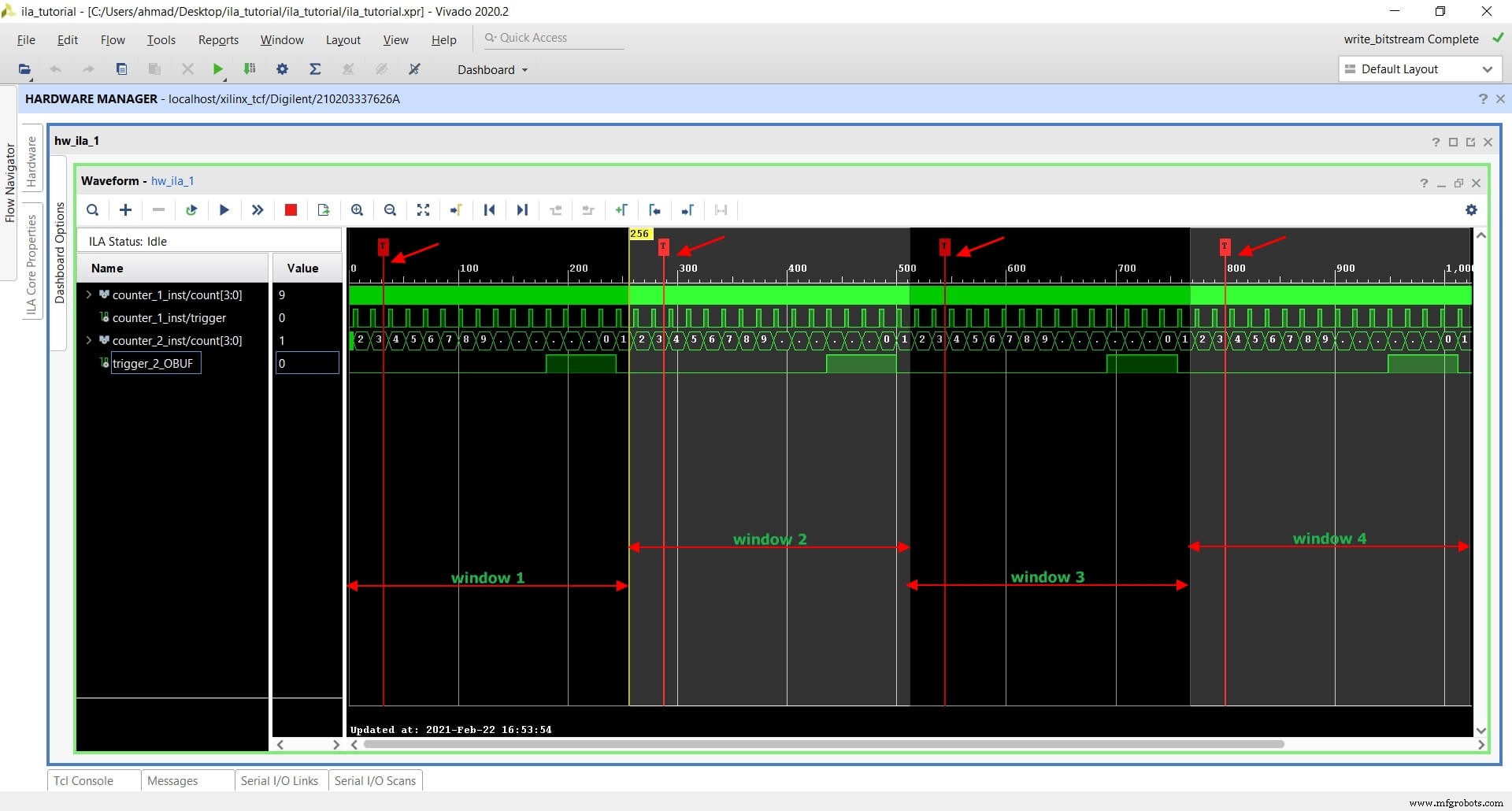

たとえば、カウント counter_1_inst からのシグナル は 9 (count ==9) に等しく、count counter_2_inst からのシグナル 2 より大きい (カウント> 2)。これを行い、FIFO を 4 つの時間枠に分割するには、次の手順に従います。

<オール>

変更 リセット 0 に戻る vio_reset から .

Maximize the waveform window. We see now that we have four windows and a trigger associated with each window. Notice that these windows are independent and not continuous.

The ILA waits for the trigger event to happen, and when it does, the ILA uses the first window to record 256 samples. It then immediately waits for the next trigger until all the windows are full.

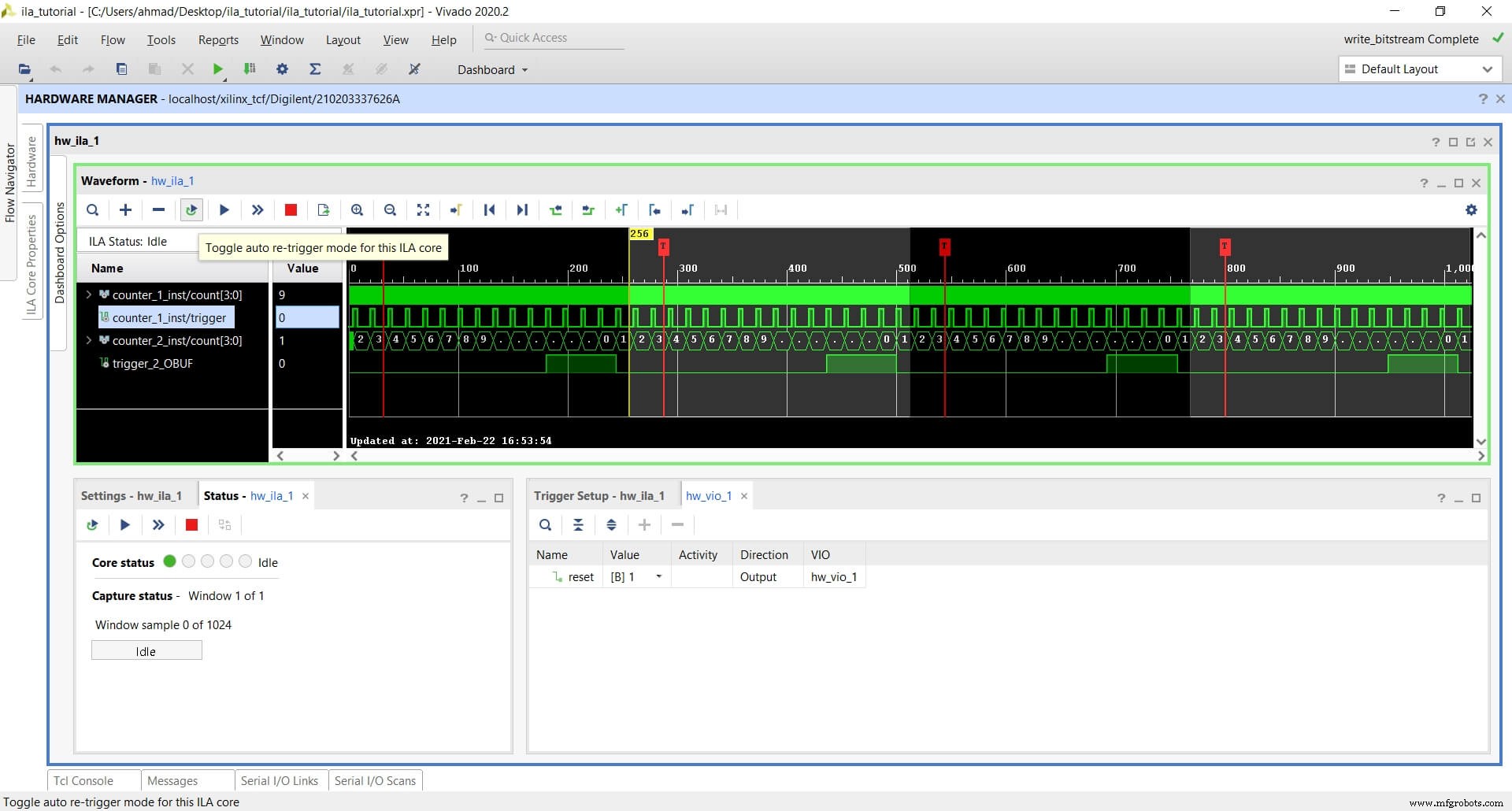

Running ILA with Auto re-trigger mode

ILA has a nice feature called Auto re-trigger that will automatically arm the trigger after it gets triggered. It is useful when monitoring events that occur seldom and you want to run a test overnight. Or you can use it when the trigger happens so often and fast that you cannot arm the trigger manually to capture the samples repeatedly.

Let us assume that the output port trigger of counter_2_inst gets asserted every 3 hours, and you want to record the data each time it happens. To use the Auto trigger, follow these steps:

<オール>

We can see now that the waveform window is getting refreshed and updated as the trigger happen. It is fast, but the behavior is noticeable.

Click on Stop trigger and toggle Auto re-trigger .

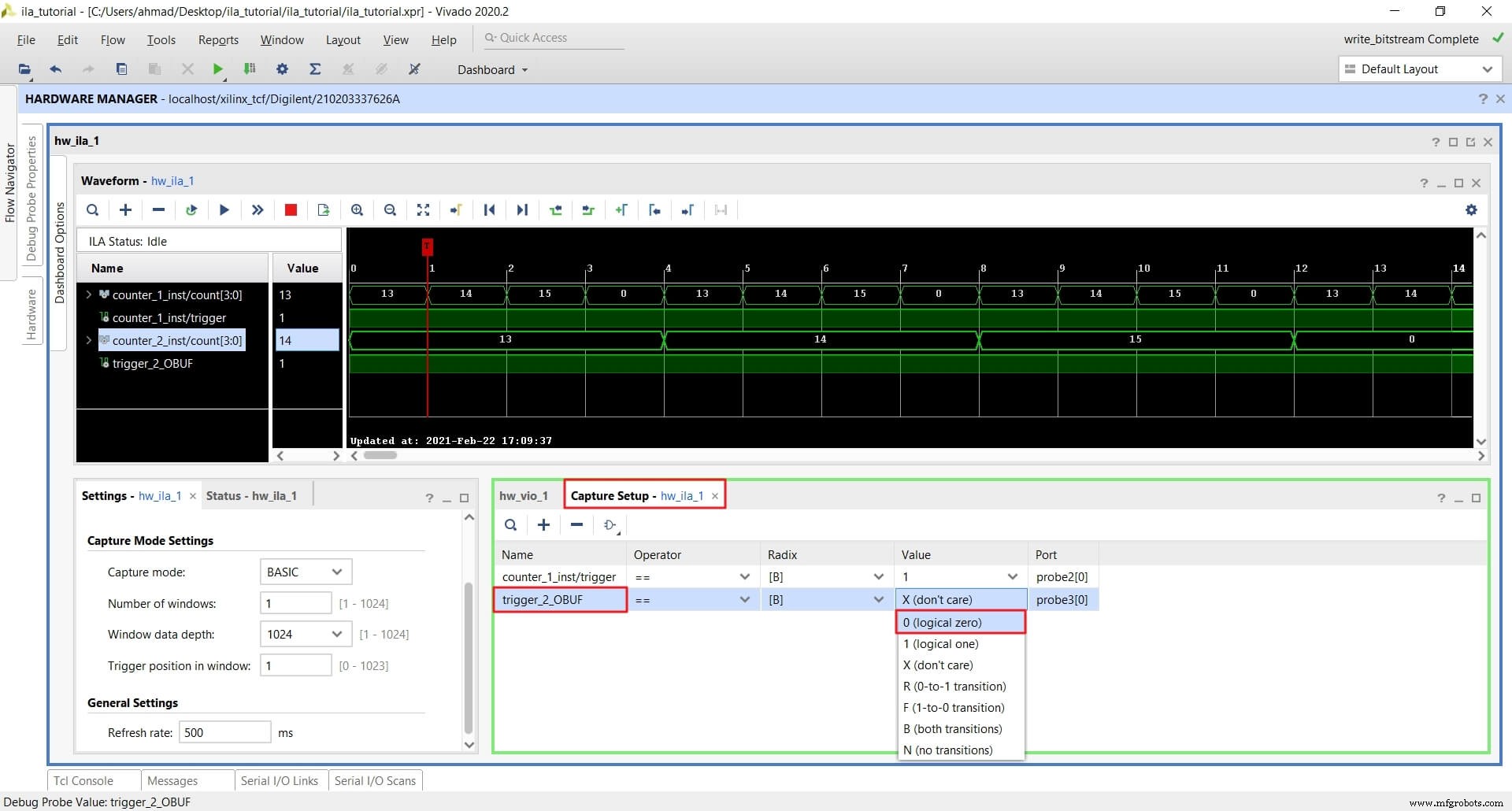

Running ILA with Capture mode

Another feature of ILA is the Capture mode . In some cases, you are not interested in recording all the data but rather capture a specific sample. Capture mode helps you filter out data and record only the samples you are interested in.

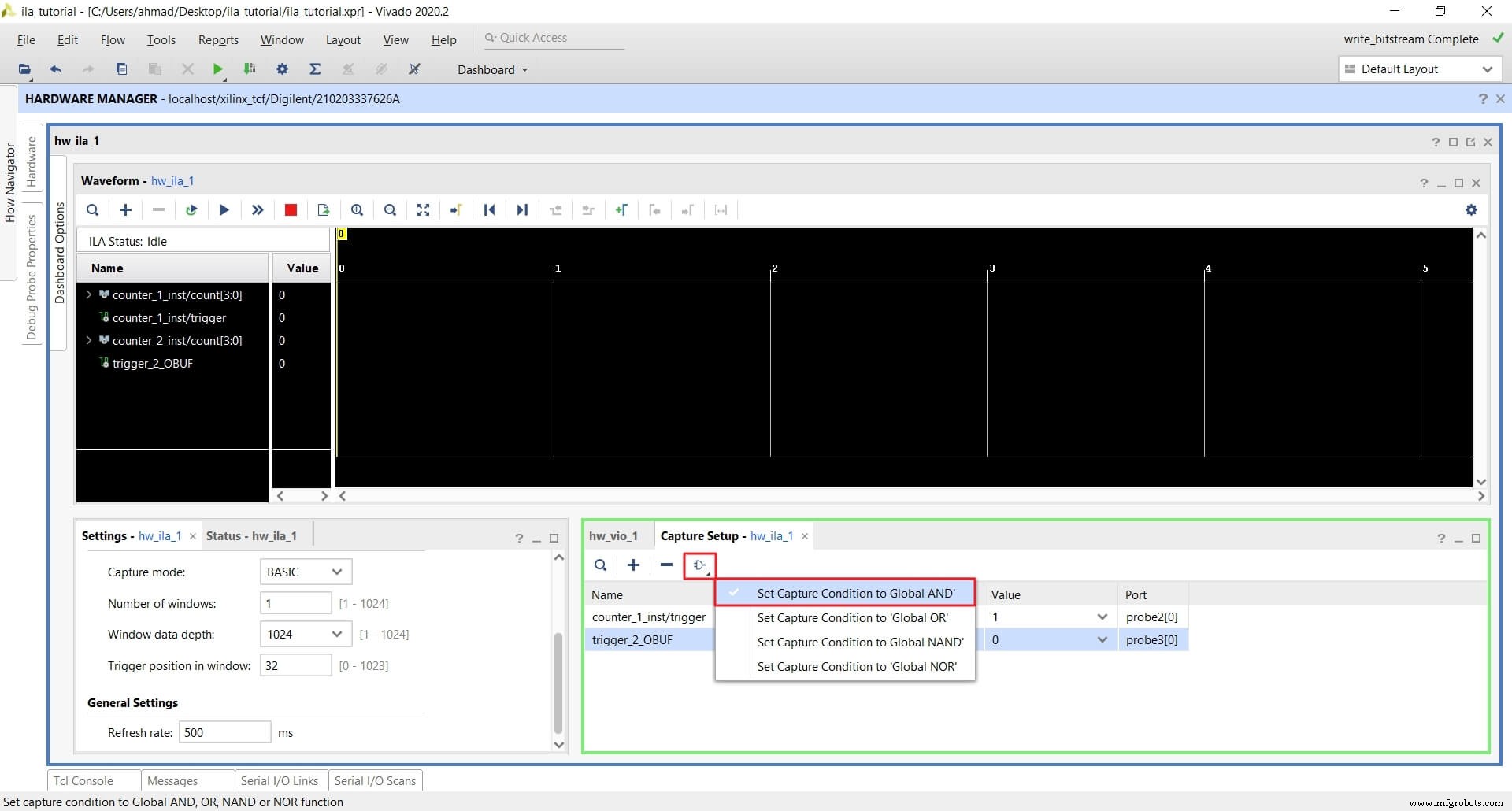

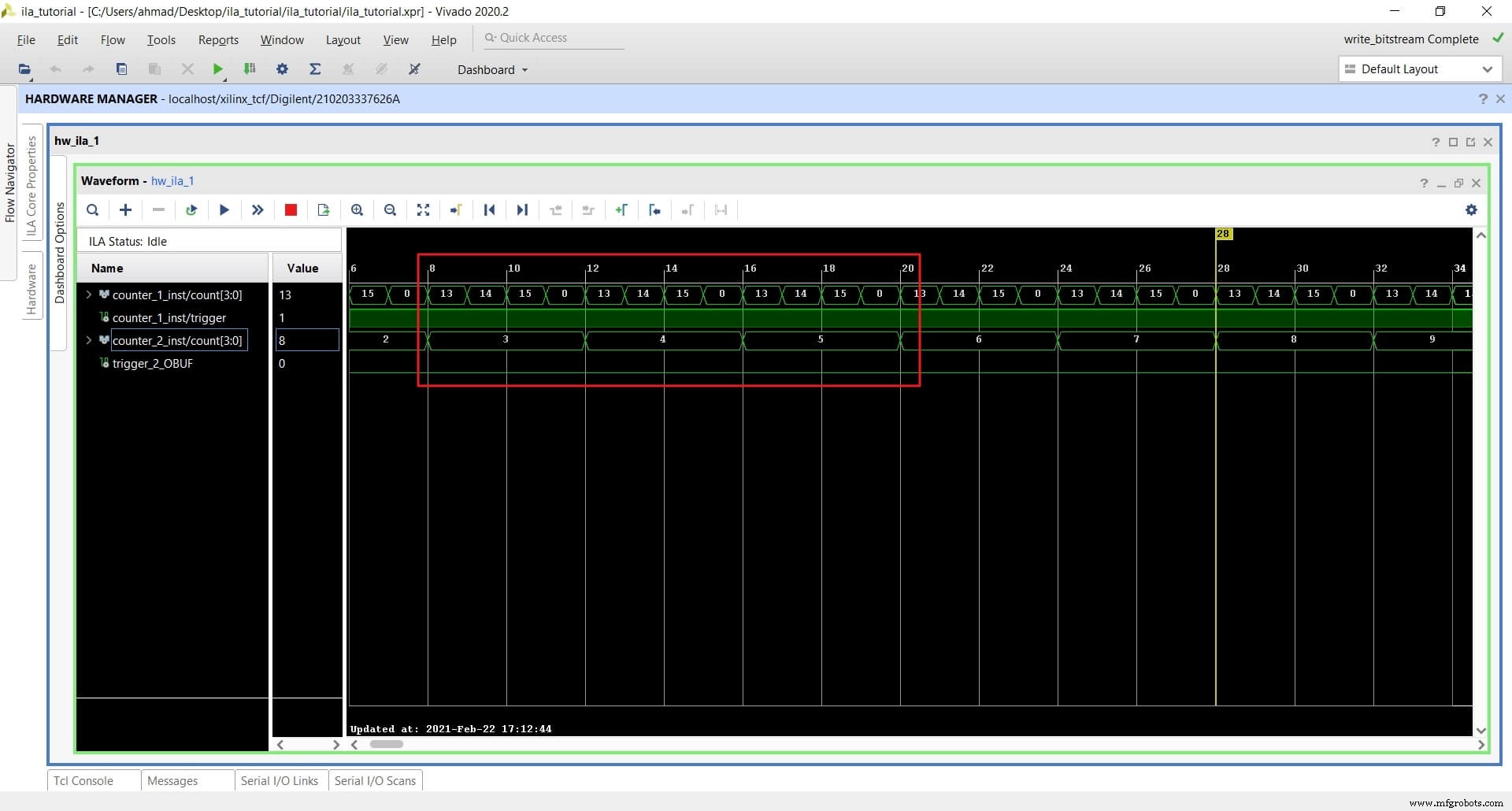

Let’s say we are only interested in sampling when the output port trigger of counter_1_inst is ‘1’ AND the output port trigger of counter_2_inst is ‘0’.

To use Capture mode to achieve this, follow these steps:

<オール>

As we can see from the image below, the waveform has only recorded data when counter_1_inst’s count signal is 13, 14, 15, or 0. Any other counts are filtered out because counter_1_inst/trigger is high on these counts only.

Conclusion

In this tutorial, we learned about ILA and VIO and different use-cases for them. ILA and VIO are excellent options for on-chip debugging. They are free, easy to use, flexible, scalable, and simple yet offer advanced features. The use of multiple triggers and Capture mode helps you achieve a complex debugging scheme.

VHDL