重要なマルチコアベースの組み込みシステムでのソフトウェアタイミング動作の保証

安全にどこかに行くには、良いブレーキ、作動するテールライト、そしてハンドルの後ろに優れた反射神経を持つ人以上のものが必要です。ますます、あなたの車を道路に、そしてあなたの飛行機を空中に保つコンポーネントは、人間だけでなく、単に機械的でさえあります。これらは、複雑な異種マルチコアプロセッサで実行され、飛行管理システムからパワーステアリングまですべてを制御し、マイクロ秒単位で測定される厳密なタイミング期限まで実行する高度な組み込みソフトウェアです。

ここに課題があります。マルチコアシステムでのソフトウェアのタイミング動作は、そのシステムで実行されているソフトウェアとその入力だけでなく、他のコアで実行されている他のソフトウェアの影響も受けます。

重要な組み込みシステムを開発するには、莫大な労力と投資(数百万ユーロ/ドルと数年のエンジニアリング努力)が必要です。安全性は、ソフトウェア開発プロセスの初期段階から、アーキテクチャと設計の中心にある必要があります。特に、システム設計者は、ソフトウェアが安全な時間枠内で実行できるように、ソフトウェアのタイミング動作を理解する必要があります。

マルチコアタイミング分析(MTA)パズルの解決

マルチコアプロセッサの優れたコンピューティング能力は、(理論的には)組み込みシステムをより強力かつ効率的にするはずですが、1つのコアで実行されるソフトウェアは、他のコアで実行されるソフトウェアの実行を遅くする可能性があります。この状況では、他のコアで実行されているタスクと共有されるバス、メモリ、キャッシュ、デバイス、FPGA、GPUなどの共有リソースの競合によって引き起こされる干渉により、ソフトウェアの実行に時間がかかる場合があります。

この干渉の影響をどのように定量化しますか?マルチコアプラットフォームで実行している場合、セーフティクリティカルなソフトウェアが常にタイミング期限内に実行できるという具体的な証拠をどのように分析、テスト、提供しますか?

バルセロナスーパーコンピューティングセンター(BSC)、Rapita Systems Ltd(RPT)、Raytheon Technologies(RTRC)、およびMarelli Europe(MAR)の専門家は、これらの質問に対する回答を長年にわたって調査してきました。 BSCとRapitaは、航空宇宙および自動車産業全体にまもなく展開されるソリューションを開発してきました。特殊なツールと自動化を、要件に基づいた安全性に重点を置いた方法論と組み合わせることで、パズルを解くことができました。

この作業は、欧州委員会が資金提供し、2019年12月に開始された学際的な研究開発プロジェクトであるMASTECSプロジェクトの基礎を形成しました。MASTECSプロジェクトは、技術を成熟させ、航空電子工学および自動車システムの認証への使用をサポートします。 MASTECSプロジェクトの重要な部分は、RTRCとMARによって展開されたケーススタディを通じて、2つの業界でのアプローチのデモンストレーションを提供することです。

最先端のツール

タイミング分析をサポートする市販のツールは、単純な(シングルコア)電子機器には効果的ですが、新しいマルチコア固有の認証要件と推奨事項を満たすように拡張することはできません。

- 静的タイミング分析ソリューション[1]は複雑な壁に直面しており、ますます複雑になるハードウェアを効果的にモデル化することも、非常に複雑なソフトウェア機能の構造的および構文的特性を効率的に処理することもできません。

- 測定ベースのソリューションは、シングルコア分析市場で十分な浸透率に達しています(Rapita SystemsのRVSツールセットは最も成功しているものの1つです)。ただし、そのようなツールは、マルチコアの導入によってもたらされる課題を完全に維持することはできません。それらは通常、統合された機能テスト戦略によって決定される測定シナリオに焦点を当てていますが、必要な裏付けとなる証拠と適切なレベルのトレーサビリティを備えたマルチコアで実行されるタスクの信頼できるタイミング境界を導き出すのに役立つハードウェアの専門知識に基づく方法論を欠いています。

私たちの知る限り、MASTECSで成熟しているものを除いて、適用可能な安全基準と新たな認証要件に重点を置いて、マルチコアプラットフォーム上のソフトウェアのタイミングを分析できる商用ツールは市場に出回っていません。

>実際の干渉分析と制御

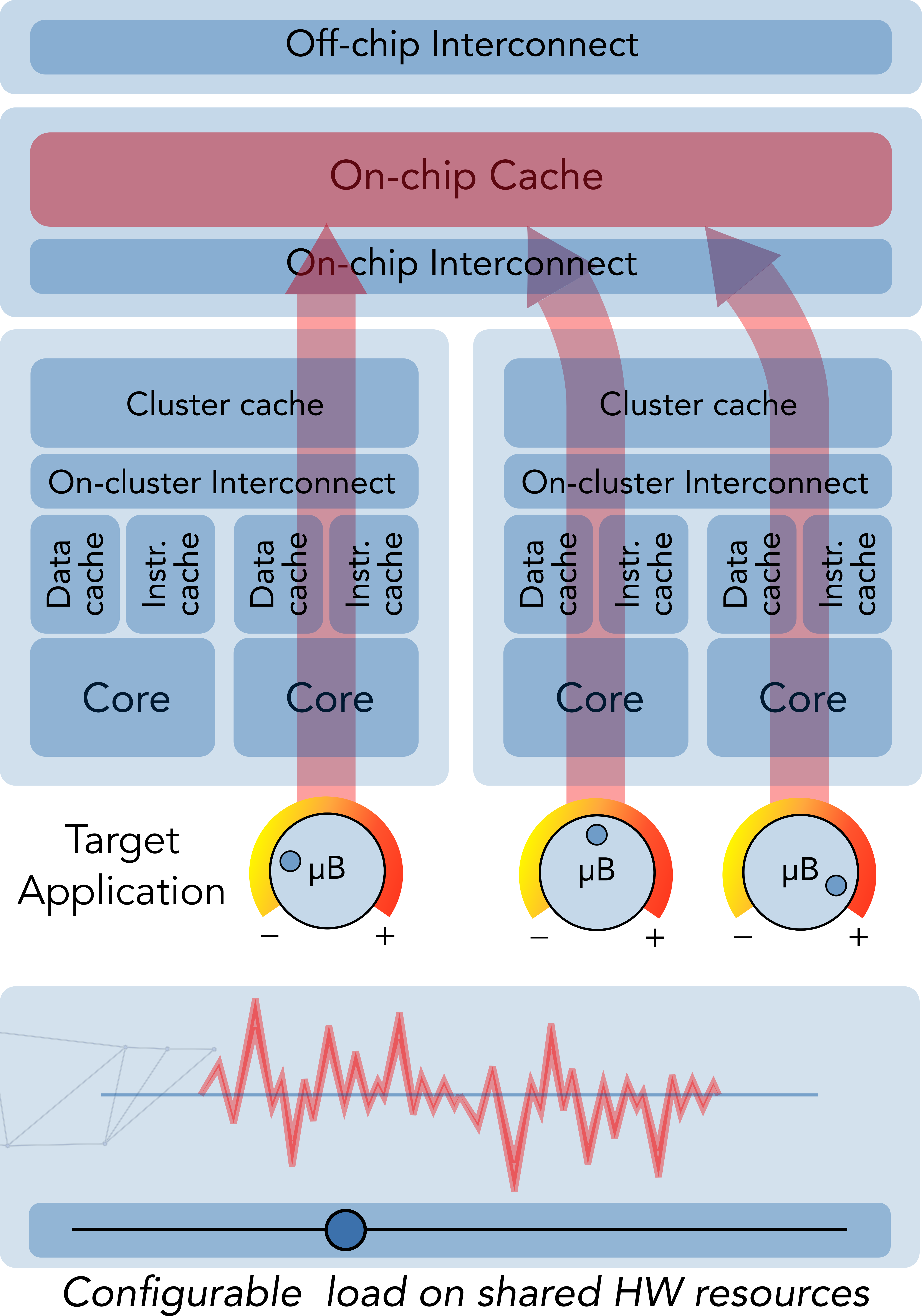

干渉を理解するための鍵は、ハードウェアとソフトウェアの専門家を使用してマルチコアのタイミング動作に関する証拠を生成する、構造化されたテスト方法です。 BSCの特殊なテクノロジー(マルチコアマイクロベンチマークテクノロジーまたはMμBTとして知られ、RapitaによってRapiDaemonsとして商品化されています)により、システム設計者は、マルチコアベースのアプリケーションでの干渉の影響を分析および定量化できます。マルチコアプロセッサ。

MuBTの中心にあるマイクロベンチマークは、ハードウェアとソフトウェアの間の最も低いインターフェイスで動作して特定の共有リソースに負荷をかける、巧妙に作成されたコードです。マイクロベンチマークは、ソフトウェアのタイミングに対する干渉チャネルの影響を明らかにします。そのために、マイクロベンチマークを展開して、特定のアプリケーションに構成可能で定量化可能なプレッシャーをかけることができます。マイクロベンチマークは、特定のハードウェアリソースに予想される影響を与える単一の明確に定義された動作を示すように特別に設計されており、他の干渉チャネルでの競合の発生を可能な限り防ぎます。マイクロベンチマークの主な機能は次のとおりです。

- 特定の共有リソースに定量化可能なプレッシャーをかけます。

- それらの動作は、イベントモニターを介して確認できます。

- 競合をマスターするために実施した緩和アクションが効果的かどうかなど、特定のタイミング関連の要件をキャプチャします。

クリックすると拡大画像が表示されます

図1:干渉分析でのマイクロベンチマークの使用。 (出典:著者)

さまざまなマイクロベンチマークが開発され、特定の役割を果たしています。たとえば、必要なレベルの干渉を一致させる、リソースへの干渉を最大化する、または単に競合(「犠牲者」)に非常に敏感であるなどです。

干渉の影響を分析する際に、MμBTの使用は、タスクが受ける可能性のある競合遅延の早期推定を提供するタスク競合モデル(TCM)でサポートされます。 Rapitaによって開発されたソフトウェア自動化およびテストツールRapiTestおよびRapiTimeは、テストを記述し、組み込みターゲットで実行するために使用されます。

設計方法

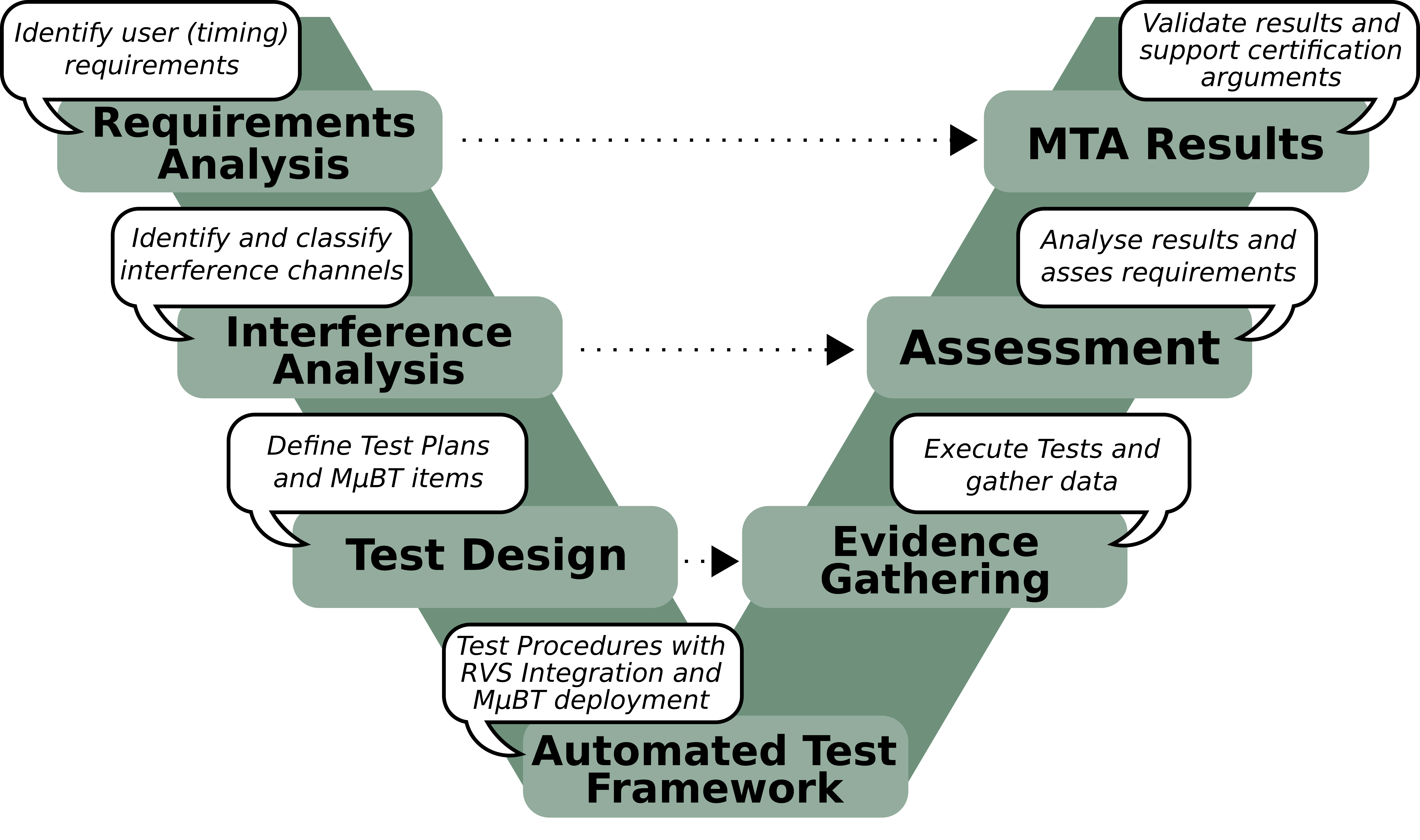

標準のソフトウェア「V」開発プロセス(図2)に沿った7段階のテスト設計プロセスに従うことで、エンジニアは干渉の影響をより完全に理解できます。

- マルチコアプロセッサの重要な構成設定、干渉チャネル、およびイベントモニターの分析。 ハードウェアの専門家は、重要な構成設定を特定して、緩和策とともに干渉チャネルも特定されるフレームワークを設定するのに役立ちます。ハードウェアイベントモニターの識別は、以降のすべての手順を検証する手段を提供するのにも役立ちます。

- タイミング要件を特定します。 エンドユーザーがシステムの特定のニーズ、タイミング要件、リスク、および安全性の問題を特定できるようにします。たとえば、干渉を最小限に抑えるために、ハードウェア分離アプローチのパフォーマンスを確認します。

- テストケースの設計。 特定のテストケース(テストの説明)を作成して、干渉チャネル分析で証拠を提供するために必要となるMμBT項目の定義を含む、ユーザー要件をサポートする一連の仮説を検証します。これには、単独での実行(干渉なし)、アプリケーションの実行時間を評価するためのマイクロベンチマークに対する実行、およびさまざまな定量化可能なストレスシナリオでの干渉に対するハードウェアの感度が含まれます。

- テスト手順の実装。 現在、MASTECSで自動化される手動プロセスであるこのステップでは、テストフレームワーク、マイクロベンチマーク、および結果を記録/追跡するための測定プローブで構成されるテスト手順を構築します。

- 証拠収集(テスト)。 テスト手順は、テストの証拠を収集するためにプラットフォーム上で実行されます。現在、いくつかの手作業が含まれていますが、これはRapiTest自動化フレームワークを使用してMASTECSで自動化され、これらのテストを実行して検証要件にリンクします。

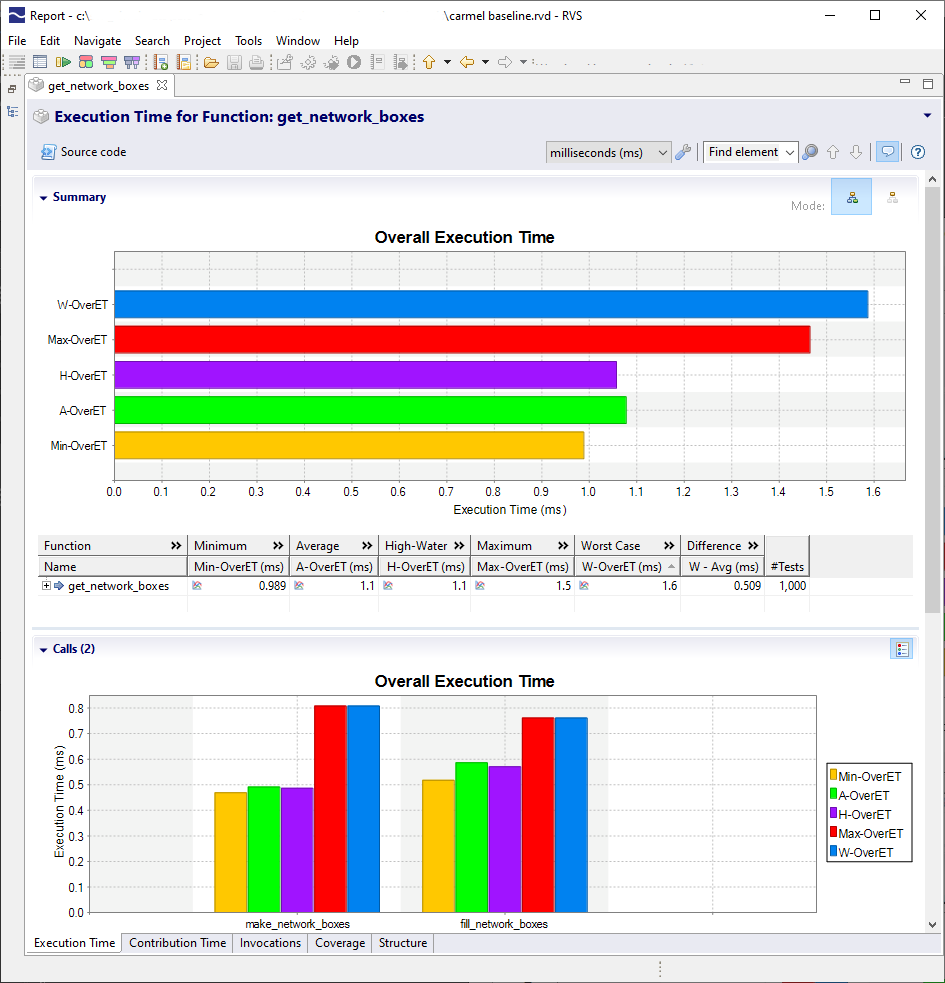

- 結果分析。 技術専門家によるテスト結果のレビュー。テスト結果が検証要件をどのように検証するか(または検証しないか)を確認します。たとえば、図3は、プログラムのさまざまな機能について報告された実行時間に関するRapiTimeのスクリーンショットを示しています。

- 結果を検証し、ドキュメントを生成します。 システムの安全性の議論をサポートするための要件の最終レビュー、文書の生成、および認定結果。お客様は、マルチコアで実行されているソフトウェアの認証に、レポートと分析成果物のフルセットを直接使用できます。

クリックすると拡大画像が表示されます

図2:Vモデルソフトウェア開発プロセスのMTAステップ。 (出典:著者)

ハードウェアの専門知識とタイミング分析プロセス

ハードウェア(マルチコア)の専門知識を注入することは、最新の複雑なマルチコアで成功するために提案されたMTAアプローチの重要な特徴です。ソフトウェア開発の初期段階:

- ハードウェアの専門家は、マルチコア構成(アビオニクス用語の重要な構成設定)を特定します。これらは、ソフトウェアの機能とタイミングの動作を決定する上で重要な役割を果たし、相互に生成する競合タスクの量に大きく影響します。説明に役立つ例として、現在のプロセッサは、適切に展開された場合に競合を大幅に減らすことができる分離および分離メカニズムを実装しています。

- マルチコアの専門家は、タスクの競合が発生する可能性のあるリソースを特定する上で重要な役割を果たします(これらはアビオニクスでは干渉チャネルと呼ばれます)。ハードウェアの専門家が数千ページのプロセッサテクニカルリファレンスマニュアルをナビゲートし、チップベンダーへのマニュアルの潜在的な欠落情報に関する適切な質問を作成する能力は、適切なMTAプロセスを推進するための基本です。

- 干渉チャネルが特定されると、ハードウェアの専門家は、タスクが受ける可能性のある競合を制限するためのプロキシメトリックとして、タスクがそれらの干渉チャネルで生成するアクティビティを追跡するために使用できるイベントモニターを特定します。これらのイベントモニターの正確さも検証する必要があります[2]。特殊なマイクロベンチマークのセットが設計されています。

- 最後に、ハードウェアの専門家はタイミング分析の専門家と協力して、ユーザー要件から高レベルおよび低レベルの要件と特定のテストを導き出し、ユーザー要件をサポートする仮説を検証します。各テストは、ハードウェアの専門家によって設計された1つまたは複数のマイクロベンチマークプログラムをインスタンス化して、ターゲット(セット)の干渉チャネルに必要なレベルの負荷をかけます。

設計後期:

- ハードウェアの専門家は、テスト結果の分析に貢献して、仮説を確認するか拒否するかを評価します。

- ハードウェアの専門家は、前のステップで得られた結果に基づいて、新しい仮説とそれに対応するテストが必要になった場合の確立にも貢献します。

クリックすると拡大画像が表示されます

図3:結果の分析(RapiTime)。 (出典:著者)

全体像

7ステップのテスト設計プロセスは、図2で前述したより広範なマルチコア検証方法の一部にすぎません。この方法は、MASTECSプロジェクトの一部として成熟し続け、包括的な証拠と結果は、対応する要件と設計に戻ります。この方法論は、航空宇宙認証局によって発行された主要なガイダンス文書であるCAST-32Aで定義された目的を満たすように設計されています。また、干渉からの解放を提唱する自動車セクターの安全基準であるISO26262とも特に整合しています。

CAST-32Aは、2016年にCertification Authority Software Team(CAST)によって公開され、マルチコアプロセッサで実行される航空機搭載ソフトウェアシステムの安全性、パフォーマンス、および整合性に影響を与える要因を特定します。アビオニクスシステムでマルチコアハードウェアを使用する場合は、これが頼りになるドキュメントです。これは、干渉チャネルの影響の特定と制限に関連する目的を含む、安全なマルチコアアビオニクスシステムの製造をガイドすることを目的とした目的を提供します。こちらからCAST-32Aのポジションペーパーをご覧ください。 EASAとFAAは、マルチコア汎用CRIを共通のAMC / AC材料(AMC 20-193)に適合させることに取り組んでいます。 「今年後半」に公開される予定です[3]。

専門知識を自動化することはできません

干渉効果は複雑です。彼らの謎を解明するには、マルチコアアーキテクチャのコンポーネントと、ソフトウェアのスケジューリングおよびリソース割り当てシステムの両方を理解している専門家が必要です。ハードウェアとソフトウェアの専門家間のコラボレーションは、MASTECSプロジェクトの中心的な機能であり、今後も継続されます。コラボレーションはソフトウェアツールと自動化に大きな進歩をもたらしますが、検証プロセスのすべてのステップを自動化できるわけではないことを覚えておくことが重要です。特にマルチコアタイミング分析が含まれる場合はそうではありません。

システムを詳細に理解している経験豊富なエンジニアが必要です。たとえば、初期段階では、マルチコアエキスパートは、ソフトウェアの機能とタイミングの動作、および潜在的な干渉チャネルを決定するプロセッサ構成(ハードウェアクリティカル構成設定とも呼ばれます)を特定できます。テスト結果の分析に関しては、経験豊富な人間の専門家の意見に勝るものはありません。プラットフォームについて行われた元の仮定を再検討して評価し、彼らの知識を使用して新しいテストサイクルにフィードします。

参考資料

[1]ラインハルト・ヴィルヘルム。混合された重要性についての混合された感情。最悪実行時間分析に関するワークショップ、2018年。

[2] Enrico Mezzetti、Leonidas Kosmidis、Jaume Abella、FranciscoJ.Cazorla。信頼性の高いタイミングV&V用の自動車用チップの高信頼性性能監視ユニット。 IEEE Micro 38(1):56-65(2018)。

[3] https://www.aviationtoday.com/2020/02/28/easa-and-faa-to-issue-further-guidance-on-multicore-certification-this-year/

埋め込み

- デバッグとは:組み込みシステムのタイプとテクニック

- 自動車における組み込みシステムの役割

- 組み込みシステムとそのリアルタイムアプリケーションとは

- テキスト文字列は組み込みソフトウェアの脆弱性ですか?

- 組み込みエッジ用のSOAFEEアーキテクチャにより、ソフトウェア定義の自動車が可能になります

- TRS-STAR:価値のある堅牢でファンレスの組み込みシステム

- Axiomtek:ミッションクリティカルで過酷な環境向けの3.5インチ組み込みSBC

- IIoTソフトウェアの脆弱性が重大なインフラストラクチャ攻撃を助長—再び

- 人工知能は量子システムの振る舞いを予測します

- 組み込みシステムとシステム統合

- DevOpsを使用した組み込みソフトウェアの課題への対処