量子デバイス

ほとんどの集積回路は、MOS(CMOS)トランジスタに基づくデジタルです。 1960年代後半から数年ごとにジオメトリの縮小が行われ、回路密度が向上しました。同じスペースでより多くの回路をより低コストで利用できます。この記事の執筆時点(2006年)では、MOSトランジスタのゲート長は最先端の製品で65 nmであり、1年以内に45nmが見込まれています。 65nmではリーク電流が明らかになりつつありました。 45 nmでは、この漏れを最小限に抑えるために英雄的な革新が必要でした。 MOSトランジスタの収縮の終わりは20〜30nmであると予想されます。 1〜2nmが限界だと考える人もいますが。フォトリソグラフィー、または他のリソグラフィー技術は、さらに改善され続け、さらに小さな形状を提供します。ただし、従来のMOSトランジスタは、20〜30nm未満のこれらの小さな形状では使用できないと予想されます。

改良されたフォトリソグラフィーは、従来のトランジスター以外の寸法(20〜30 nm未満)に適用する必要があります。不快なMOSリーク電流は、量子力学的効果、つまりゲート酸化物を通る電子トンネリングと狭いチャネルによるものです。要約すると、量子力学的効果は、これまでになく小型の従来型MOSトランジスタの障害となっています。ますます小さな形状のデバイスへの道には、量子力学的原理を実際に利用する独自のアクティブデバイスが含まれます。物理的形状が非常に小さくなると、電子は量子力学的同等物、つまり波として扱われる可能性があります。量子力学的原理を利用するデバイスには、共鳴トンネルダイオード、量子トンネルトランジスタ、金属絶縁体金属ダイオード、および量子ドットトランジスタが含まれます。

量子トンネリング

量子トンネリング: は、ドブロイ電子の波長に比べて薄い絶縁バリアを電子が通過することです。 「電子波」がバリアに比べて大きい場合、バリアの両側に波が現れる可能性があります。

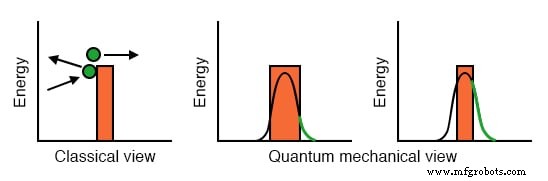

障壁を乗り越えるかどうかの古典的な見方。量子力学的ビューにより、電子はバリアを通り抜けることができます。確率(緑)はバリアの厚さに関連しています。図1の後

古典物理学では、電子は障壁を乗り越えるのに十分なエネルギーを持っている必要があります。そうでなければ、それは障壁から反動します。 (上の図)量子力学は、電子が障壁の反対側にある確率を考慮に入れています。波として扱うと、電子はバリアの厚さに比べてかなり大きく見える場合があります。波として扱っても、厚い障壁の向こう側で見つかる可能性はごくわずかです。上の図の曲線の緑色の部分を参照してください。バリアを薄くすると、電子がバリアの反対側で見つかる可能性が高くなります。

トンネルダイオード

トンネルダイオード: 修飾されていない用語トンネルダイオード esakiトンネルダイオードを指します 、初期の量子デバイス。逆バイアスされたダイオードは、導電性のアノードとカソードの間に空乏領域、つまり絶縁領域を形成します。この空乏領域は、高濃度にドープされた場合の電子波長と比較してわずかです。整流ダイオードのドーピングの1000倍です。適切なバイアスをかけると、量子トンネリングが可能になります。詳細については、CH3を参照してください。

共鳴トンネルダイオード(RTD)

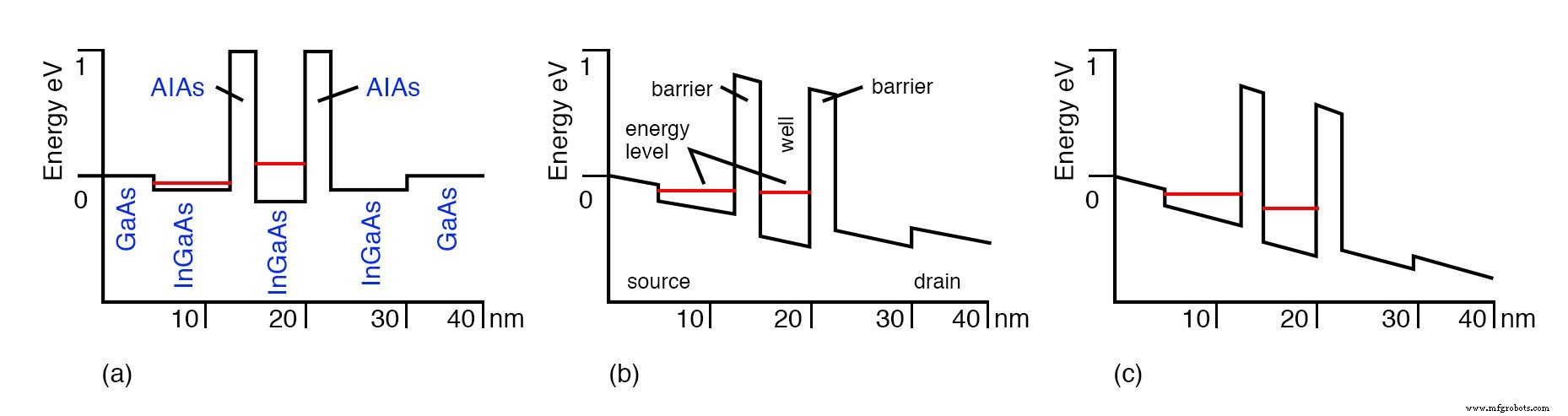

RTD、共鳴トンネルダイオード: これは、従来の高濃度にドープされたバイポーラ半導体であるEsakiトンネルダイオードCH3と混同しない量子デバイスです。電子トンネル 共鳴トンネルダイオードを排出するために、流れるソースのウェルによって分離された2つのバリアを通過します。 。トンネリングは、量子力学的トンネリングとしても知られています。電子の流れはダイオードバイアスによって制御されます。これは、電子が障壁を通り抜けることができるように、ソース内の電子のエネルギーレベルをウェル内の量子化されたレベルに一致させます。井戸が小さいため、井戸のエネルギーレベルが量子化されます。エネルギーレベルが等しい場合、共鳴 下の図(b)に示すように、電子がバリアを通過できるようになります。下の図(a)と(c)で、バイアスがないかバイアスが大きすぎると、ソースとウェルの間にエネルギーの不一致が生じ、伝導がなくなります。

共鳴トンネルダイオード(RTD):( a)バイアスがなく、ソースとウェルのエネルギーレベルが一致せず、伝導がありません。 (b)小さなバイアスは、一致したエネルギーレベル(共振)を引き起こします。伝導の結果。 (c)バイアスがさらにエネルギーレベルを不一致にし、伝導を減少させます。

RTD全体でバイアスがゼロから増加すると、電流は増加してから減少し、オフ、オン、およびオフの状態に対応します。これにより、2つのトランジスタの代わりにRTDのペアを使用することで、従来のトランジスタ回路を簡素化できます。たとえば、2つの連続したRTDと1つのトランジスタがメモリセルを形成し、従来の回路と比較して、使用するコンポーネント、面積、電力が少なくなります。 RTDの潜在的な用途は、すべてではありませんが一部のトランジスタを交換することにより、従来のトランジスタ回路のコンポーネント数、面積、および消費電力を削減することです。 [GEP] RTDは最大712gHzで発振することが示されています。 [ERB]

2層トンネリングトランジスタ(Deltt)

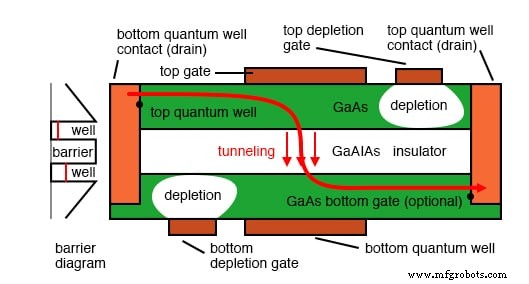

2層トンネリングトランジスタ: Deltt 、別名二重層トンネリングトランジスタ は、絶縁体または高バンドギャップ半導体によって分離された一対の導電性ウェルで構成されています。 (下の図)ウェルは非常に薄いため、電子は2次元に閉じ込められます。これらは量子井戸として知られています 。これらの量子井戸のペアは、薄いGaAlAs、高バンドギャップ(容易に伝導しない)層によって絶縁されています。電子はトンネルできます 2つの量子井戸の電子が同じ運動量とエネルギーを持っている場合は、絶縁層を通過します。ウェルは非常に薄いため、電子は波として扱われる可能性があります。粒子と波の量子力学的二重性です。上部およびオプションの下部制御ゲートは、電子のエネルギーレベル(共鳴)を等しくして、ソースからドレインへの伝導を可能にするように調整できます。下の図のバリア図の赤いバーは、「オフ状態」の状態であるウェル内の不均等なエネルギーレベルを示しています。ゲートに適切なバイアスをかけると、ウェル内の電子のエネルギーレベルが均等になります。これは「オン状態」の状態です。バーは、エネルギー準位図で同じレベルになります。

二層トンネリングトランジスタ(Deltt)は、非導電性バリアによって分離された2つの電子含有ウェルで構成されています。ゲート電圧は、ウェル内の電子のエネルギーと運動量が等しくなるように調整できます。これにより、電子は非導電性バリアを通り抜けることができます。 (エネルギーレベルは、バリア図では等しくないものとして示されています。)

ゲートバイアスがトンネリングに必要な値を超えて増加すると、量子井戸のエネルギーレベルが一致しなくなり、トンネリングが抑制され、ソースからドレインへの電流が減少します。要約すると、ゲートバイアスをゼロから増やすと、オン、オフ、オンの状態になります。これにより、DelttのペアをCMOS相補ペアのようにスタックできます。ただし、異なるp型トランジスタとn型トランジスタは必要ありません。電源電圧は約100mVです。 4.2 K、77 K、および0°C付近で動作する実験用デルトが製造されています。室温バージョンが予想されます。[GEP] [IGB] [PFS]

金属-絶縁体-絶縁体-金属(MIIM)

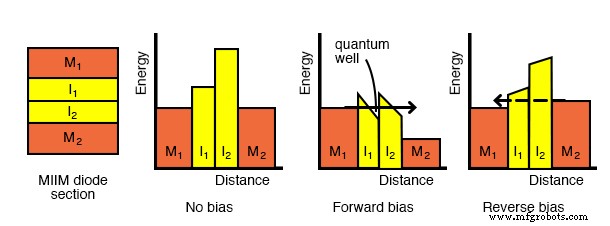

MIIMダイオード: metal-insulator-insulator-metal (MIIM)ダイオードは、半導体に基づかない量子トンネリングデバイスです。下の「MIIMダイオードセクション」の図を参照してください。量子トンネリングを可能にするには、絶縁体層をドブロイ電子の波長に比べて薄くする必要があります。ダイオードの動作には、優先トンネル方向が必要であり、その結果、ダイオードの順方向特性曲線が急激に曲がります。 MIIMダイオードは、ここでは考慮されていない、金属絶縁体金属(MIM)ダイオードよりも鋭いフォワードカーブを持っています。

金属絶縁体絶縁体金属(MIIM)ダイオード:ダイオードの断面。バイアスなし、順方向バイアス、および逆方向バイアスのエネルギーレベル。図1の後。

M1とM2のエネルギーレベルは、上の「バイアスなし」の図では同じです。ただし、I1とI2の障壁が高いため、(熱)電子は流れません。金属M2の電子は、上の「逆バイアス」図でより高いエネルギーレベルを持っていますが、それでも絶縁体の障壁を克服することはできません。上記の「フォワードバイアス」の図が大きくなると、量子井戸 、電子が存在する可能性のある領域は、絶縁体の間に形成されます。 M1が量子井戸と同じエネルギー準位に基づいている場合、電子は絶縁体I1を通過する可能性があります。簡単な説明は、絶縁体を通る距離が短いということです。より長い説明は、バイアスが増加するにつれて、電子波がM1から量子井戸にオーバーラップする確率が増加するということです。詳細な説明については、Phiar Corp. [PHI]

を参照してください。MIIMデバイスは、マイクロ波トランジスタよりも高い周波数(3.7 THz)で動作します。 [RCJ3] MIIMダイオードに3番目の電極を追加すると、トランジスタが生成されます。

量子ドットトランジスタ

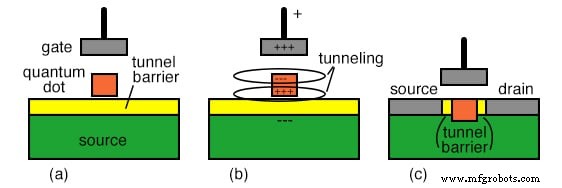

量子ドットトランジスタ: 孤立した導体は、大きな物体のクーロン単位で測定された電荷を帯びることがあります。 量子ドットとして知られるナノスケールの孤立した導体の場合 、電荷は電子で測定されます。 1〜3 nmの量子ドットは、単一電子の増分電荷を帯びることがあります。これが量子ドットトランジスタの基礎です 、単一電子トランジスタとも呼ばれます 。

電子が豊富なソース上の薄い絶縁体の上に配置された量子ドットは、単一電子ボックスとして知られています。 。 (下の図(a))電子を転送するために必要なエネルギーは、ドットのサイズとすでにドット上にある電子の数に関連しています。

量子ドットの上のゲート電極は、ドットのエネルギーレベルを調整できるため、ソースから絶縁体を介した電子の(波としての)量子力学的トンネリングが可能になります。 (下の図(b))したがって、単一の電子がドットにトンネリングする可能性があります。

(a)単一電子ボックス、絶縁体によって電子源から分離された孤立した量子ドット。 (b)ゲートの正電荷は量子ドットを分極し、電子をソースからドットにトンネリングします。 (c)量子トランジスタ:チャネルはトンネル障壁に囲まれた量子ドットに置き換えられます。

上の図(c)のように、量子ドットがトンネルバリアに囲まれ、従来のFETのソースとドレインの間に埋め込まれている場合、ドットの電荷がソースからドレインへの電子の流れを変調する可能性があります。ゲート電圧が増加すると、ソースからドレインへの電流がポイントまで増加します。ゲート電圧をさらに上げると、ドレイン電流が減少します。これは、RTDおよびDeltt共振デバイスの動作に似ています。相補型論理ゲートを構築するために必要なトランジスタは1種類だけです。[GEP]

単一電子トランジスタ

単一電子トランジスタ: 導体、超伝導体、または半導体のペアが、量子ドットのような小さな導電性の島を囲むトンネルバリア(絶縁体)のペアによって分離されている場合、単一の電荷の流れ(超伝導体のクーパー対)は、ゲート。これは単一電子トランジスタです 上の図(c)と同様です。ゲートの正電荷を増やすと、電子が島にトンネルすることができます。十分に小さい場合、静電容量が小さいと、単一電子のためにドット電位が大幅に上昇します。電子の電荷のために、これ以上電子は島にトンネリングできません。これは、クーロンブロッケードで知られています。 。島にトンネルした電子は、排水管にトンネルすることができます。

単一電子トランジスタは、ほぼ絶対零度で動作します。例外は、グラフェンアイランドを備えたグラフェン単一電子トランジスタです。これらはすべて実験的なデバイスです。

グラフェンおよびカーボンナノチューブトランジスタ

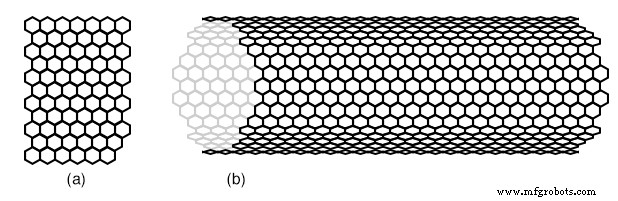

グラフェントランジスタ: 炭素の同素体であるグラファイトは、ダイヤモンドのような堅固なインターロッキング結晶構造を持っていません。それでもなお、それは結晶構造を持っています– 1原子の厚さ、いわゆる二次元構造。グラファイトは三次元の結晶です。しかし、それは薄いシートに劈開します。実験者は、これを極端にとらえて、グラフェンとして知られる単一の原子と同じくらい薄いミクロンサイズの斑点を生成します。 。 (下の図(a))これらの膜は独特の電子特性を持っています。導電性の高い伝導は、電子または正孔のいずれかによって行われ、いかなる種類のドーピングも行われません。 [AKG]

グラフェンシートは、リソグラフィー技術によってトランジスタ構造に切断することができます。トランジスタはMOSFETにいくらか似ています。グラフェンチャネルに容量結合されたゲートが伝導を制御します。

シリコントランジスタのサイズが小さくなると、消費電力とともにリークが増加します。そして、それらは数年ごとに小さくなります。グラフェントランジスタはほとんど電力を消費しません。そして、それらは高速で切り替わります。グラフェンはいつかシリコンの代わりになるかもしれません。

グラフェンは、幅60原子程度のデバイスに加工できます。この小さなトランジスタ内のグラフェン量子ドットは、単一電子トランジスタとして機能します。 。超伝導体または従来の半導体のいずれかから作られた以前の単一電子トランジスタは、絶対零度近くで動作します。グラフェン単一電子トランジスタは、室温で独自に機能します。[JWA]

グラフェントランジスタは、現時点では実験室の好奇心です。 20年後に生産を開始するためには、グラフェンウェーハを生産する必要があります。最初のステップである化学蒸着(CVD)によるグラフェンの製造は、実験規模で達成されました。ただし、これまでに利用できるウェーハはありません。

(a)グラフェン:炭素のグラファイト同素体の1枚のシート。原子は六角形のパターンで配置され、各交点に炭素があります。 (b)カーボンナノチューブ:グラフェンを丸めたシート。

カーボンナノチューブトランジスタ: グラフェンの2次元シートを巻いた場合、結果として得られる1次元構造はカーボンナノチューブと呼ばれます。 。 (上の図(b))1次元として扱う理由は、導電性が高いためです。電子は、結晶格子によって散乱されることなくカーボンナノチューブを通過します。通常の金属の抵抗は、金属の結晶格子による電子の散乱によって引き起こされます。電子がこの散乱を回避する場合、伝導は弾道輸送によると言われます 。金属(作用)と半導体の両方のカーボンナノチューブが製造されています。 [MBR]

電界効果トランジスタは、両端にソース接点とドレイン接点を配置し、接点間でゲートをナノチューブに容量結合することにより、カーボンナノチューブから作成できます。 p型トランジスタとn型トランジスタの両方が製造されています。なぜカーボンナノチューブトランジスタに関心があるのですか?ナノチューブ半導体は、シリコントランジスタと比較して、より小さく、より速く、より低い電力です。 [PNG]

スピントロニクス

スピントロニクス: 従来の半導体は、電子の電荷、電流の流れを制御します。デジタル状態は、電流の「オン」または「オフ」フローで表されます。小さな形状に移行するにつれて半導体の密度が高くなるにつれて、熱として放散しなければならない電力が増加し、除去が困難になります。電子は、スピンなどの電荷以外の性質を持っています。 電子スピンの暫定的な説明 は、地球の日周回転に類似した、スピン軸を中心とした分布電子電荷の回転です。電荷の動きによって生成される電流のループは、磁場を形成します。ただし、電子は分布電荷というよりは点電荷に似ているため、回転分布電荷のアナロジーはスピンの正しい説明ではありません。電子スピンは、デジタル状態を表す可能性のある上または下の2つの状態のいずれかを持つ可能性があります。より正確には、スピン(ms)量子数は角運動量(l)量子数の±1/2である可能性があります。 [DDA]

電荷の流れの代わりに電子スピンを制御すると、電力損失が大幅に減少し、スイッチング速度が向上します。 スピントロニクス 、 SPIN TRansportelectrONICSの頭字語 電子スピンの生成、制御、および検出が困難なため、広く適用されていません。ただし、高密度の不揮発性磁気スピンメモリは、変更された半導体プロセスを使用して製造されています。これはスピンバルブに関連しています コンピュータのハードディスクドライブで使用される磁気読み取りヘッド。ここではこれ以上説明しません。

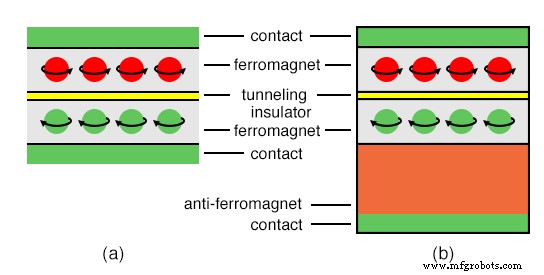

単純な磁気トンネル接合(MTJ) 下の図(a)に、強磁性のペアで構成されています。 、鉄(Fe)のような強い磁気特性、薄い絶縁体で分離された層。電子の量子力学的特性、つまり電子の波動性により、電子は十分に薄い絶縁体を通り抜けることができます。 MTJを流れる電流は、強磁性層の磁化、スピン極性の関数です。最上層の磁気スピンが最下層と同じ方向(極性)にある場合、MTJの抵抗は低くなります。 2つの層の磁気スピンが反対の場合、抵抗は高くなります。 [WJG]

(a)磁気トンネル接合(MTJ):薄い絶縁体で分離された強磁性層のペア。抵抗は最上層の磁化極性によって変化します。(b)反強磁性バイアス磁石とピン留めされた下部強磁性層は、最上層の強磁性層の極性の変化に対する抵抗感度を高めます。 [WJG]図3から引用。

抵抗の変化は、反強磁性体を追加することで強化できます。 、上の図(b)の最下層の下に、スピンが整列しているが反対側にある材料。このバイアスマグネットピン 下の強磁性層は、単一の不変の極性に回転します。最上層の磁化(スピン)は、図に示されていない外部磁場の印加によってデータを表すために反転させることができます。ピン留めされた層は、外部磁場の影響を受けません。この場合も、MTJ抵抗は、上部の強磁性層のスピンが下部のピン留めされた強磁性層と同じ意味である場合に最も低くなります。 [WJG]

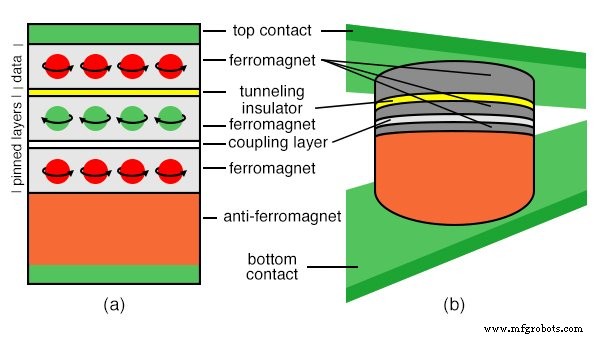

MTJは、ピン留めされた強磁性層を下の図(a)のバッファ層で分離された2つの層に分割することでさらに改善できます。これにより、最上層が分離されます。下の強磁性層は、前の図のように反強磁性体によって固定されています。バッファの上の強磁性層は、下の強磁性層に引き付けられます。反対側が引き付けます。したがって、追加の層のスピン極性は、引力のために最下層のスピン極性と反対です。下部と中央の強磁性層は固定されたままです。最上部の強磁性層は、近接する導体(図示せず)の大電流によっていずれかのスピン極性に設定することができます。これがデータの保存方法です。データは、トンネル接合を流れる電流の差によって読み取られます。絶縁層の両側の層が同じスピンである場合、抵抗は最も低くなります。 [WJG]

(a)(b)のピン留めされた強磁性層をバッファ層で分割すると、安定性が向上し、上部の強磁性のピン留めされていない層が分離されます。データは、スピン極性に基づいて最上位の強磁性層に保存されます(b)多くのMTJの1つである半導体ダイの読み取りラインに埋め込まれたMTJセル。 [IBM]

から採用磁気トンネル接合のアレイは、従来のCMOS回路を使用してMTJからデータビットを読み取るために上部端子と下部端子を接続する導体を備えたシリコンウェーハに埋め込むことができます。そのようなMTJの1つが、読み取り導体とともに上の図(b)に示されています。示されていないが、重い書き込み電流を運ぶ別の交差した導体のアレイは、データを格納するために最上部の強磁性層の磁気スピンを切り替える。多くの「X」導体の1つと「Y」導体に電流が流れます。アレイ内の1つのMTJは、導体のクロスオーバーの下で磁化されます。データは、従来のシリコン半導体回路でMTJ電流を検出することによって読み取られます。 [IBM]

磁気トンネル接合メモリに関心がある主な理由は、それが不揮発性であるということです。 。電源を「オフ」にしてもデータは失われません。他のタイプの不揮発性メモリは、限られたストレージサイクルしか実行できません。 MTJメモリは、ほとんどの半導体メモリタイプよりも高速です。現在(2006年)の商品です。 [TLE]

市販の製品ではなく、実験装置でさえ、いつかスピン論理ゲートを可能にするかもしれない理論上のスピントランジスタではありません。スピントランジスタは、理論上のスピンダイオードの派生物です。コバルト鉄強磁性体を流れる電子がスピン偏極することは以前から知られていました。強磁性体は、1つのスピンの電子を優先的に通過させるフィルターとして機能します。これらの電子は、隣接する非磁性導体(または半導体)に流れ込み、スピン偏極を短時間(ナノ秒)保持します。ただし、スピン偏極電子は、半導体の寸法と比較してかなりの距離を伝搬する可能性があります。スピン偏極電子は、半導体に隣接するニッケル-鉄強磁性層によって検出され得る。 [DDA] [RCJ2]

円偏光が一部の半導体材料を照射すると、電子スピン偏極が発生することも示されています。したがって、スピン偏極した電子を半導体ダイオードまたはトランジスタに注入することが可能であるはずです。スピンベースのトランジスタとゲートへの関心は、散逸性の電荷の流れと比較して、スピン伝播の非散逸性の性質によるものです。従来の半導体のサイズが縮小されると、消費電力が増加します。ある時点で、スケールダウンは実用的ではなくなります。研究者は、従来の電荷流ベースのトランジスタの代替品を探しています。そのデバイスは、スピントロニクスに基づいている可能性があります。 [RCJ]

レビュー:

- MOSゲート酸化膜は、トランジスタが世代を重ねるごとに薄くなるため、ゲートリークが多すぎると、許容できない電力損失と加熱が発生します。従来の半導体ジオメトリのスケールダウンの限界は見えています。

- 共鳴トンネルダイオード(RTD):従来の半導体を劣化させる量子力学的効果がRTDで採用されています。十分に薄い絶縁体を通る電子の流れは、電子と粒子の波動の二重性の波の性質によるものです。 RTDはアンプとして機能します。

- 二重層トンネリングトランジスタ(Deltt):DelttはRTDのトランジスタバージョンです。ゲートバイアスは、ある量子井戸から別の量子井戸へ(ソースからドレインへ)薄い絶縁体をトンネルする電子の能力を制御します。

- 量子ドットトランジスタ:電荷を保持できる量子ドットは、従来のFETのゲートに代わる薄いトンネルバリアに囲まれています。量子ドットの電荷は、電流を流すためのソースを制御します。

- スピントロニクス:電子には、電荷とスピンという2つの基本的な特性があります。従来の電子機器は、電荷の流れを制御し、エネルギーを消費します。スピントロニクスデバイスは、電子スピン、つまり伝播的で非散逸的なプロセスを操作します。

関連するワークシート:

- 半導体ワークシートの電気伝導

産業技術