ADCコードのエラー率を理解する

高速アナログ-デジタルコンバータ(ADC)のサンプリングレートが向上するにつれて、ADCの出力データのコードエラー(スパークルコードとも呼ばれる)の問題も発生します。コードエラーは、定義されたしきい値を超えるADCの出力コードのエラーとして定義されます。しきい値は、最も一般的には、ノイズが存在する場合にエラーを簡単に識別できるように、エラーがADCのノイズの予想される振幅を超えるレベルとして定義されます。

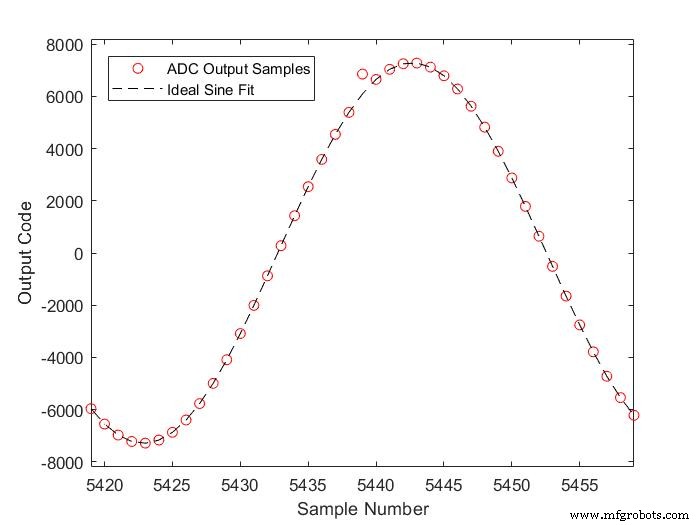

エラーしきい値のこの定義を説明する別の方法は、ADCの想定されるガウス分布ノイズが与えられた場合に、エラー振幅がその振幅の期待確率を超える確率で発生することです。 図1 は、ADCの出力サンプルで見つかったコードエラーの例を示しています。誤ったサンプルは、理想的な正弦波フィットと比較するとはっきりと見え、プロット内の他のサンプルのノイズをはるかに上回っています。

図1:コードエラーのあるADC出力の例。

ADCのコードエラーレート(CER)は、ワードエラーレート(WER)またはメタスタビリティエラーレートとも呼ばれ、サンプルあたりの平均エラー数として定義され、連続するエラー間の平均サンプル数をカウントすることで測定されます。ほとんどの場合、10 –12 などの1桁として定義されます。 エラー/サンプル。したがって、エラー間の平均時間は、コンバータのサンプリングレートに依存します。測定されたCERは、ADCがCERが測定されたサンプリングレートで動作している場合にのみ正確です。一般に、サンプリングレートを下げると、CERが桁違いに向上します。

サンプリングレートが主な要因である理由を確認するために、コードエラーがどこから発生するかを見てみましょう。

ADCを輝かせる理由は何ですか?

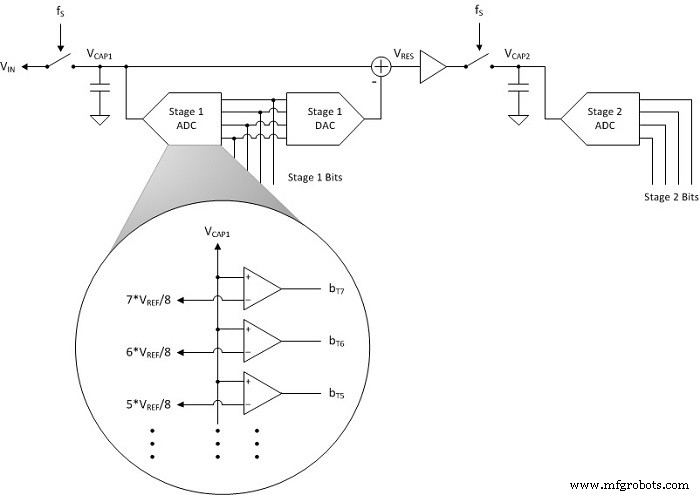

パイプラインフラッシュADCや逐次比較レジスタ(SAR)ADCなどのマルチステップADCアーキテクチャは、サンプリングされた電圧を段階的にデジタルビットに変換し、連続する各ステージは前のステージの結果に依存します。 図2 に示すように、基本的なパイプラインフラッシュ高速ADCについて考えてみます。 。この簡略化されたADCは、2つの変換ステージを示しています。各ステージでは、入力信号をより詳細に推定するデジタルコードが生成されます。

示されているADCの動作は次のとおりです。

-

第1ステージは入力電圧をサンプリングし、第1ステージADCを使用してアナログ入力信号をデジタルコードに大まかに変換します。この段階のフラッシュADCは、サンプリングされた電圧を、ADCのメインリファレンス電圧(V REF )から生成された静的電圧リファレンスと比較することによって機能します。 )、高速コンパレータを使用します。フラッシュコンパレータの出力は、入力電圧を表す温度計でエンコードされたデジタルサンプルです。

-

変換された温度計コードは、最初のステージのDACに直接送信されます。このDACは、粗く変換されたサンプルに対応するアナログ電圧を出力します。

-

元の入力電圧から第1段DACの出力を差し引くと、量子化誤差電圧または残留電圧(V RES )。次に、残留物は増幅され、第2段階のために再サンプリング(パイプライン化)されます。

-

第2段階のADCはV RES を量子化します 元のアナログ入力電圧のより正確な(より高解像度の)推定値を取得するため。

図2:パイプライン化されたフラッシュADCアーキテクチャのブロック図の例。

V RES 作成プロセスでは、高速の意思決定ループが導入されます。 1サンプリングクロック周期内で、サンプリングされた電圧は第1段ADCによってデジタルコードに変換される必要があります。デジタルコードは、第1ステージのDACから出力され、元の入力電圧から差し引かれ、第2ステージでリサンプリングされる必要があります。高速決定ループでは、フラッシュADCのコンパレータのセトリング時間が、サンプリングされた電圧とV REF の差の関数であるため、コードエラーが発生します。 。

より簡単に言えば、入力電圧(V CAP1 )が基準電圧に近い(7 * V REF など) / 8)コンパレータの。理論的には、V CAP1 コンパレータの基準電圧に非常に近い場合、コンパレータは線形領域で動作するため、安定することはありません。

ノイズはこれが実際に発生するのを防ぎますが、コンパレータが安定するのに時間がかかりすぎる場合、第1段DACは誤ったデジタルコードを使用して量子化されたアナログ電圧を出力する可能性があります。結果はV RES です これは、第1段階のADCの実際のデジタル出力コードとは一致しません。次に、第2ステージADCは間違ったV RES を変換します 、コードエラーが発生します。

CERに影響するものは何ですか?

これで、CERに影響を与えるものについていくつかの結論を引き出すことができるように十分な詳細が得られるはずです。 CERは明らかにサンプリングレートに依存します。より速いサンプリングレートは、決定ループが決定を下さなければならない時間を短縮します。決定を下す時間が短くなると、コンパレータが時間内に落ち着かない確率が指数関数的に増加します。

–Matt Guibordは、TexasInstrumentsの高速コンバーターのシステムエンジニアです。

埋め込み