Verilogハードウェア記述言語入門

この記事では、Verilogモジュールの基本構造を学習し、Verilogの「wire」データ型とその使用例をいくつか見ていきます。ベクトル形式で、VHDLとVerilogの違いについて簡単に触れます。

この記事では、Verilogモジュールの基本構造を学習し、Verilogの「ワイヤ」データ型とそのベクトル形式の使用例をいくつか見て、VHDLとVerilogの違いについて簡単に触れます。

VerilogとVHDLは、デジタル回路を記述するために一般的に使用される2つの言語です。 AACには、VHDLの基本概念について説明した一連の技術記事があります。この記事は、Verilogに関するシリーズの出発点として機能します。

VerilogとVHDLの両方が必要ですか?

話し合いを始める前に、明らかな質問に答えましょう。これら2つの言語の両方を本当に知る必要があるのでしょうか?

VerilogとVHDLはどちらも、複雑なデジタル回路の設計に使用できる強力なツールです。これら2つのHDLにはいくつかの違いがありますが、マスターして使用するHDLはどちらかを自由に選択できます。ただし、ある時点で、少なくとも両方の言語の基本を理解することでメリットが得られると思います。設計者として、プロジェクトのコーディングについてのアイデアを得るためにサンプルコードセグメントが必要になる場合があります。私たちは何時間もネットをサーフィンし、最終的に必要なものを見つけますが、それは私たちには意味がありません。それは私たちにはまったくなじみのないHDLで書かれています。言語の基本を理解していないと、テクニックを完全に理解できない可能性があります。

Verilog Evolution

Verilogは、1984年の初めにGateway Design Automationによって設計されました(VHDLが米国国防総省によって開始されてから約3年後)。 DoDのサポートにより、VHDLは1987年にIEEE標準になりました。Verilogは1995年まで登場しませんでした。現在、VHDLとVerilogはどちらも人気のあるHDLであり、FPGA設計ツールは通常両方の言語をサポートしています。

「Verilog」という単語は、「検証」と「論理」という単語のかばん語です。これは、この言語がシミュレーションおよび検証ツールとして最初に提案されたためです。 Verilogの概念と構文を始めましょう。

例1

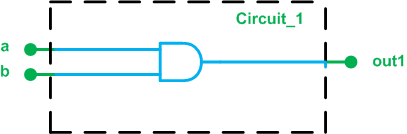

最初の例として、図1に示す回路のVerilogコードを記述してみましょう。

図1。 Circuit_1

2つの入力と1つの出力があります。ポートはすべて1ビット幅です。回路の機能は、2つの入力をANDし、その結果をout1ポートに出力することです。

Circuit_1モジュールで考えられるVerilogの説明の1つは、次のとおりです。

1行目と8行目

これらの2行は、キーワード「module」と「endmodule」を使用して、その間の行(2行目から7行目)がすべて「Circuit_1」という名前の回線を表すことを指定します。この名前は任意であり、後でこの回路を参照することができます。

2行目から6行目

これらの行は、「Circuit_1」とその周辺環境とのインターフェースを指定します。入力ポートと出力ポートは、キーワード「入力」と「出力」を使用して記述されます。これらのキーワードの後に別のキーワード「wire」が続き、次にポートの名前が続きます(図1を参照)。キーワード「wire」は何を指定しますか? 「ワイヤ」は、デザイン内の物理的なワイヤを表すVerilogデータ型です。 Verilogデータ型については今後の記事で詳しく説明しますが、今のところ、モジュールにはa、b、out1という3つのワイヤがあり、これらはポート宣言で指定されているため、モジュールインターフェイス。

7行目

この行では、ビット単位のAND演算子、つまり&を使用して、回路の機能を記述しています。キーワード「assign」は、出力ポートout1にa&bを配置します。このタイプの割り当ては、連続割り当てと呼ばれます。これは、右側のオペランドが変更されるたびに割り当てが常にアクティブになるため、a&bが評価され、out1に割り当てられるためです。連続割り当ては、入力に応じて出力が継続的に更新される組み合わせ回路として想定できます。この例では、この組み合わせ回路は単純なANDゲートです。 Verilog HDLには、今後の記事で説明する手順の割り当てもあります。

これで、ザイリンクスISEなどのソフトウェアパッケージを使用して、上記のコードを検証できます。このソフトウェアのVerilogベースのチュートリアルはここ(PDF)にあります。

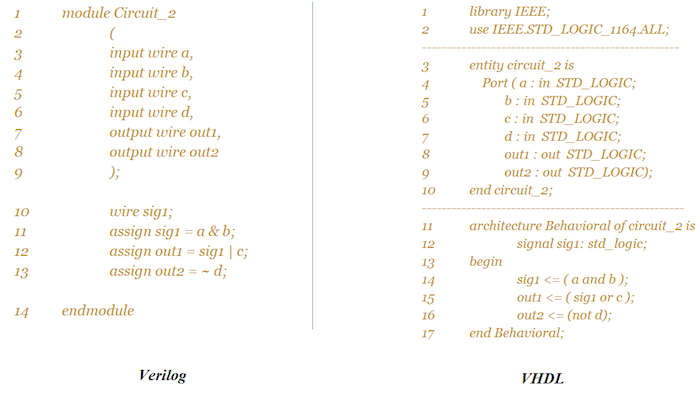

例1とVHDLコードの比較

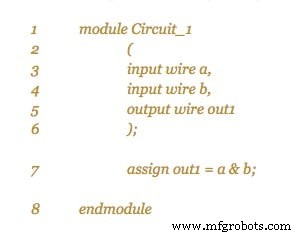

以下の図2は、Circuit_1モジュールのVerilogおよびVHDLの説明を示しています。

図2。 Circuit_1のVerilogとVHDLの説明の比較。

ご覧のとおり、VHDLでコーディングする場合はいくつかのライブラリを含める必要があります。これらのライブラリは、データ型と演算子の定義を提供します。これらのライブラリの追加とVHDLの一般的な形式を考慮すると、VHDLコードはより冗長であることがわかります。ただし、この冗長性には利点がないわけではありません。たとえば、VHDLのライブラリ管理機能は、高レベルのシステムをモデル化するときに役立ちます。今後の記事では、これら2つのHDLの長所と短所について説明することがあります。

Verilogには4つの値のシステムがあります

ほとんどのVerilogデータ型で使用される4つの基本的な値があります。リスト1で定義されているワイヤーは、次のいずれかの値を取ることができます。

- 0:ロジックローまたは誤った状態の場合

- 1:ロジックハイまたは真の状態の場合

- z:ハイインピーダンス状態の場合(トライステートバッファの出力を記述するために使用できます)

- x:ドントケアまたは不明な値の場合(入力が初期化されていない場合、または2つ以上の競合する出力が相互に接続されている場合)。

VHDL std_logicデータ型は9つの異なる値を取ることができますが、一般的に使用される値は「0」、「1」、「Z」、および「-」です(「-」はドントケアを示します)。

例2

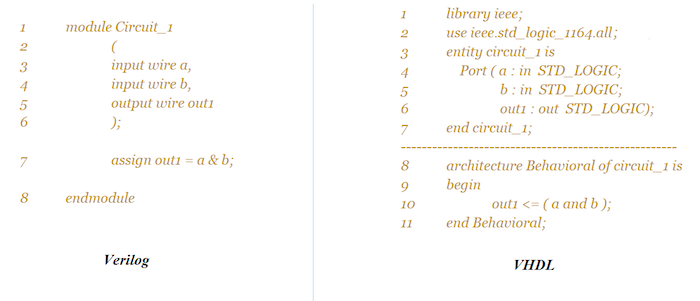

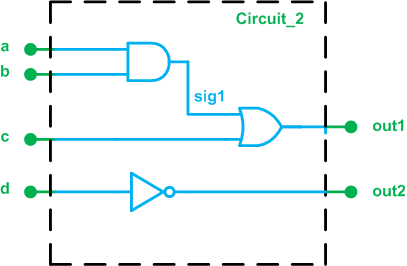

別の例として、図3に示す回路(Circuit_2というラベルを付けます)のVerilogコードを記述してみましょう。

図3。 Circuit_2

次のVerilogコードは、この回路を説明しています。

上記のコードで使用されている要素は、コードの10行目で内部信号が定義されていることを除いて、例1の要素と似ています。キーワード「wire」は、この接続のデータ型を指定するために使用されます。上で説明したように、「ワイヤ」データ型は、設計では物理的なワイヤに変換されます。

上記のコードでは、いくつかの新しいVerilogビット演算子も使用しています。 OR演算用。もう1つの便利なビット演算子は、XOR演算の^です。図4は、Circuit_2モジュールのVerilogとVHDLの両方の説明を示しています。このような比較は、これら2つの言語の相違点と類似点を確認するのに役立ちます。

図4。 Circuit_2のVerilogとVHDLの説明の比較。

例3

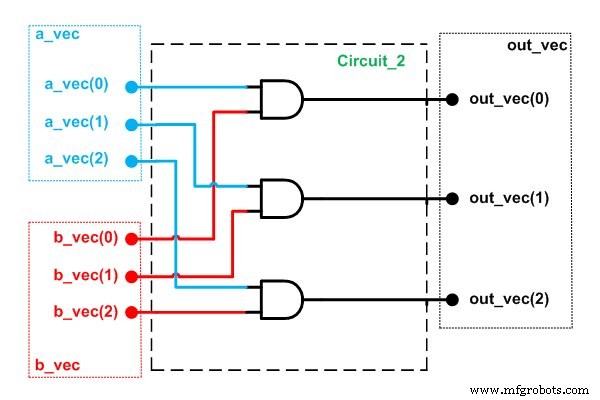

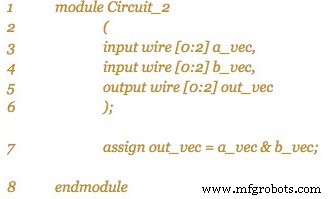

3番目の最後の例として、図5に示す回路図のVerilogコードを示します。

図5。 概略例3。

ご覧のとおり、青い入力ポートと赤い入力ポートの間には特定の関係があります。対応する入力はAND演算子で結合されます。結果は出力ポートに割り当てられます。このような場合、信号をグループ化してベクトルとして扱うことができます。これにより、コードがコンパクトで読みやすくなります。

Verilogのベクトルの概念を使用すると、リスト1のコードを簡単に拡張して、上記の回路を説明できます(以下のリスト3のコードを参照)。

ベクトルのインデックス範囲は、昇順([0:2])または降順([2:0])のいずれかであることに注意してください。上記では昇順の形式が使用されていますが、通常、降順の形式を使用するとエラーが発生しにくくなります。これは、降順のスタイルが、2進数の左端の位置が最も高いインデックスを持っているという私たちの認識と一致するという事実によるものです。ベクトルはVHDLでも使用されることに注意してください。

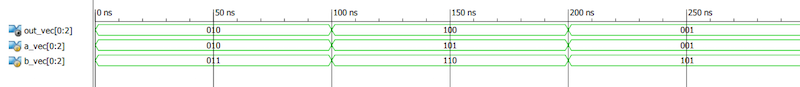

以下の図6は、リスト3のコードのISEシミュレーションを示しています。

図6。 例3のコードのISEシミュレーション。

この記事では、VHDLとVerilogの両方を学習することをお勧めします。また、Verilogモジュールの基本構造を学習し、Verilogの「ワイヤ」データ型とそのベクトル形式について理解しました。また、VHDLとVerilogのいくつかの違いについても簡単に触れました。 Verilogシリーズの次の記事では、Verilogでの組み合わせ回路の設計について説明します。

埋め込み