VHDL テストベンチでシミュレーションを停止する方法

シミュレーションが完了したときに VHDL シミュレータを停止するにはどうすればよいですか?それにはいくつかの方法があります。この記事では、テストベンチの実行を成功させる最も一般的な方法を検討します。

ここに示す VHDL コードはユニバーサルであり、対応するすべての VHDL シミュレータで動作するはずです。 Tcl を含むメソッドについては、ModelSim および Vivado シミュレーターのコマンドをリストします。

ModelSim がインストールされている場合は、この記事から 4 つの異なるテストベンチを含むサンプル プロジェクトをダウンロードできます。以下のフォームにメール アドレスを入力して、Zip ファイルを受け取ります。

finish の使用 手順

VHDL 仕上げ この手順は、エラーなしで完了する VHDL テストベンチを停止する私のお気に入りの方法です。 STD.ENV パッケージから「finish」をインポートする必要があり、それを使用するには VHDL-2008 以降でテストベンチをコンパイルする必要があります。

以下のコードは、テストベンチ シーケンサー プロセスの最後の行に到達したときにシミュレーションを終了します。

use std.env.finish; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'finish'"; finish; end process;

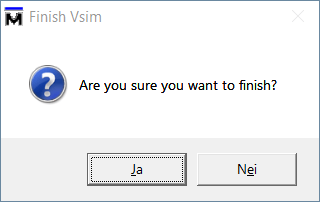

終了に注意してください デフォルトでシミュレーションを終了します。 GUI バージョンで ModelSim を実行している場合は、「終了してもよろしいですか?」というポップアップが表示されます。はいをクリックすると、ModelSim は終了します。

それはおそらくあなたが望むものではありません。幸いなことに、以下に示すように、vsim コマンドに「-onfinish stop」オプションを追加することで、この動作を防ぐことができます。そうすることで、仕上がり 手順は stop と同じように動作します 手順については、この記事の次のセクションで説明します。

vsim -onfinish stop work.using_finish_tb

finish を使用する利点 バッチ モードでシミュレートするときに、既定の動作を使用できるということです。スクリプトを使用してシミュレーションを開始している場合は、シミュレーションの終了後に呼び出し元のスクリプトに制御を戻す必要があります。

以下の例は、finish を使用したテストベンチを示しています。 手順は、Linux の ModelSim バッチ モードで開始されました。テストベンチが完了すると、シミュレーターが終了し、最後の行で Linux シェルに戻ります。

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_finish_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_finish_tb # vsim work.using_finish_tb # Start time: 22:58:31 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_finish_tb(sim) # run -all # ** Note: Calling 'finish' # Time: 1 ms Iteration: 0 Instance: /using_finish_tb # End time: 22:58:31 on Jun 21,2020, Elapsed time: 0:00:00 # Errors: 0, Warnings: 8 jonas@ubuntu:~/stop_tb$

VHDL 仕上げ 手順は、標準の ENV パッケージで定義されています。以下のコードからわかるように、オーバーロードされた 2 つのフレーバーがあります。私がいつも使用しているパラメーターなしのバージョンと、定数入力としてステータス整数を受け取るバージョンがあります。

procedure FINISH (STATUS: INTEGER); procedure FINISH;

Linux シェルから呼び出されると、ステータス整数が終了コードになると思うかもしれませんが、少なくとも ModelSim ではそうではありません。このステータス コードを使用する際の問題は、その動作がシミュレータに依存することです。 VHDL-2008 標準の文言は、「STATUS パラメータの値は、ホスト シミュレータによって定義された実装方法で使用される可能性があります」です。 「.

ただし、Tcl コマンド exit -code <value> を使用して、ModelSim で Linux 終了コード値を制御できます。 、しかしそれはまた別の話です。

停止の使用 手順

VHDL停止 手順により、シミュレーションが一時停止します。これは、信号値を手動で調べたい場合や、後でシミュレーションを続行したい場合に便利です。シミュレーターはこれをブレークポイントのように扱います。

以下の例は、stop をインポートして使用する方法を示しています。

use std.env.stop; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'stop'"; stop; end process;

stop の使用に関する問題 スクリプトベースの設定では、シミュレーションを終了しないということです。制御を呼び出し元に戻す代わりに、ModelSim は Tcl コマンド シェルを開き、呼び出しスクリプトを無期限にハングさせます。

以下のリストは、stop を使用するテストベンチを実行した場合の出力を示しています。 バッチモードでの手順。シミュレーションが停止した後も、まだ ModelSim にいます。 Tcl シェルから出るには、「exit」と入力する必要があります。

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_stop_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_stop_tb # vsim work.using_stop_tb # Start time: 22:58:56 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_stop_tb(sim) # run -all # ** Note: Calling 'stop' # Time: 1 ms Iteration: 0 Instance: /using_stop_tb # Break in Process SEQUENCER_PROC at ~/stop_tb/src/using_stop_tb.vhd line 23 # Stopped at ~/stop_tb/src/using_stop_tb.vhd line 23 VSIM 3>

仕上げのように 手順、停止 VHDL-2008 以降が必要です。以下に示すように、オーバーロードされたバージョンのプロシージャが存在します。整数のステータス値を取りますが、動作はシミュレーターによって異なります。

procedure STOP (STATUS: INTEGER); procedure STOP;

アサートの使用 キーワード

VHDL テストベンチを停止するためのフェールセーフで一般的な方法は、アサーション エラーを作成することです。これは、大学で VHDL を学んでいたときにシミュレーションを終了するように教えられた最初の方法でした。

追加のインポートは必要なく、すべての VHDL バージョンで機能します。重大度レベル failure を必ず使用してください

SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; assert false report "Test: OK" severity failure; end process;

そして、成功したシミュレーションを停止するこの方法が嫌いなのはなぜですか?

まず第一に、上記の例の出力を見ると奇妙で紛らわしく見えます:

# ** Failure: Test: OK

「失敗」と書いてありますが、同時にテストは「OK」です。それは assert ステートメントは、シミュレーションが正常に完了したことではなく、エラー状態を示しているはずです。

私が考えることができるもう 1 つの厄介な問題は、シミュレーションが成功したかどうかをプログラムで確認することが難しくなることです。

ほとんどの VHDL 専門家は、たとえば大規模な回帰テスト スキームの一部として、ある時点でスクリプトからシミュレーションを開始します。何も問題がないのにテストベンチがアサーション エラーで停止した場合、それをマーカーとして使用して VHDL モジュールの状態を判断することはできません。

Tcl の使用

これから説明するシミュレーションを停止する最後の方法は、Tcl を VHDL と組み合わせて使用することです。 VHDL ファイルからテストベンチを停止する代わりに、停止するタイミングで通常の VHDL 信号を設定します。そして事前に、このトリガー信号の変化をリッスンするようにシミュレーターを構成します。

こちらもお読みください:

Tcl を学ぶ必要がある理由

stop_condition という名前のシグナルを設定する以下の例を見てください。 すべてのテスト ケースが完了したとき。

signal stop_condition : boolean;

begin

-- Replace this line with your DUT instantiation

stop_condition <= not stop_condition after 1 ms;

SEQUENCER_PROC : process

begin

-- Put your testbench logic here

-- Pause this process forever after all tests are done

wait;

end process;

1 回の wait で、ジョブを完了したテストベンチ プロセスをスリープ状態にすることができます。 終了プロセスの前のステートメント 鬼ごっこ。これにより、再起動が妨げられます。シミュレーションを実際に停止するための Tcl コードは、シミュレータによって異なります。

ModelSim で

stop_condition になったときにテストベンチを停止する必要があります。 VHDL シグナルが true になる . VHDL テストベンチを実行する前に、Tcl でコールバックを設定することでこれを行うことができます。

ModelSim コマンド リファレンス マニュアルによると、Tcl when を使用してそれを実現できます。 指図。以下の Tcl コードでは、このようなコールバックを登録し、run -all を使用してシミュレータを開始します。 .

when {stop_condition} {

stop

echo "Test: OK"

}

run -all

中括弧内のコードは、コールバックが発生するまで実行されないことに注意してください。 VHDL コードが stop_condition を変更したとき true の合図 、シミュレーターは一時停止し、2 つの行を実行します。この例では、シミュレーションを停止し、「Test:OK」をコンソールに出力します。 Tcl exit を持つこともできます VHDL finish と同じように、シミュレーターを終了するコマンドがあります。

# vsim # Start time: 22:31:11 on Jun 22,2020 # Loading std.standard # Loading work.using_tcl_tb(sim) # Test: OK # Simulation stop requested.

上記のリストは、Tcl/VHDL テストベンチが完了したときに ModelSim コンソールに表示される出力を示しています。お使いのコンピューターで試してみたい場合は、以下のフォームを使用して、この記事のすべての例を含む ModelSim プロジェクトをダウンロードしてください!

Vivado で

Vivado Design Suite Tcl コマンド リファレンス ガイドによると、add_condition を使用して Tcl コールバックを登録できます。 指図。以下のコードは、前述の ModelSim バージョンに相当するザイリンクスを示しています。

set sim_fileset sim_1

launch_simulation -simset [get_filesets $sim_fileset]

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

run all

-notrace スイッチは、コールバック関数のコード行が実行時に端末にエコーされるのを防ぎます。コンソールに余計な物を散らかしたくない.

次のリストは、Vivado シミュレータ コンソールで実行されているシミュレーションからの抜粋です。

launch_simulation: ...

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

condition8

run all

Test: OK

最終的な考え

これまで見てきたように、VHDL シミュレーションを終了するには多くの方法があります。ただし、私が使用したのは VHDL-2008 finish だけです 手順。

現在、すべてのシミュレーターが VHDL-2008 をサポートしており、2008 では RTL コードをコンパイルする必要はなく、テストベンチのみをコンパイルする必要があります。 仕上げ この手順は最も移植性の高い方法であり、GUI モードで実行しているときにシミュレーターを停止したり、バッチ モードで実行しているときにシミュレーターを終了したりできます。ほとんどの場合、まさに私が望んでいる動作です。

ただし、この記事の範囲外の Tcl メソッドには利点があります。 Tcl コールバックでシミュレータを一時停止すると、シミュレータを停止して終了するだけでなく、さらに多くのことができます。コールバック中に、VHDL 信号を調べたり、Tcl を使用してそれらを操作したりすることもできます。これは Tcl を使用した検証です。

VHDL