ACおよびDCデータ取得シグナルチェーンの簡素化

アナログ-デジタルコンバータ(ADC)のサンプリング現象は、エイリアシングと容量性キックバックの問題を引き起こします。これらの問題を解決するために、設計者は独自の課題をもたらすフィルターと駆動増幅器を使用します。これにより、中帯域幅のアプリケーション領域で高精度のDCおよびACパフォーマンスを達成することが困難になり、設計者はシステムの目標をトレードオフすることになります。

この記事では、信号チェーンを単純化することでサンプリングの問題を本質的かつ劇的に解決する連続時間シグマデルタ(∑-Δ)ADCについて説明します。アンチエイリアシングフィルターとバッファーの必要性を排除し、追加のコンポーネントに関連するシグナルチェーンオフセットエラーとドリフトの問題を解決します。これらの利点により、ソリューションサイズが縮小され、ソリューション設計が容易になり、システムのフェーズマッチングと全体的な遅延が改善されます。この記事では、離散時間コンバーターとの比較も行い、システムの利点と、連続時間シグマデルタADCを使用する際の制約について説明します。

サンプリングの基礎

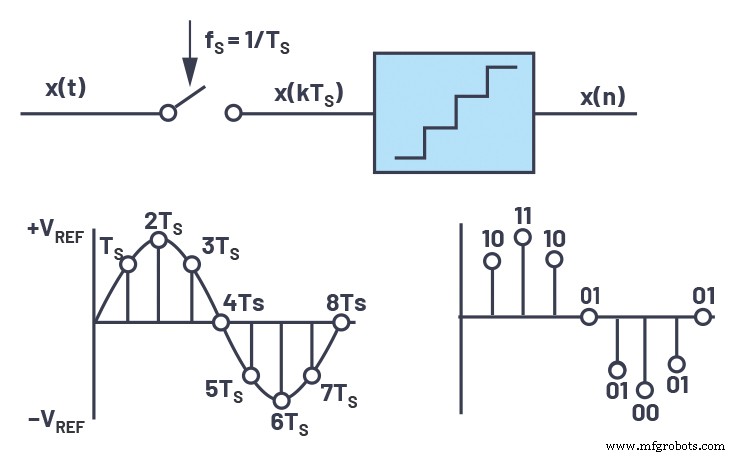

データのデジタル化には、図1に示すように、サンプリングと量子化の2つの基本的なプロセスが含まれます。サンプリングは、サンプリングを使用して連続時間変化するアナログ信号x(t)を離散時間信号x(n)に変換する最初のステップです。周波数fS。結果は、1 / TS(fS =1 / TS)の期間で均等に区切られます。

クリックすると拡大画像が表示されます

図1.データのサンプリング。 (出典:Analog Devices)

2番目のステップは量子化です。これは、これらの離散時間サンプルの値を可能な有限値の1つに近似し、図1に示すように、デジタルコードで表されます。値の有限セットへのこの量子化は、と呼ばれるデジタル化のエラーにつながります。量子化ノイズ。

サンプリングプロセスではエイリアシングも発生します。エイリアシングでは、入力信号とそのサンプル周辺の高調波からのフォールドバックが見られ、クロック周波数が保持されます。ナイキスト基準では、サンプリング周波数が信号に含まれる最高周波数の少なくとも2倍である必要があります。サンプリング周波数が最大アナログ信号周波数の2倍未満の場合、エイリアシングと呼ばれる現象が発生します。

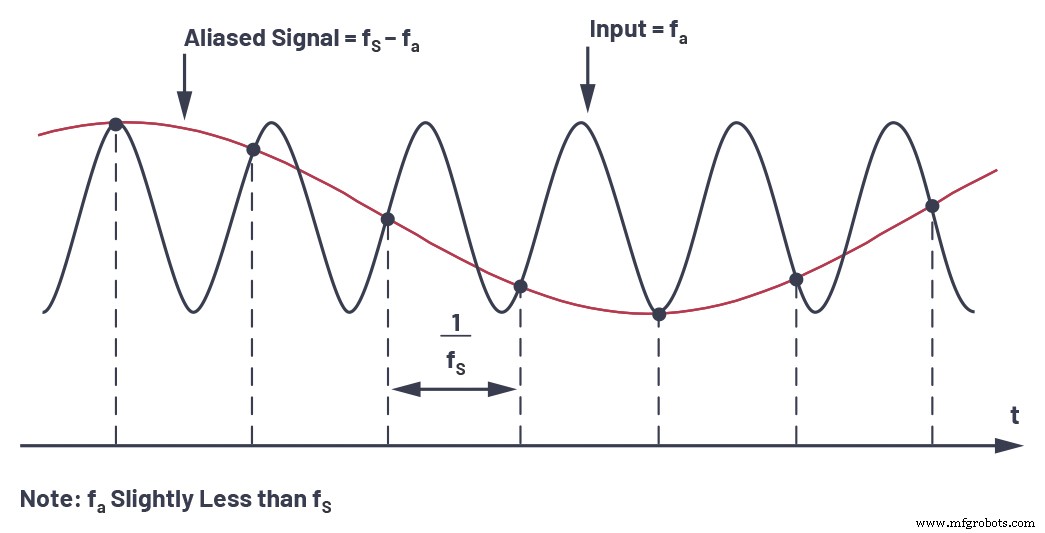

時間領域と周波数領域の両方でのエイリアシングの影響を理解するために、最初に、図2に示すようにサンプリングされたシングルトーン正弦波の時間領域表現の場合を考えます。この例では、サンプリング周波数fSは少なくとも2faですが、アナログ入力周波数faよりわずかに高いため、ナイキスト基準を満たしていません。実際のサンプルのパターンは、fS –faに等しい低周波数でエイリアシングされた正弦波を生成することに注意してください。

クリックすると拡大画像が表示されます

図2.エイリアシング:時間領域での表現。 (出典:Analog Devices)

クリックすると拡大画像が表示されます

図3.エイリアシング:周波数領域での表現。 (出典:Analog Devices)

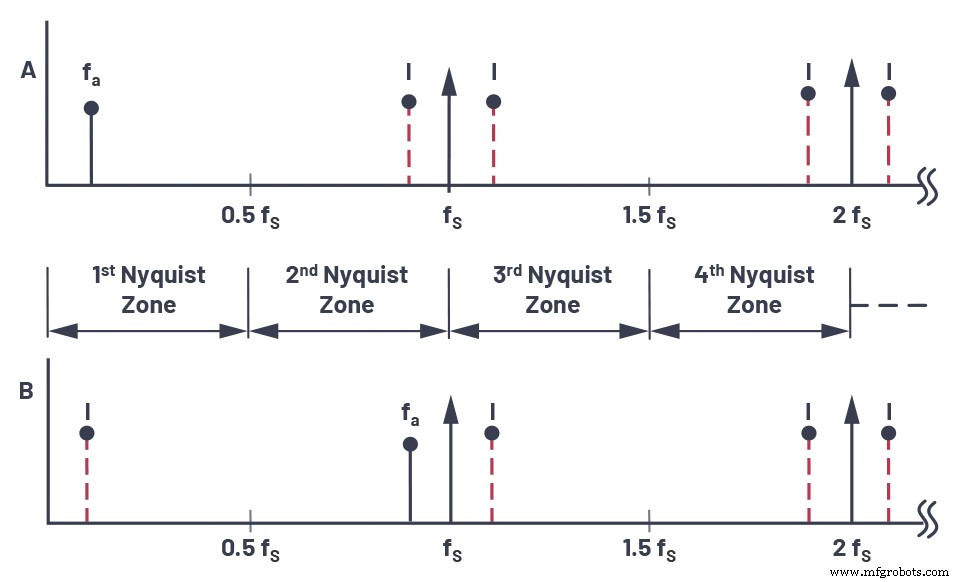

このシナリオの対応する周波数領域の表現を図3に示します。

ナイキスト帯域幅は、DCからfS / 2までの周波数スペクトルとして定義されます。周波数スペクトルは、それぞれが0.5fSに等しい幅を持つ無数のナイキストゾーンに分割されます。実際には、理想的なサンプラーはADCに置き換えられ、その後にFFTプロセッサが続きます。 FFTプロセッサは、DCからfS / 2への出力のみを提供します。つまり、最初のナイキストゾーンに表示される信号またはエイリアスです。

理想的なインパルスサンプラーによって周波数fSでサンプリングされた周波数faの単一周波数正弦波の場合を考えてみます(図1を参照)。また、fS> 2faであると仮定します。サンプラーの周波数領域出力には、fSの倍数ごとの元の信号のエイリアスまたは画像が表示されます。つまり、|に等しい周波数で±KfS±fa |、K =1、2、3、4など。

ここで、図3の最初のナイキストゾーンの外側にある信号の場合を考えます。信号周波数は、図2の時間領域表現に示されている条件に対応して、サンプリング周波数よりわずかに低いだけです。信号は最初のナイキストゾーンの外側にあり、そのイメージ(またはエイリアス)fS –faは内側にあります。図3に戻ると、faの画像周波数のいずれかで不要な信号が発生した場合、それはfaでも発生し、それによって最初のナイキストゾーンにスプリアス周波数成分が生成されることは明らかです。

高精度のパフォーマンスのための課題との戦い

高性能アプリケーションの場合、システム設計者は、サンプリングプロセスに起因する量子化ノイズ、エイリアシング、およびスイッチトキャパシタ入力サンプリングの問題に対処する必要があります。どちらのタイプの高精度ADC、つまり、業界で利用可能な逐次比較レジスタ(SAR)とシグマデルタADCは、スイッチトキャパシタベースのサンプリング技術を使用して設計されています。

量子化ノイズ

理想的なナイキストADCでは、ADCのLSBサイズによって、アナログからデジタルへの変換中に入力に追加される量子化ノイズが決まります。この量子化ノイズは、fS / 2の帯域幅に広がります。量子化ノイズに対抗するための最初の手法は、オーバーサンプリングです。これは、ナイキスト周波数よりもはるかに高いレートで入力信号をサンプリングして、信号対ノイズ比(SNR)と分解能(ENOB)を向上させます。オーバーサンプリングでは、サンプリング周波数はナイキスト周波数のN倍(2×fIN)になるように選択され、その結果、同じ量子化ノイズがナイキスト周波数のN倍に広がる必要があります。これにより、アンチエイリアシングフィルターの要件も緩和されます。オーバーサンプリング比(OSR)は、fS / 2fINとして定義されます。ここで、fINは対象の信号BWです。一般的なガイドラインとして、ADCを4倍オーバーサンプリングすると、解像度が1ビット増えるか、ダイナミックレンジが6dB増加します。オーバーサンプリング比を大きくすると、全体的にノイズが減少し、オーバーサンプリングによるダイナミックレンジ(DR)の改善はΔDR=10log10 OSR(dB)です。

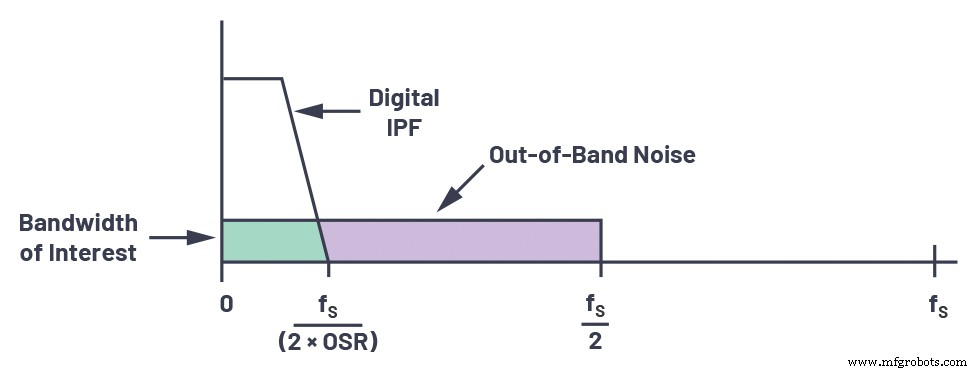

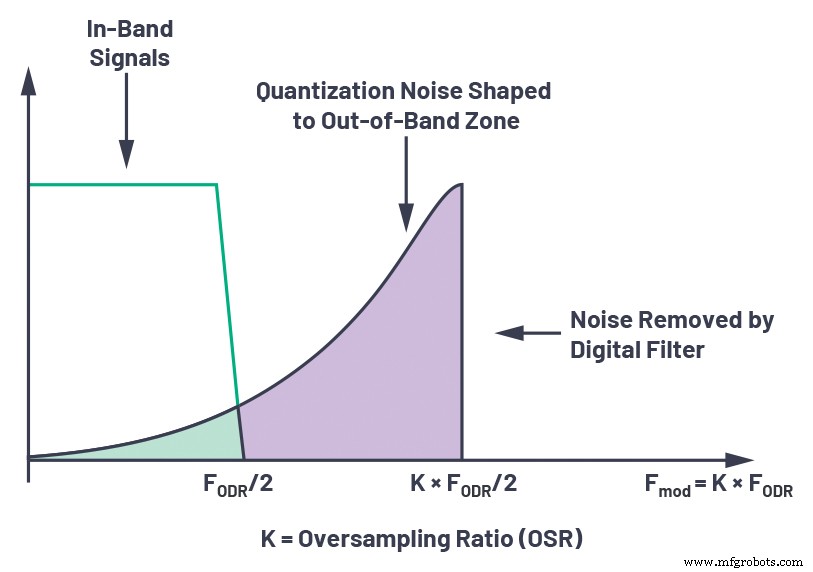

オーバーサンプリングは本質的に使用され、統合されたデジタルフィルターおよびデシメーション機能とともに実装されます。シグマデルタADCの基本的なオーバーサンプリング変調器は、量子化ノイズを整形して、そのほとんどが対象の帯域幅の外側で発生するようにします。その結果、図4に示すように、低周波数での全体的なダイナミックレンジが増加します。デジタルローパスフィルター(LPF )次に、対象の帯域幅外の量子化ノイズを除去し、デシメータは出力データレートをナイキストレートに戻します。

クリックすると拡大画像が表示されます

図4.オーバーサンプリングの例。 (出典:Analog Devices)

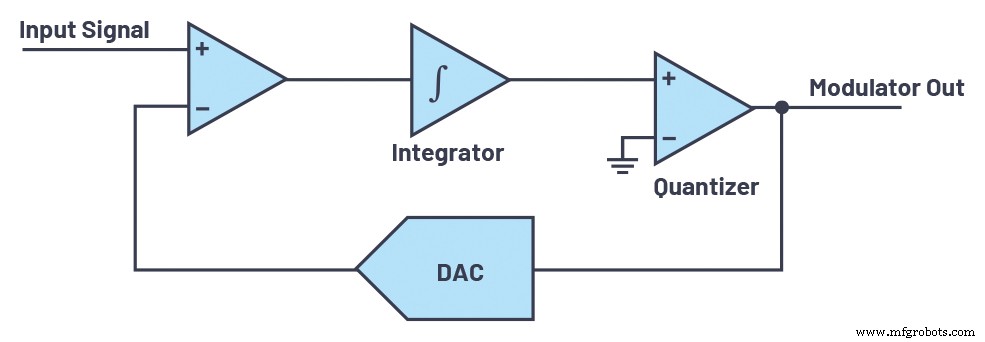

ノイズシェーピングは、量子化ノイズを低減するためのもう1つの手法です。シグマデルタADCでは、ループフィルタの後のループ内で低分解能量子化器(1ビットから5ビット)が使用されます。図5に示すように、DACは、入力から量子化された信号を差し引くためのフィードバックとして使用されます。

クリックすると拡大画像が表示されます

図5.ノイズシェーピング。 (出典:Analog Devices)

積分器は量子化誤差を合計し続けるため、量子化ノイズがより高い周波数に整形され、デジタルフィルターを使用してフィルター処理できます。図6は、一般的なシグマデルタADCの出力x [n]のパワースペクトル密度(PSD)を示しています。ノイズシェーピングスロープは、ループフィルターH(z)の次数に依存し(図11を参照)、(20×n)dB / decadeです。ここでnはループフィルターの次数です。シグマデルタADCは、ノイズシェーピングとオーバーサンプリングの組み合わせにより、高分解能の帯域内を実現します。帯域内帯域幅はfODR / 2に等しくなります(ODRは出力データレートを表します)。ループフィルターの次数を増やすか、オーバーサンプリング比を上げると、より高い解像度を得ることができます。

クリックすると拡大画像が表示されます

図6.オーバーサンプリングとノイズシェーピングのプロット。 (出典:Analog Devices)

エイリアシング

高性能アプリケーションでエイリアシングに対抗するために、高次のアンチエイリアシングフィルターを使用してフォールドバックを回避します。アンチエイリアシングフィルターは、入力信号の帯域幅を制限し、フォールドバックできる対象の帯域幅を超える信号の周波数成分がないことを保証するローパスフィルターです。フィルタのパフォーマンスは、帯域外信号がfS / 2にどれだけ近いか、および必要な減衰量によって異なります。

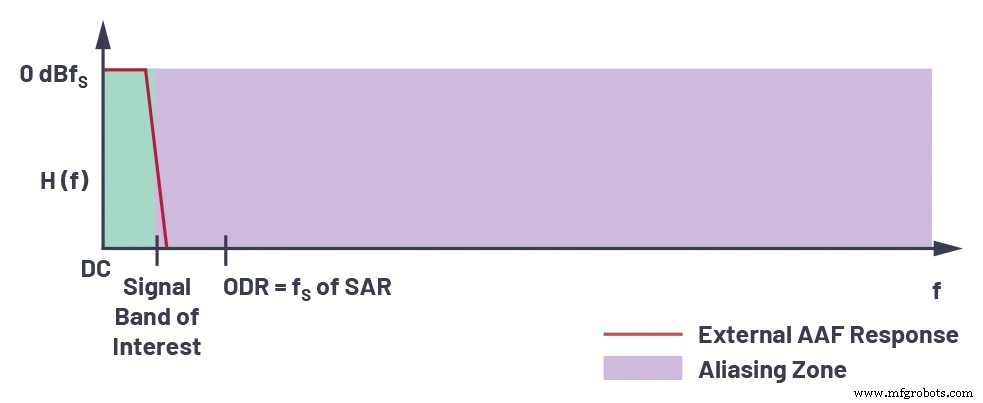

SAR ADCの場合、入力信号BWとサンプリング周波数の間のギャップは大きくないため、より多くの電力と歪みを備えた複雑で高次のフィルター設計を必要とする高次フィルターが必要です。たとえば、200kSPSのサンプリング速度SARの入力帯域幅が100kHzの場合、アンチエイリアシングフィルターは、エイリアシングがないことを確認するために、100kHzを超える入力信号を拒否する必要があります。これには、非常に高次のフィルターが必要です。図7は、急勾配の需要を示しています。

クリックすると拡大画像が表示されます

図7.エイリアス要件。 (出典:Analog Devices)

フィルタの次数を緩和するために400kSPSのサンプリング速度を選択した場合、300kHzを超える入力周波数に対して除去が必要になります。サンプリング速度を上げるとパワーが上がり、2倍の速度の場合はパワーも2倍になります。サンプリング周波数は入力帯域幅よりもはるかに高いため、電力を犠牲にしてさらにオーバーサンプリングすると、アンチエイリアシングフィルターの要件がさらに緩和されます。

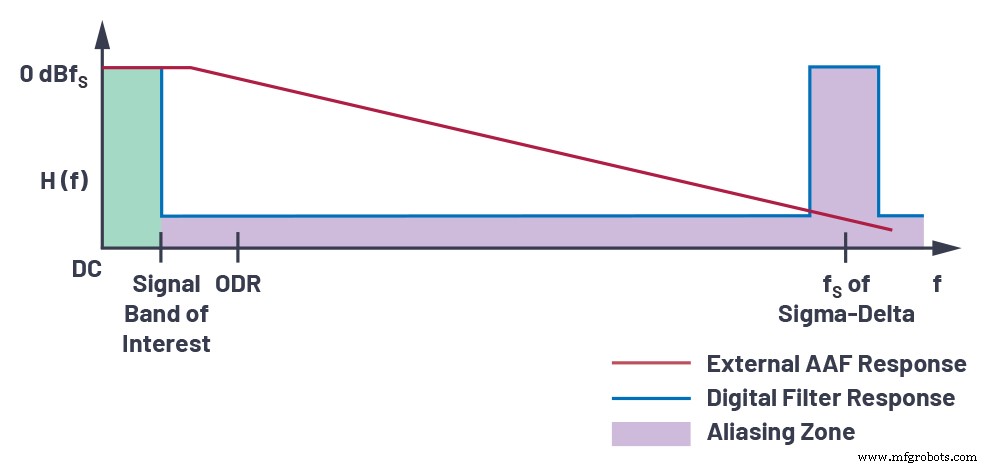

シグマデルタADCでは、入力ははるかに高いOSRでオーバーサンプリングされるため、図8に示すように、サンプリング周波数が入力BWよりもはるかに高いため、アンチエイリアシングフィルターの要件が緩和されます。

クリックすると拡大画像が表示されます

図8.シグマデルタのアンチエイリアシングフィルター要件。 (出典:Analog Devices)

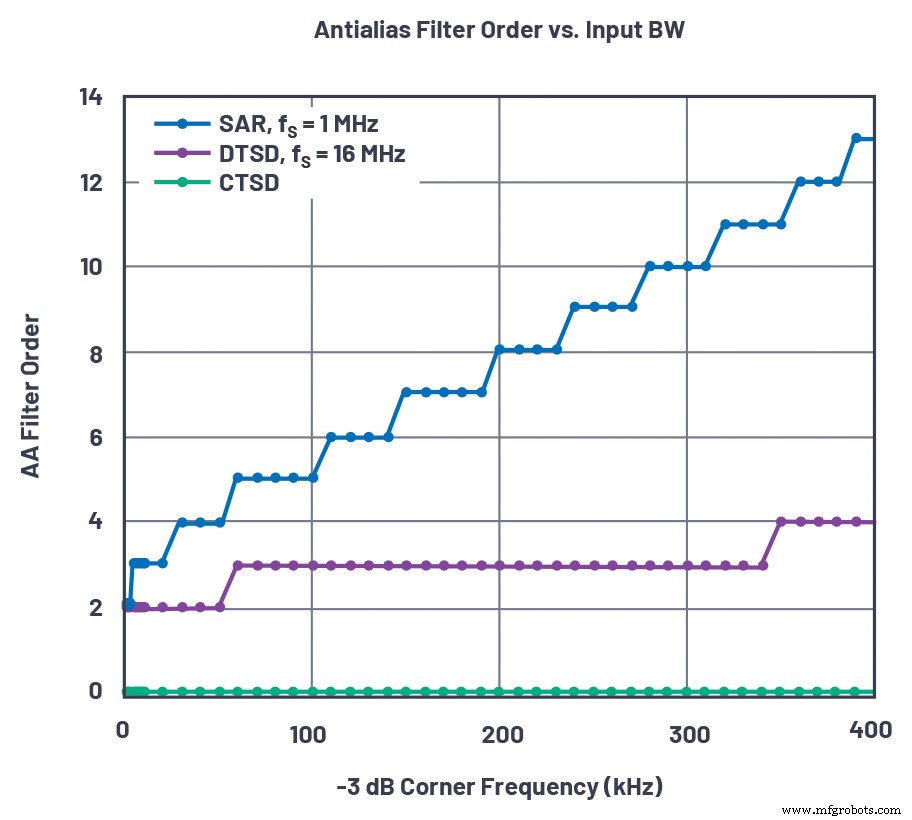

図9は、SARおよび離散時間シグマデルタ(DTSD)アーキテクチャのAAFの複雑さを示しています。サンプリング周波数fSで102dBの減衰を達成するために100kHzの–3 dB入力帯域幅を使用する場合、DTSD ADCには2次アンチエイリアシングフィルターが必要ですが、fSで同じ減衰を得るには、 SARADC。

連続時間シグマデルタ(CTSD)ADCの場合、減衰は固有であるため、アンチエイリアシングフィルターは必要ありません。

クリックすると拡大画像が表示されます

図9.さまざまなアーキテクチャのAAFフィルター要件。 (出典:Analog Devices)

これらのフィルターは、システム設計者にとって問題となる可能性があり、対象の帯域で提供する垂下に合わせてフィルターを最適化し、可能な限り多くの拒否を提供する必要があります。また、オフセット、ゲイン、位相エラー、ノイズなどの他の多くのエラーがシステムに追加されるため、システムのパフォーマンスが低下します。

また、高性能ADCは本質的に差動であるため、2倍の数の受動部品が必要です。マルチチャネルアプリケーションでより良い位相整合を得るには、信号チェーン内のすべてのコンポーネントが適切に整合する必要があります。その結果、より厳しい公差のコンポーネントが必要になります。

スイッチトキャパシタ入力

スイッチトキャパシタ入力サンプリングは、コンデンサへのサンプリング入力の整定時間に依存しており、サンプリングスイッチがオン/オフになったときに過渡電流を充電/放電する必要があります。これは入力のキックバックと呼ばれ、これらの過渡電流をサポートできる入力駆動アンプを必要とします。また、入力はサンプリング時間の終わりに整定する必要があり、サンプリングされた入力の精度がADCの性能を決定します。これは、駆動アンプがキックバックイベントの直後に整定する必要があることを意味します。これにより、高速セトリングをサポートし、スイッチトキャパシタ動作のキックバックを吸収できる高帯域幅ドライバが必要になります。スイッチトキャパシタ入力では、サンプリングがオンになると、ドライバはすぐにホールドコンデンサの電荷を供給しなければなりません。この突然の電流の急増は、ドライバーに十分な帯域幅機能がある場合にのみ時間内に提供できます。スイッチの寄生により、サンプリング時にドライバーにキックバックが発生します。次のサンプリングの前にキックバックが安定しない場合、サンプリング中にエラーが発生し、ADC入力が破損します。

クリックすると拡大画像が表示されます

図10.サンプリングキックバック。 (出典:Analog Devices)

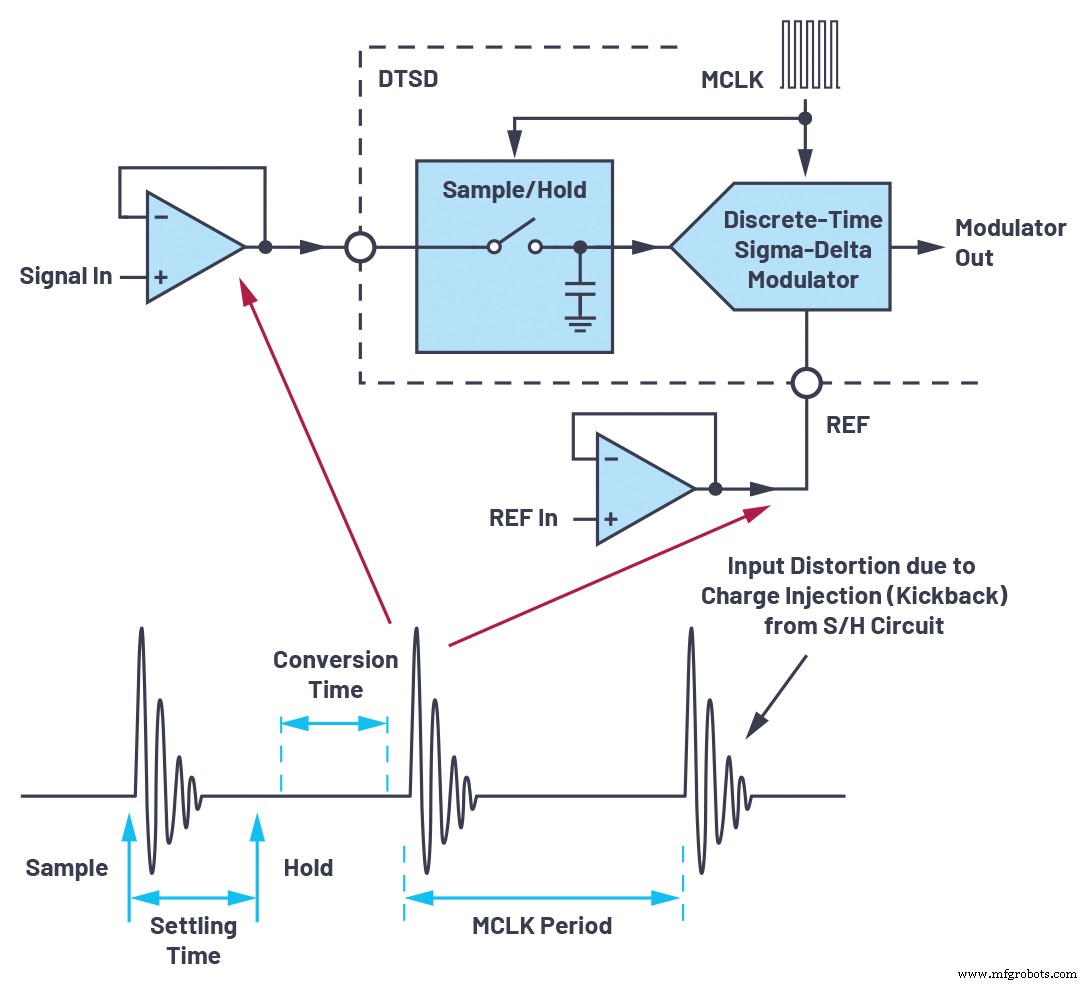

図10は、DTSDADCのキックバックを示しています。たとえば、サンプリング周波数が24 MHzの場合、データ信号は41ns以内に安定する必要があります。リファレンスはスイッチトキャパシタ入力でもあるため、リファレンス入力ピンにも高帯域幅のバッファが必要です。これらの入力信号とリファレンスバッファはノイズを増加させ、信号チェーンの全体的なパフォーマンスを低下させます。さらに、入力信号ドライバからの歪み成分(S&H周波数付近)により、アンチエイリアシング要件がさらに追加されます。また、スイッチトキャパシタ入力では、サンプリング速度を変更すると入力電流が変化します。これにより、ADCの駆動中にドライバーまたは前のステージで発生するゲインエラーを減らすために、システムが再調整される可能性があります。

連続時間シグマ-デルタADC

CTSD ADCは、オーバーサンプリングやノイズシェーピングなどの原理を利用する代替のシグマデルタADCアーキテクチャですが、システムに大きなメリットをもたらすサンプリング操作を実装する代替手段があります。

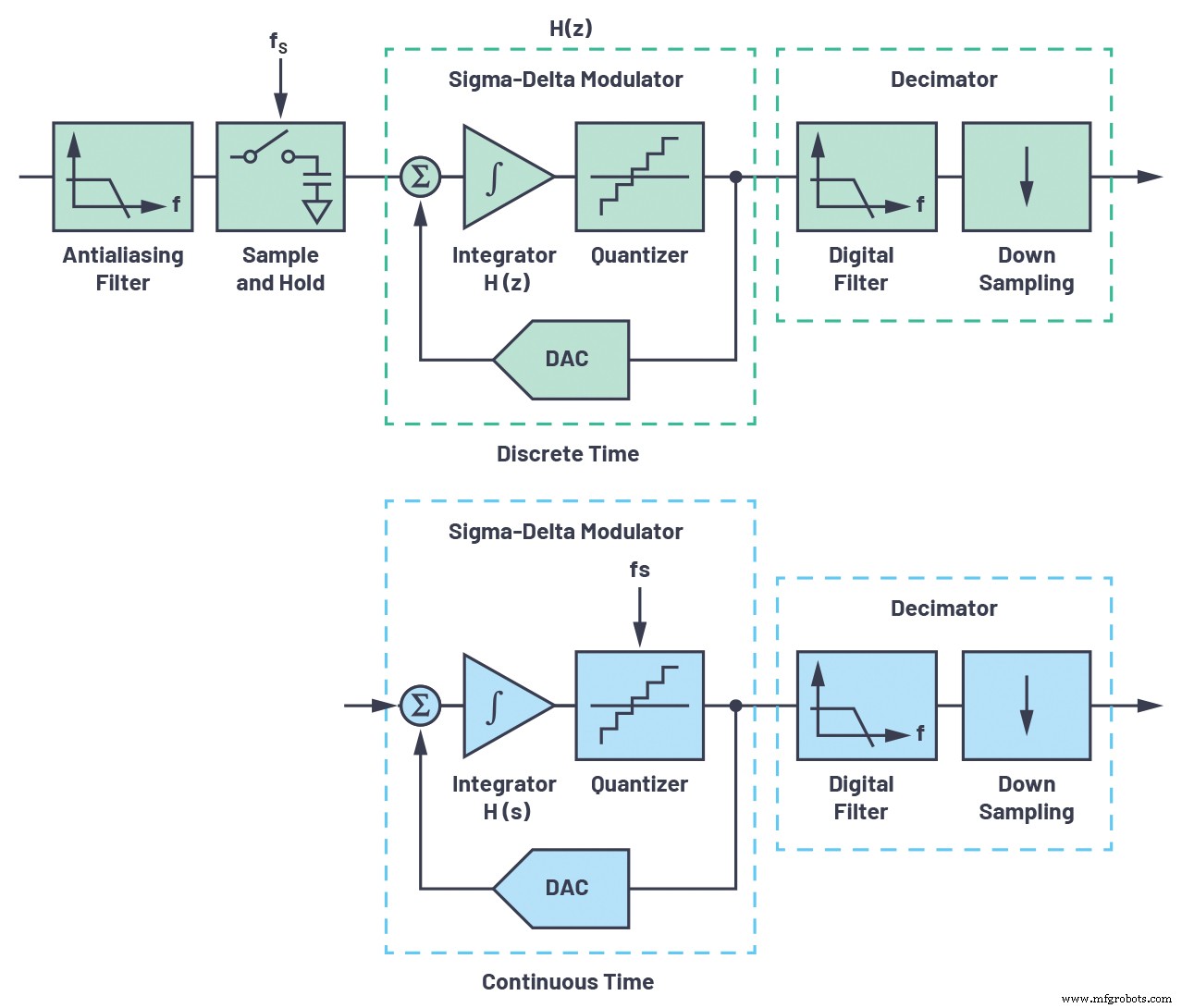

図11に、DTSDアーキテクチャとCTSDアーキテクチャの比較を示します。 DTSDアーキテクチャで見られるように、入力はループの前にサンプリングされます。ループフィルタH(z)は時間的に離散的であり、スイッチトキャパシタ積分器を使用して実装されます。フィードバックDACもスイッチトキャパシタベースです。入力にサンプリングがあるため、f S からのエイリアシングの問題が発生します。 、サンプリングする前に、入力に追加のアンチエイリアシングフィルターが必要です。

クリックすると拡大画像が表示されます

図11.離散時間および連続時間のモジュラーブロックの回路図。 (出典:Analog Devices)

CTSDには入力にサンプラーがありません。むしろ、ループ内の量子化器でサンプリングされます。ループフィルターは、連続時間積分器を使用した連続時間であり、フィードバックDACも同様です。整形される量子化と同様に、サンプリングによるエイリアシングも整形されます。これにより、ほとんどサンプリングされないADCが生成され、独自のクラスが作成されます。

変調器のサンプリング周波数を簡単にスケーリングできるDTSDとは異なり、CTSDのサンプリング周波数は固定されています。また、CTSD ADCは、スイッチトキャパシタの同等品よりもジッターに対する耐性が低いことが知られています。既製の水晶またはCMOS発振器は、ADCにローカルで低ジッタークロックを提供します。これにより、アイソレーションを介した低ジッタークロックの送信を回避し、EMCを削減できます。

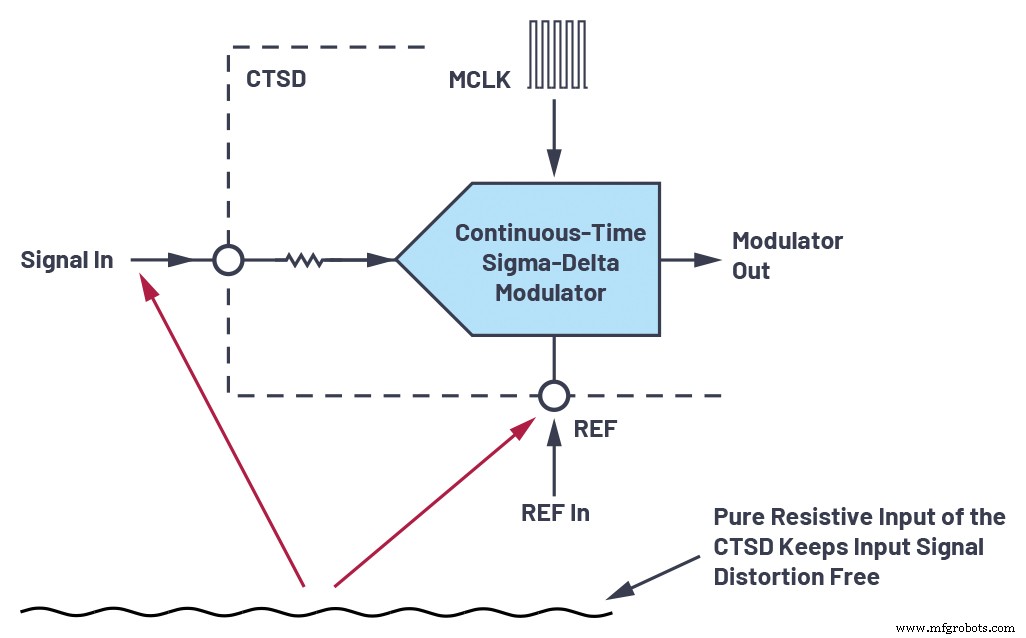

CTSDの2つの主な利点は、固有のエイリアス除去と、信号およびリファレンスの抵抗入力です。

固有のアンチエイリアス

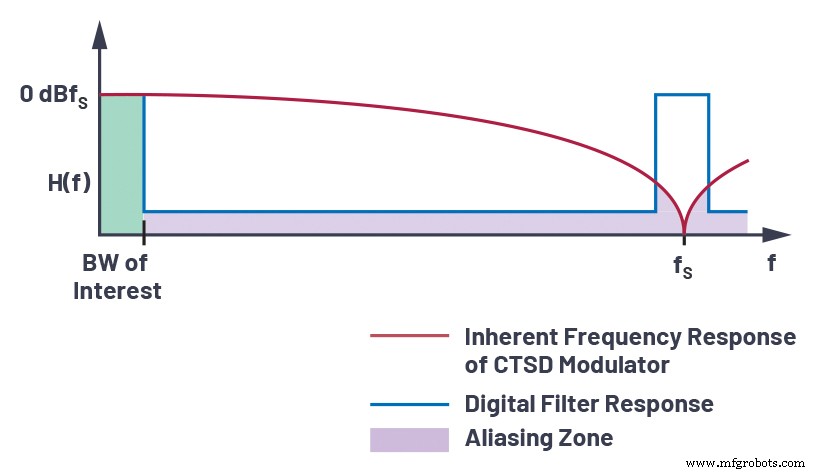

量子化器をループ内に移動すると、固有のエイリアスが拒否されます。図12に示すように、入力信号はサンプリングされる前にループフィルターを通過し、量子化器で導入されるフォールドバック(エイリアス)エラーもこのフィルターを認識します。信号とエイリアスエラーは、シグマデルタループと同じノイズ伝達関数を示し、どちらもシグマデルタアーキテクチャの量子化ノイズと同様のノイズシェーピングを持ちます。したがって、CTSDループの周波数応答は、サンプリング周波数の整数倍の入力信号を自然に拒否し、アンチエイリアシングフィルターとして機能します。

クリックすると拡大画像が表示されます

図12.CTSD変調器の周波数応答。 (出典:Analog Devices)

抵抗入力

信号入力とリファレンス入力に抵抗入力があると、サンプルアンドホールド構成よりも駆動が容易になります。一定の抵抗入力を使用すると、キックバックがなく、ドライバーを完全に取り外すことができます。図13に示すように、入力には歪みがありません。また、入力抵抗が一定であるため、ゲインエラーに対するシステムの再調整も排除されます。

クリックすると拡大画像が表示されます

図13.CTSDの入力セトリング。 (出典:Analog Devices)

ADCにユニポーラ電源がある場合でも、アナログ入力はバイポーラにすることができます。これにより、バイポーラフロントエンドからADCへのレベルシフトの必要がなくなります。 ADCのDC性能は、入力抵抗に入力コモンモード依存電流と入力電流があるのと同じではない場合があります。

リファレンス負荷も抵抗性であるため、スイッチングキックバックが減少するため、個別のリファレンスバッファは必要ありません。ローパスフィルターの抵抗はオンチップで作成できるため、オンチップの抵抗性負荷(同じ材料である可能性があるため)と一緒に追跡できるため、ゲインエラーの温度ドリフトを低減できます。

CTSDアーキテクチャは新しいものではありませんが、産業および計装市場のメガトレンドでは、より高い帯域幅でDCおよびACの高精度性能が求められています。さらに、顧客は、市場投入までの時間を短縮するために、ほとんどのソリューションに対応できる単一のプラットフォーム設計を好みます。

CTSDアーキテクチャは、他のタイプのADCに比べて多くの利点があるため、高性能オーディオからセルラーハンドセットRFフロントエンドに至るまでの幅広いアプリケーションで選択されてきました。利点には、統合の快適性の向上と低消費電力が含まれますが、CTSDを使用するとシステムレベルの重要な問題が多数解決されるため、さらに重要なこともあります。多くの技術的な欠点のため、CTSDの使用は、以前は相対的な可聴周波数/帯域幅とより低いダイナミックレンジに制限されていました。したがって、逐次比較型ADCやオーバーサンプリングされたDTSDコンバーターなどの高性能ナイキストレートコンバーターは、高精度、高性能/中帯域幅アプリケーションの主流ソリューションとなっています。

ただし、最近の技術革新により、多くの制限を克服できるようになりました。たとえば、Analog DevicesのAD7134は、CTSDに基づく高精度のDCから400 kHzの帯域幅のADCをサポートします。これにより、DCの精度が向上し、システムレベルの重要な問題の解決が可能になります。パフォーマンス計測アプリケーション。 AD7134は、CTSDの固定サンプリング速度から得られる可変データレートでデータを提供する非同期サンプルレートコンバーター(ASRC)も統合しています。出力データレートは、変調器のサンプリング周波数に依存せず、さまざまなきめ細かいスループットでCTSDADCを正常に使用できます。出力データレートをきめ細かく変更できる柔軟性により、ユーザーはコヒーレントサンプリングを使用することもできます。

固有のエイリアス拒否により、アンチエイリアシングフィルターが不要になり、コンポーネントが少なくなり、ソリューションサイズが小さくなります。さらに重要なことに、ドループなどのアンチエイリアシングフィルター、オフセット、ゲイン、位相エラーなどのエラー、およびシステムのノイズに伴うパフォーマンスの問題がなくなりました。アンチエイリアシングフィルターは、必要な除去に応じて、信号チェーンの全体的な遅延を大幅に増加させます。フィルタを削除すると、この遅延が完全に除去され、ノイズの多いデジタル制御ループアプリケーションでの正確な変換が可能になります。

システムレベルでアンチエイリアシングフィルターがないため、マルチチャネルシステムの位相整合を大幅に改善できます。これは、振動監視、電力測定、データ取得モジュール、ソナーなど、チャネル間の不一致が少ないアプリケーションで特に役立ちます。 CTSD ADCは、固有のフィルタリング動作により、IC自体の内部からだけでなく、システムレベルでのあらゆる種類の干渉の影響を受けません。 DTSDADCおよびSARADCでは、ADCがサンプリングしているときの干渉が少なくなるように注意する必要があります。また、固有のフィルタリング動作により、電源ラインへの干渉の影響を受けません。定抵抗アナログ入力とリファレンス入力を使用すると、ドライバ要件も完全に取り除くことができます。繰り返しになりますが、これにより、オフセット、ゲイン、位相エラー、システムへのノイズなどのパフォーマンスの問題が解消されます。

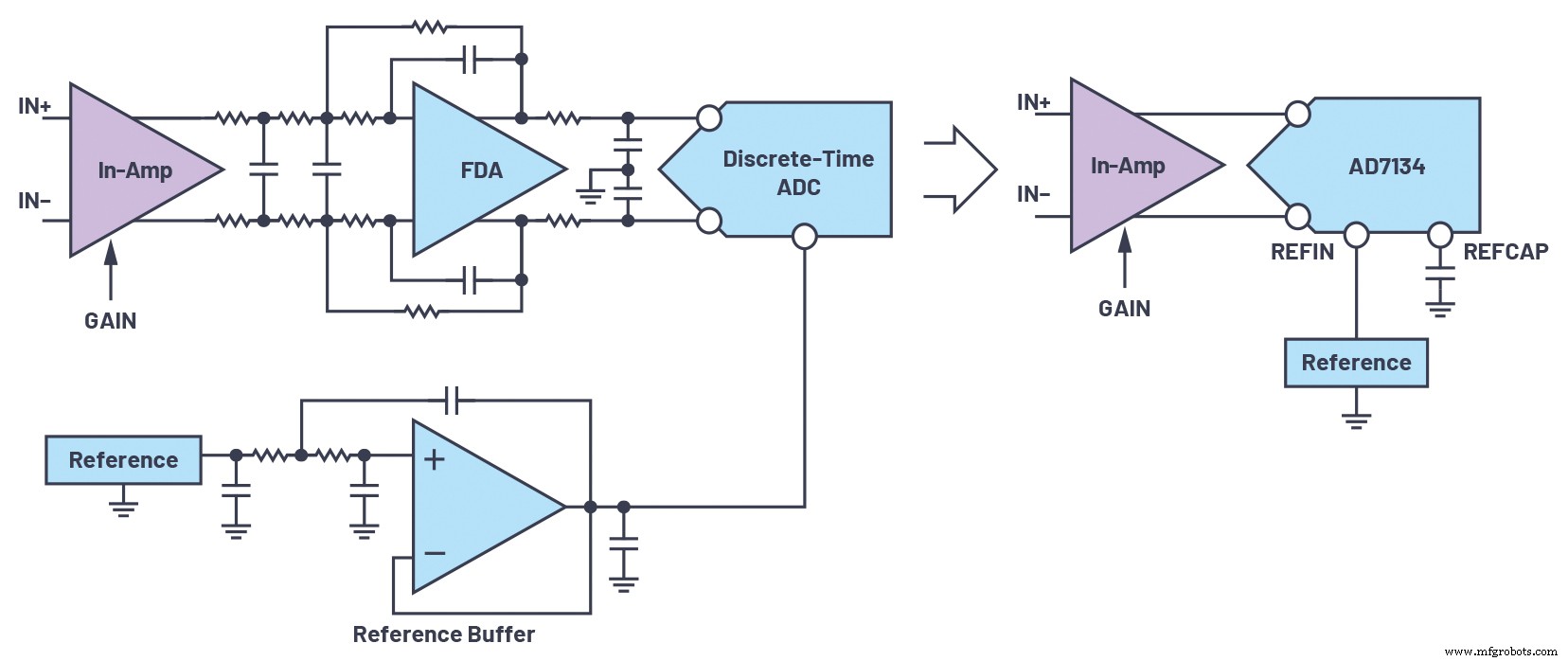

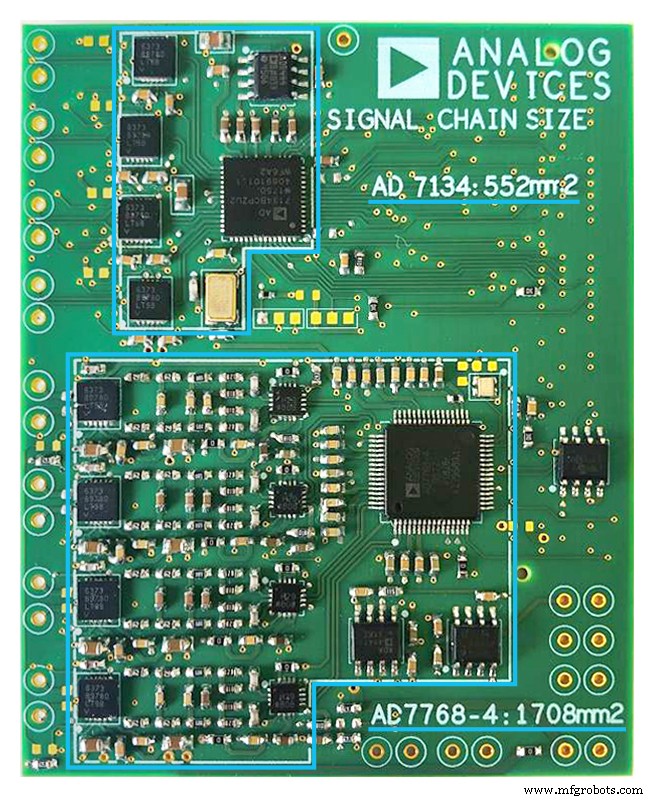

設計された要素の数が大幅に削減されるため、高精度のパフォーマンスを実現するための苦労はごくわずかです。これにより、設計時間の短縮、顧客への市場投入までの時間の短縮、BOM管理の容易化、および信頼性が実現します。アンチエイリアシングフィルター、ドライバー、およびリファレンスバッファーを削除すると、システムボードの面積が大幅に削減されます。計装アンプを使用して、ADCを直接駆動できます。たとえば、AD7134では差動入力のみのADCであるため、LTC6373などの差動インアンプをドライバとして使用できます。図14の比較は、離散時間ベースの信号チェーンと連続時間ベースの信号チェーンの信号チェーンを示しています。私たちの実験では、同等の離散時間ベースの信号チェーンと比較した場合、面積が70%節約されることが示されているため、高密度マルチチャネルアプリケーションに最適です。

結論として、このアプローチは、システムサイズを大幅に削減し、シグナルチェーンの設計を簡素化し、システムをより堅牢にし、精密計装アプリケーションに必要なパフォーマンスパラメータを交換することなく、簡単な設計で市場投入までの時間を短縮します。

クリックすると拡大画像が表示されます

図14.離散時間ベース(左)と連続時間ベース(右)のシグナルチェーンの比較。 (出典:Analog Devices)

クリックすると拡大画像が表示されます

図15.離散時間と連続時間の信号チェーンのサイズ比較。 (出典:Analog Devices)

参照

ケスター、ウォルト。 「MT-002:ナイキスト基準がサンプルデータシステム設計に意味するもの。」 Analog Devices、Inc.、2009年。

パヴァン、シャンティ。 「スイッチトキャパシタフィードバックDACを備えた連続時間Δ∑変調器のエイリアス除去。」 IEEE Transactions on Circuits and Systems I:Regular Papers 、Vol。 58、No。2、2011年2月。

シュライアー、リチャード、ガボールC.テメス。 デルタシグマデータコンバータについて理解する。 John Wiley and Sons、2005年。

謝辞

著者は、この記事をサポートしてくれたAbhilasha Kawle、Avinash Gutta、RobertoMaurinoに感謝します。

埋め込み

- デジタルメモリの用語と概念

- C# 変数と (プリミティブ) データ型

- Python の型変換と型キャスト

- セマフォ:ユーティリティサービスとデータ構造

- イベントフラググループ:ユーティリティサービスとデータ構造

- Apacer:世界中で発売されたCV110-SDおよびCV110-MSDカード

- Swissbit:データとデバイスを保護するためのハードウェアベースのセキュリティソリューション

- ハイパーコンバージェンスとセカンダリストレージ:パート2

- 責任ある信頼できるAIの構築

- ブロックチェーンとサプライチェーン:可能性を解き放つ

- データファブリックの意味—およびそれらがサプライチェーンにどのように役立つか