パワーアップフェーズの決定論:マルチチップ同期の使用

複数のデジタル信号処理(DSP)ブロック、広帯域デジタル-アナログコンバーター(DAC)、および広帯域アナログ-デジタルコンバーター(ADC)を単一のモノリシックチップに統合することで、電力を大量に消費するFPGAリソースのオフロードが可能になります。以前に達成可能であったよりも高いレートでサンプリングできる、より小さなフットプリント、より低い電力、より多くのチャネル数のプラットフォームを可能にします。この新機能に加えて、これらの集積回路(IC)内に新しいマルチチップ同期(MCS)アルゴリズムが搭載されています。これにより、ユーザーは、システムに電力を供給したり、システムにソフトウェアを変更したりするときに、すべてのチャネルの既知の(決定論的)フェーズを実現できます。したがって、この決定論的フェーズは、これらのICに接続されたフロントエンドネットワークへの出力または入力ですべてのチャネルの同期を実現するために必要な、より広範なシステムレベルのキャリブレーションアルゴリズムを簡素化します。この記事では、複数のデジタイザーIC、クロックソース、およびデジタルインターフェイスで構成される16チャネルの受信機/送信機プラットフォームを使用した場合のこのMCS機能を実証する実験結果を紹介します。

高レベルのシステムブロック図

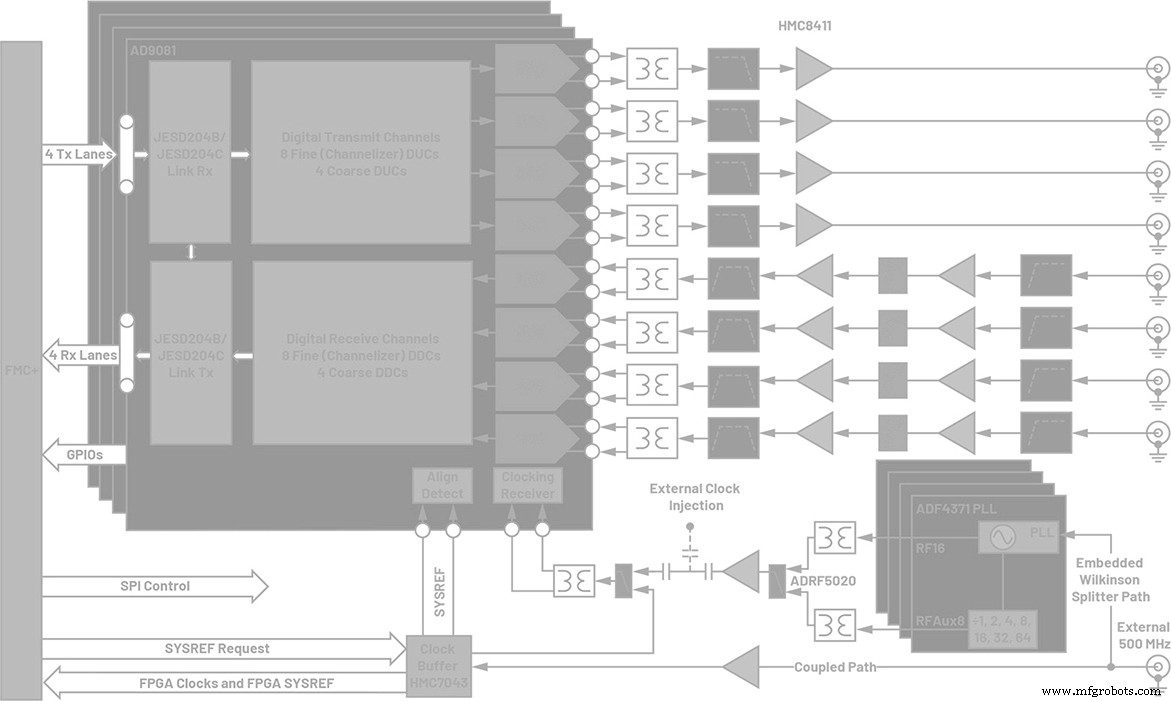

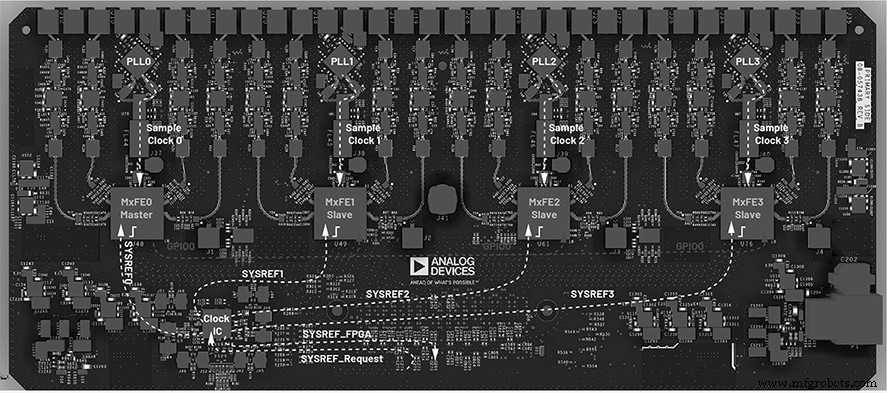

このテストに使用したシステムのブロック図を図1に示します。これは、4つの統合DAC / ADC / DSP ICで構成され、それぞれが4つの12 GSPS DAC、4つの4 GSPS ADC、および12のデジタルアップコンバーター(DUC)と12のデジタルで構成されています。ダウンコンバータ(DDC)ブロック。

クリックしてフルサイズの画像を表示

図1.MCSおよびマルチチャネルキャリブレーションアルゴリズムのデモンストレーションに使用されるシステムの高レベルのブロック図。 (出典:Analog Devices)

DUC / DDCは、デジタルドメイン内での周波数変換および/または補間/デシメーションを可能にします。次に、ボードに注入された単一の500 MHz基準クロックを使用して、基準ロッククロックバッファを使用して、MCSに必要なシステム基準信号とベースバンドプロセッサ(BBP)へのデジタルインターフェイスに必要なクロックを生成します。このシステムには、共通のリファレンスから各デジタル化ICをクロックするために必要な12 GHzソースを生成する4つの個別のフェーズロックループ(PLL)シンセサイザーも含まれています。 RFフロントエンドは各デジタイザの出力/入力に接続されており、エッジで起動されたRFコネクタとの間でフィルタリングおよび増幅された信号を生成します。フル配電ソリューションが実装されています。システムに必要なすべての電圧は、単一の12V電源から生成されます。すべての送信信号はボードの下部で伝播しますが、すべての受信信号はボードの上部で伝播して、最適なチャネル間分離を実現します。

サブアレイクロックツリー構造

前述のように、サブアレイクロックツリーは、上記の図1に示すように、分割されて4つの別々のPLLシンセサイザーICのリファレンス入力に送信される単一の500 MHzリファレンスソースで構成されます。この500MHz信号も10dB結合され、増幅されます。 、およびデジタルインターフェイスに必要なシステムリファレンス(SYSREF)とBBPクロックの生成を担当する別のクロックバッファICに送信されます。この時計ツリーの目標は、次の3つです。

- 個々のチャネルのSYSREF遅延により、IC間のトレース長の不一致を修正できます。

- 個々のPLL /シンセサイザーの位相調整を許可するため、システム内で誘発される温度勾配を補正するために、それぞれのデジタイザーICクロックソース間での同期が保証されます。

- ユーザーがデジタル化ICに必要なセットアップとホールドの要件を達成できるようにします。

クロックツリーICは、これらのチップ内に存在するデジタルおよびアナログの遅延ブロックを使用して、ソフトウェアやハードウェアでさまざまなボードレイアウトの異常を修正できることを示すために選択されています。最終的には、これらの各ICの同じサンプルクロックサイクル内で必要なすべてのICにSYSREFパルスを提供できるクロックツリーが得られます。

ベースバンドプロセッサを備えたデジタルインターフェース

4つのデジタル化ICはそれぞれ、BBPとのJESD204BまたはJESD204Cデジタルリンクインターフェイスを確立します。 1,2 このインターフェースは、物理トレース(SERDES)を介してBBPとの間でADCおよびDACコードを送信する役割を果たします。このインターフェイスで使用される差動SERDESトレースの数は、このリンクのレーン数(L)と呼ばれます。リンクを介して送信されるコンバータのビット解像度はN ’と見なされます。チャネライズドデータパスの数(これも造られた仮想コンバーター)はMとラベル付けされています。この記事に示す結果は、DAC側リンクにM =16、N '=16、L =4、M =8のJESD204Cリンクを使用しています。 、N '=16、ADC側リンクの場合はL =2。

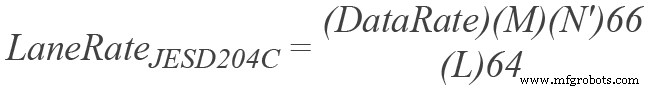

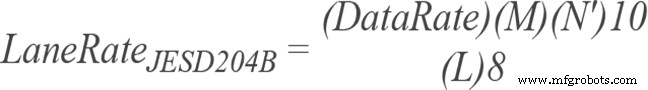

デジタイザICとBBPの間でデータが送受信されるレートは、レーンレートと呼ばれます。シリコン上のDSPブロック(つまり、DDC / DUC)を使用すると、ユーザーは、物理レーンを介して送信されるデータレートとは異なるレートでデジタイザーをサンプリングできます。そのため、レーンレートは、各データパスのデジタルデシメート/補間されたデータレートに依存します。この作業では、250 MSPS I / Qデータレートが使用されています。 JESD204Cインターフェースの場合、レーンレートは次のように定義されます。

一方、JESD204Bインターフェースの場合、レーンレートは次のように定義されます。

この記事に示されている結果では、ADC側とDAC側の両方のJESD204Cリンクに16.5Gbpsのレーンレートを使用しています。

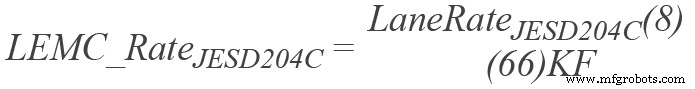

各JESD204B / JESD204Cリンクは、異なるサブクラス内で確立できます。これらのサブクラスは、マルチチップ同期または決定論的遅延が必要かどうかに基づいて分離されます。この作業では、示されているデータはJESD204Cサブクラス1モードを使用しているため、SYSREF信号を使用して、システム内に存在する複数のリンクを介して送信されるデジタルデータの一部を整列させます。具体的には、このJESD204Cサブクラス1モードでは、SYSREF信号を使用して、次の速度で送信するローカル拡張マルチブロックカウンター(LEMC)を調整します。

ここで、FはレーンごとのJESDフレームごとのオクテット数であり、Kは単一のマルチフレームごとのフレーム数です。この作業では、F =8およびK =32であるため、7.8125MSPSのLEMCレートが使用されます。 MCSルーチンを成功させるには、LEMCレートの整数倍ではないRF周波数が決定論的なパワーアップフェーズを達成できることを実証する必要があるため、このLEMCレートの知識は重要です。

マルチチップ同期方式

このシステム内で、広帯域集積ADC / DAC ICは、IC内でDUC / DDC DSPブロックを使用している場合でも、すべての送信および受信RFチャネルでパワーアップ決定論的位相を可能にするMCS回路を提供します。このMCS機能により、ユーザーは工場出荷時のキャリブレーション中にルックアップテーブル(LUT)にデータを入力して、運用上のダウンタイムを最小限に抑えることができます。 MCSのデモンストレーションを成功させるには、RF周波数、温度勾配、およびシステムの電源サイクルを試行するたびに、システム内のすべてのチャネルにわたって決定論的な位相を提供できる必要があります。

統合されたADC / DAC ICには、上記の図1に示すように、12個のDUCブロックと12個のDDCブロックが含まれます。これらの各ブロックには、DACデジタル入力信号のデータレートを変更するための補間(DUC)またはデシメーション(DDC)サブブロックが含まれます。それぞれADCデジタル化出力信号。また、各DUC / DDCには、デジタルドメイン内での周波数変換を可能にする複雑な数値制御発振器(NCO)が含まれています。これらの各NCOは、DAC / ADCとBBP間のデジタル信号を変更して、さまざまなSERDESトレース長の不一致を補正できるように、リアルタイムの複雑な位相調整が可能です。

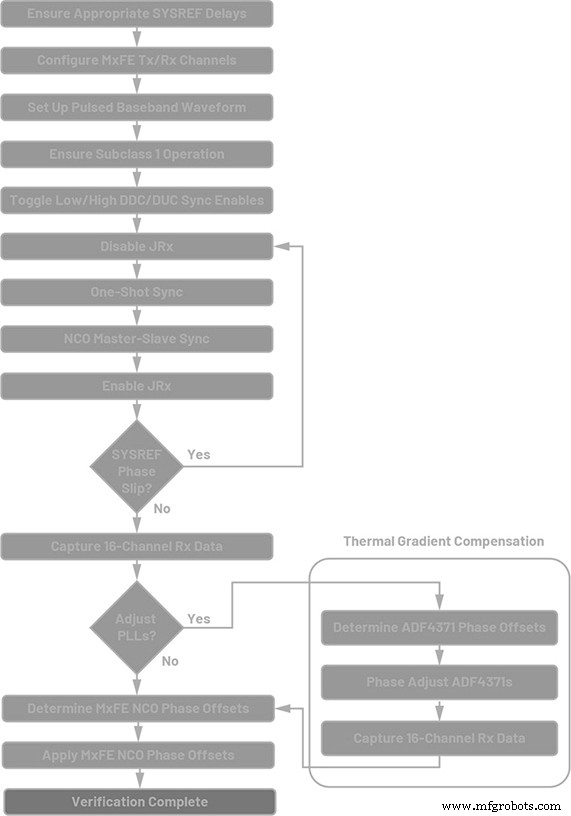

これらのADC / DAC ICのMCS機能は、デジタイザーICのデータパスのすべての側面で位相決定論を実現する役割を果たします。 MCSを実現するためのワークフローを図2に示します。

クリックしてフルサイズの画像を表示

図2.MCSワークフローには、データパスのさまざまな部分を調整する個別の機能が含まれます。 (出典:Analog Devices)

MCSアルゴリズムは、次の2つの機能に分けることができます。

- ワンショット同期:この機能は、サブアレイシステム内のすべてのデジタイザーICの物理レーンを介して送信されるベースバンドデータを調整する役割を果たします。

- NCOマスター/スレーブ同期:この機能は、サブアレイシステム内のすべての異なるデジタイザーIC全体ですべてのNCOを調整する役割を果たします。

ワンショット同期機能では、最初にユーザーがJESDリンクパラメーター(M、N ’、Lなど)を定義してから、必要なSYSREF平均化(連続SYSREFパルスを使用する場合)の同期ロジックを構成する必要があります。さらに、必要なLEMC遅延を使用して、SYSREFエッジ後の特定の遅延でLEMCを強制的に生成することができます。これが完了した後、ユーザーは各デジタイザーIC内でワンショット同期ビットを有効にし、図3に示すように、SYSREFパルスを同じクロックサイクル内で各ICに送信するように要求します。

クリックしてフルサイズの画像を表示

図3.MCSアルゴリズムは、SYSREF信号を使用してワンショット同期を実装し、GPIO信号を使用してNCOマスター/スレーブ同期を実装し、決定論的フェーズを実現します。 (出典:Analog Devices)

このシステムでは、すべてのデジタイザICへの同期SYSREFを可能にするために、クロックバッファIC内にアナログファインディレイが導入されています。後続のチェックを実行して、SYSREF信号と各ICのリンクのLEMC境界との間の位相関係に関する情報を提供する各IC内のレジスタにクエリを実行することにより、ワンショット同期プロセスが正常に実行されたことを確認できます。

安定した位相が測定されると(つまり、SYSREF-LEMC位相レジスタが0を読み取ると)、ユーザーはすべてのデジタイザーICのLEMCが整列していることを認識し、NCOマスタースレーブ同期プロセスに進むことができます。このアクティビティでは、ワンショット同期について説明したサブタスクは、チップメーカーが提供するアプリケーションプログラミングインターフェイス(API)に含まれています。

NCOマスター/スレーブ同期機能は、最初に、サブアレイ内のデジタイザーICの1つを、上記の図3に示すように、マスターチップとして機能するように割り当てます。その後、他のすべてのデジタイザーはスレーブICと見なされます。マスターICは、このデバイスのGPIO0ピンが出力として構成され、3つのスレーブデジタイザーICのGPIO0ネットにルーティングされるように設定されています。スレーブGPIO0ネットは入力として構成されます。次に、ユーザーは、SYSREFパルス、LEMC立ち上がりエッジ、またはLEMC立ち下がりエッジのいずれかでトリガーすることを選択できます。この記事に示されているデータでは、LEMC立ち上がりエッジがNCOマスター/スレーブ同期トリガーソースとして使用され、GPIOネットはサブアレイ上でローカルではなくBBPを介してルーティングされます。次に、DDC同期ビットがローに切り替えられてからハイに切り替えられ、ADC側のNCO同期アルゴリズムが準備されます。同様に、マイクロプロセッサのアライメントビットがローに切り替えられてからハイに切り替えられ、DAC側のNCO同期アルゴリズムが作動します。

このトリガーが要求されると、次のLEMC立ち上がりエッジで、マスターデジタイザーICがGPIO0ネットを介してマスター出力信号をハイにアサートします。この信号は、各スレーブデバイスのGPIO0入力に伝播します。次のLEMCエッジでは、すべてのデジタイザICでNCOリセットアルゴリズムが実行されます。この後、NCOマスター/スレーブ同期アルゴリズムに関して、LEMCパルスはすべて無視されます。ワンショット同期と同様に、これらのNCOマスター/スレーブ同期サブタスクは、ユーザーが使いやすいようにAPI関数に含まれています。

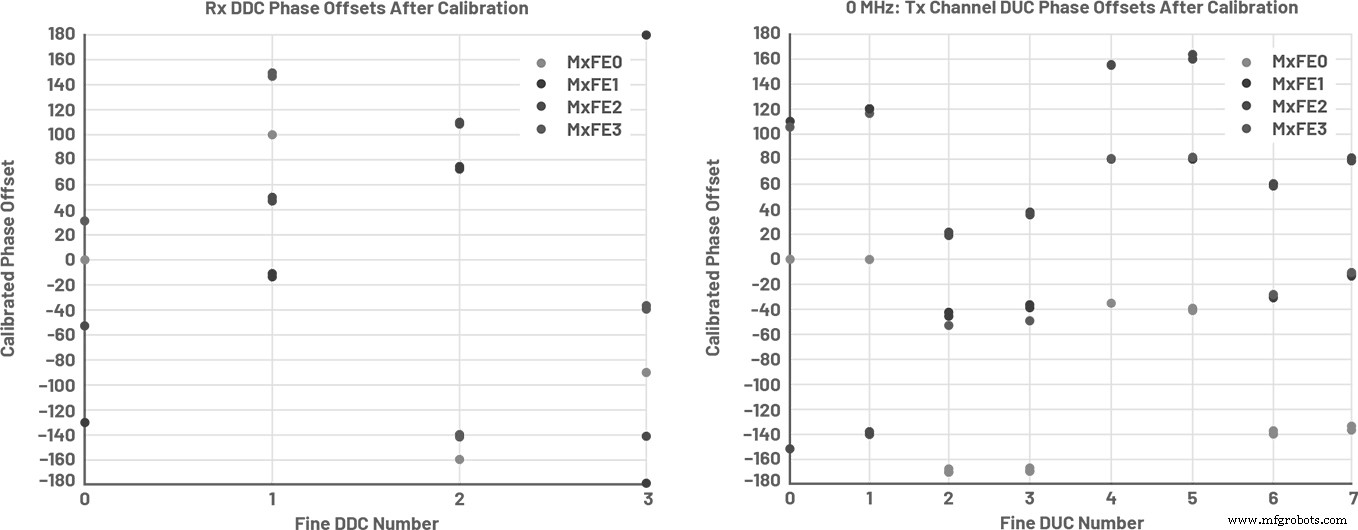

ワンショット同期とNCOマスタースレーブ同期機能の両方を使用すると、図4に示すように、各受信チャネルと送信チャネルの出力位相オフセットが複数の電源サイクル後に繰り返し可能になるように、両方の入力がすべてのDDC / DUCに調整されます。図4は、システムが各再起動中に静的な温度勾配の下で動作しているときの、各受信および送信チャネライザーの100パワーサイクル(複数の実線の点で示されている)にわたる校正済み位相オフセットを示しています。

クリックしてフルサイズの画像を表示

図4.MCSアルゴリズムを実行すると、受信ファインDDC(左)と送信ファインDUC(右)が適切に配置されます。 (出典:Analog Devices)

この図にある複数のドットからわかるように、特定のDDC / DUCの各色のドットは、電源を入れ直した後、すべて同じ位置に密集しており、特定のチャネルの決定論的フェーズを表しています。このテストのデータでは、送信側で8つのチャネライザーDUCがすべて使用されていますが、8つのチャネライザーDDCのうち4つだけが使用されています。ただし、実際には、8つのチャネライザーDDCはすべて、MCSアルゴリズムを使用しながら決定論的なフェーズを提供することが確認されています。

起動時にこのアルゴリズムを発行すると、PLLシンセサイザーのサンプルクロックとクロックIC SYSREFが起動時に同じ位相関係を維持する場合に、各チャネルの決定論的位相が確立されます。ただし、どのシステムでも温度勾配が発生するため、PLLクロックドリフトが発生する可能性があり、補償されないままにすると、異なるパワーアップフェーズが発生する可能性があります。システム内の温度勾配ドリフトを補正するために、このプラットフォームはPLLシンセサイザーの位相調整を利用しています。

このシリーズの次のパートでは、PLLシンセサイザーの位相調整、複数のサブアレイへのスケーラビリティ、およびシステムレベルのキャリブレーションアルゴリズムについて説明します。

参考資料

1デルジョーンズ。 「JESD204C入門書:新機能とその中身-パート1」 アナログダイアログ 、Vol。 53、No。2、2019年6月。

2デルジョーンズ。 「JESD204C入門書:新機能とその中身-パート2」 アナログダイアログ 、Vol。 53、No。3、2019年7月。

埋め込み