パワーアップ位相決定論:PLLシンセサイザーとシステムレベルのキャリブレーション

この記事シリーズの最初のパートでは、複数のデジタル信号処理(DSP)ブロック、広帯域デジタル-アナログコンバーター(DAC)、および広帯域アナログと統合されたチップ内のすべてのチャネルで既知の(決定論的)フェーズを実現する方法について説明しました。 -デジタルコンバーター(ADC)。サブアレイクロックツリー構造を採用した高レベルのシステムブロック図から始め、マルチチップ同期方法について説明しました。この第2部では、PLLシンセサイザーの位相調整、複数のサブアレイへのスケーラビリティ、およびシステムレベルのキャリブレーションアルゴリズムについて説明します。

PLLシンセサイザーの位相調整

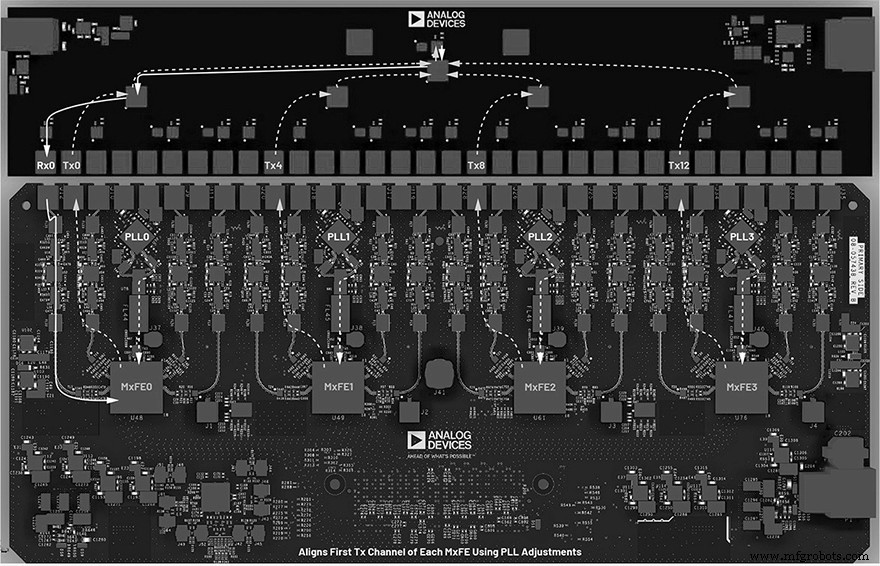

選択されたPLLシンセサイザーICは、各デジタイザーICに注入される相対的なサンプルクロック位相調整を可能にするように選択されています。熱ドリフト、およびサンプルクロックと各ICのSYSREF間の結果として生じるPLL位相ドリフトは、各デジタイザICの最初の送信チャネルが最初のデジタイザICの最初の送信チャネルに位相調整されることを保証するフィードバックメカニズムを作成することによって補償されます。このフィードバックループを実現するために、各ICの最初の送信チャネルは、図1に示すように、他の送信チャネルとは異なる信号を出力します。これらの4つの信号は結合され、このシステムではRx0とラベル付けされた共通の受信機に送信されます。 。

クリックしてフルサイズの画像を表示

図1.PLLシンセサイザーの位相調整機能により、各デジタイザーICの最初の送信チャネルをサブアレイ全体で整列させることができます。 (出典:Analog Devices)

すべての受信チャネルについて同時に受信データが取得されます。これにより、ユーザーは相互相関手法を適用し、これら4つの送信チャネル間の複素位相オフセットΦ TxOffset を決定できます。 。 PLLシンセサイザーICには、周波数ƒで動作する電圧制御発振器(VCO)が含まれています。 VCO_PLL 。

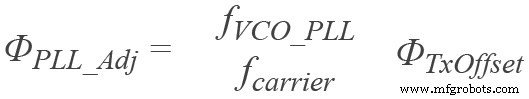

測定された位相オフセットΦ TxOffset 次に、必要なPLL位相調整Φ PLL_Adj に関連付けられます。 およびRF周波数ƒ キャリア そのような:

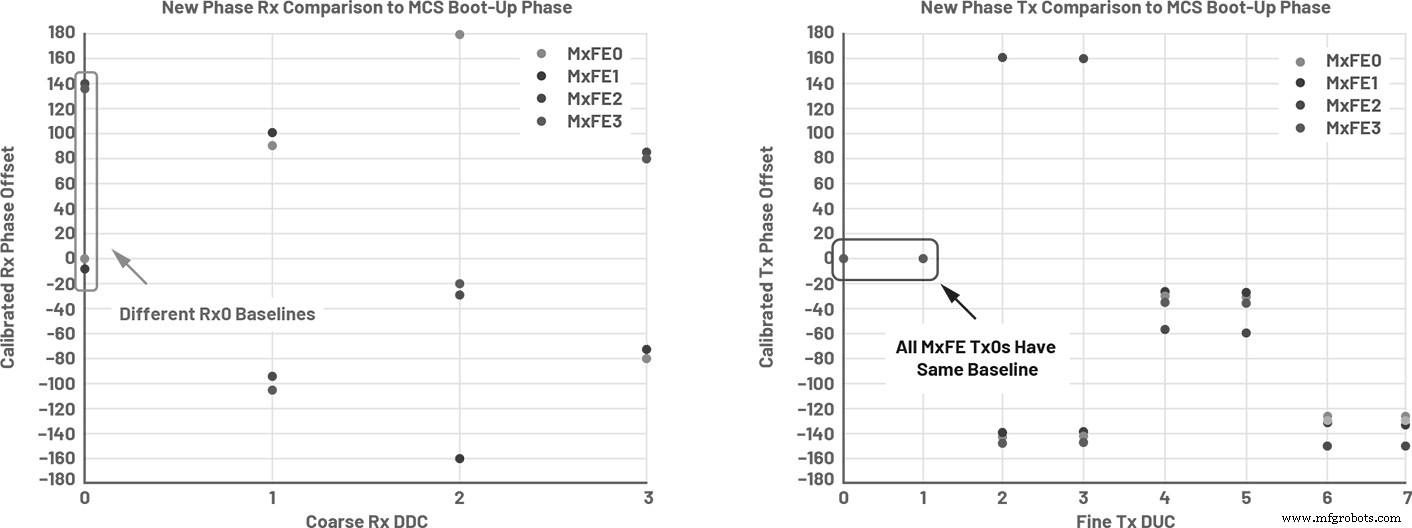

この式を使用すると、PLLシンセサイザーの位相を新しい既知の量で調整して、図2に示すように、すべてのパワーサイクルのすべてのデジタイザーIC間で共通の送信ベースラインを確立できます。図2に示す各チャネルの白丸は、最初の電源サイクル。他のすべての実線の点は、後続の電源サイクルに対応します。この図からわかるように、すべてのデジタイザICの1番目(および2番目)のチャネライザのキャリブレーションされた送信位相オフセットは、位相が調整されています。この場合も、システム内のDACごとに2つのチャネライザーが使用されるため、各デジタイザーICの2番目のチャネライザーが調整されます。

前のセクションで説明したMCSルーチンの前にこのPLLシンセサイザーの位相調整ステップを追加すると、システムを同じサンプルクロックとSYSREFの位相関係に強制することにより、システム内のすべての誘導温度勾配にわたって決定論的な位相が作成されます。すべてのデジタイザーICにわたるアライメントベースライン。

クリックしてフルサイズの画像を表示

図2.PLL位相を調整することにより、ユーザーはすべてのデジタイザーICの最初の送信チャネルを調整できます。 (出典:Analog Devices)

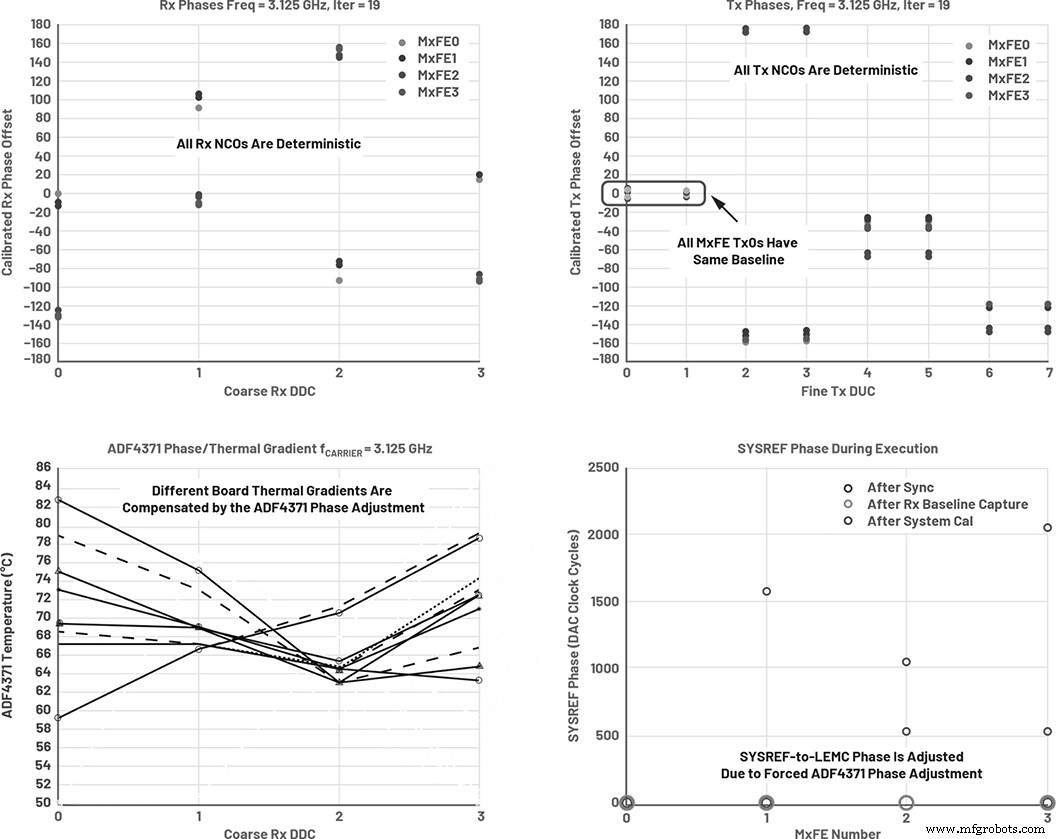

図3は、各PLLシンセサイザーチップの温度測定ユニット(TMU)を介して、誘導された温度勾配を検出できることを示しています。図3の左下にある青いトレースからわかるように、プラットフォーム全体で大きく変化する温度は、システムにさまざまなファンの気流を適用することによって意図的に誘発されています。ただし、各ICにPLL位相調整を使用すると、ボードに適用されるエアフローに関係なく、各デジタイザーICの最初の送信チャネライザーを他の。これは、さまざまな電源サイクル中にボードに適用されるさまざまな温度勾配にもかかわらず、図3の上の2つのプロットで同じ色のドットの密集したクラスターを観察することで明らかになります。

クリックしてフルサイズの画像を表示

図3.PLL位相調整機能と組み合わせて使用されるMCS機能は、プラットフォームに誘導される温度勾配に関係なく、すべての受信チャネルと送信チャネルのパワーアップ位相決定性を示しています。 (出典:Analog Devices)

図3の右下に示されているのは、ポーリングされたデジタイザーICレジスターです。これは、PLLシンセサイザーの位相オフセットを適用した後に測定されたSYSREF-LEMC位相関係を示しています。左下のプロットのオレンジ色のトレースから、PLLシンセサイザーの位相調整が、異なる誘導温度勾配に起因する測定された非ゼロのSYSREF位相を完全に補正していることに注意してください。

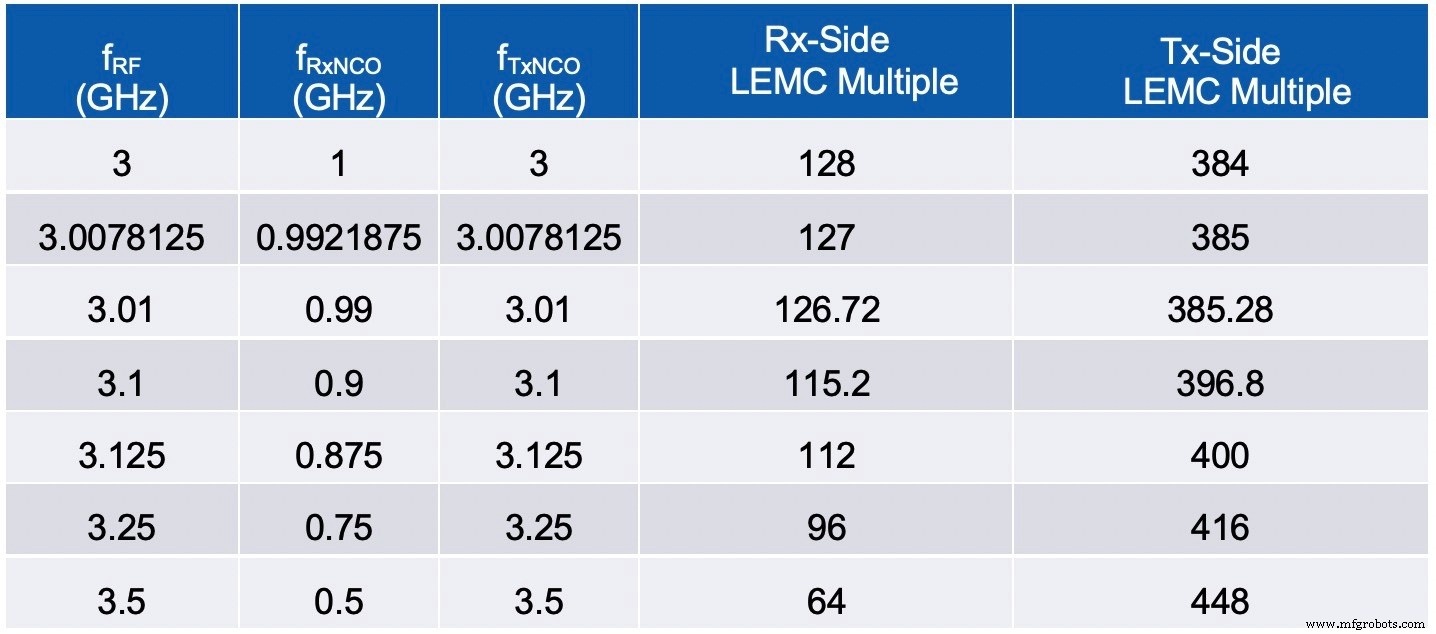

多くの周波数が測定されており、そのすべてが決定論的な受信および送信位相を示しています。この記事で選択した特定の周波数を図4に示します。これは、基準クロックまたはLEMCの非整数倍を使用した場合に、MCSが多くの誘導温度勾配で示されるように選択されています。

図4.この記事で使用されているRF周波数は、基準クロックとLEMCの非整数倍を含む幅広いクロックソースでMCS機能を実証するために選択されています。 (出典:Analog Devices)

複数のサブアレイへのスケーラビリティ

この記事に示されているデータは、主にサブアレイレベルでのMCSパフォーマンスに焦点を当てていますが、これらの同期機能がより大きなアレイレベルおよび複数のサブアレイで実現可能であることを確認する必要もあります。このより高いレベルの同期を実現するには、アレイレベルのクロックツリーが必要です。これにより、パート1の図1に示す各サブアレイへのSYSREF要求が、各サブアレイのクロックバッファICに同期的に到着します。次に、この基準が与えられると、各サブアレイは、前述のように必要なSYSREFとBBPクロックを発行して、これらの信号がより大きなアレイ全体で同じサンプルクロックサイクル内にサブアレイデジタイザICとBBPに到着するようにします。このアレイレベルのクロックツリーでは、各サブアレイへのクロック分配が、ダウンストリームサブアレイクロックチップICのそれぞれへの同期SYSREF要求分配を実現するために必要な遅延調整ブロックを備えている必要があります。このようにして、複数のサブアレイに接続された複数のBBPが最終的に同期されます。

システムレベルのキャリブレーションアルゴリズム

前のセクションで示したMCSアルゴリズムは、各受信チャネルと送信チャネルにパワーアップ決定論的フェーズを提供しますが、チャネル間のRFフロントエンドトレース長の違いにより、これらのフェーズは必ずしもRFドメイン内のすべてのチャネルで位相調整されているとは限りません。 。したがって、MCSアルゴリズムは実際にアレイのキャリブレーションプロセスを簡素化しますが、システム内の各RFチャネルの位相を調整するためにシステムレベルのキャリブレーションルーチンを実行する必要があります。

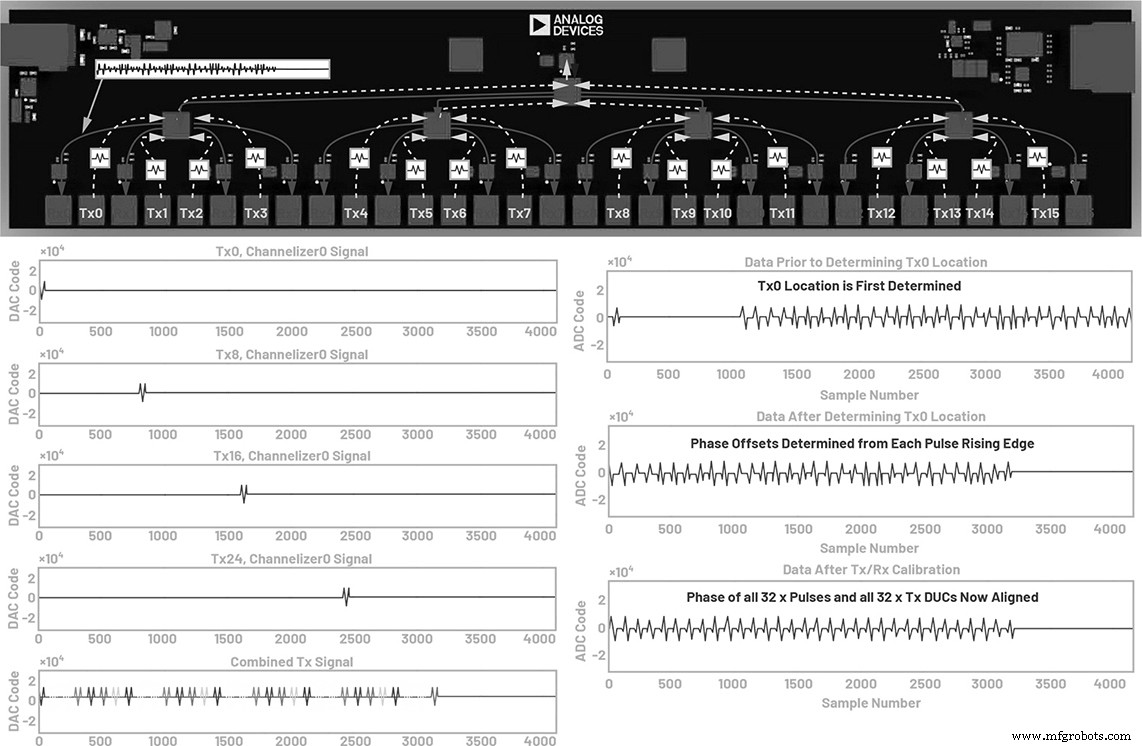

したがって、MCSアルゴリズムの実行に加えて、効率的なシステムレベルのキャリブレーションアルゴリズムを開発する必要があります。この記事のシステムレベルのキャリブレーション方法は、特定のベースバンド波形を利用し、外部機器を必要とせずに完全に自己完結型です。この記事で説明するシステムは、プラットフォーム上の各チャネライザーに個別のベースバンド波形を注入することができます。この機能を利用して、図5の左下に示すように、各送信チャネライザーの1周期パルスで構成されるベースバンド波形がサブアレイに注入されます。したがって、各送信チャネライザーは1つのパルスのみを出力します。ただし、波形はすべての送信チャネライザー間でずらされているため、システム全体で一度に1周期のパルスのみが出力されます。図5の上部に示すように、すべての送信チャネライザーの出力はRFドメイン内で結合され、分割されてすべての受信チャネルに送り返されます。最後に、すべての受信チャネルに対して同時受信データキャプチャが実行され、データが保存されます。 4096×16のマトリックスに変換されます。ここで、4096は16の受信チャネルすべてについて収集されたサンプルサイズです。

クリックしてフルサイズの画像を表示

図5.システムレベルのキャリブレーションアルゴリズムをMCSと組み合わせて使用して、システム内のすべての受信チャネルと送信チャネルの調整を迅速に実行します。 (出典:Analog Devices)

次に、このデータを最初の列(Rx0に対応)に沿って垂直に分析し、図5の右下の上部のサブプロットに示すように、Tx0チャネライザーパルスを特定します。Tx0パルスが識別されると、他のすべてのパルス位置がわかります。そして、各パルスの立ち上がりエッジの複素位相が計算され、システム全体のすべての送信チャネルに存在する測定された位相オフセットに対応する1×16ベクトルに保存されます。この知識を使用し、ベースライン基準としてTx0を使用すると、測定されたオフセットに基づいて、すべての送信チャネルの複雑な位相が変更されます。

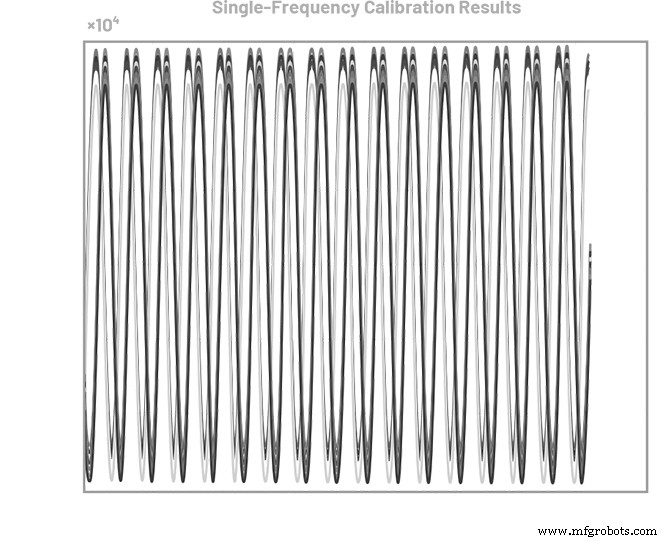

同様に、同じ結合信号がすべての受信チャネルに送信されているため、データはマトリックスに沿って水平方向に分析されます(すべての受信チャネルを調べます)。次に、すべての受信チャネルの複素位相がRx0に関して測定され、システムに存在する測定された受信位相オフセットに対応する1×16ベクトルに保存されます。次に、サブアレイ全体で受信NCO複合位相を調整して、すべてのチャネルをRx0に対して位相調整します。これは、図6の16個の受信チャネルすべての同相(I)および直交位相(Q)ADCコードで示されています。図6のプロットはすべてのチャネルを位相調整しますが、必ずしもすべてのチャネルを振幅調整するわけではないことに注意してください。ただし、これらのデジタイザICに現在搭載されているオンチップの有限インパルス応答(FIR)フィルタを使用すると、同じ結果を得るために電力を大量に消費するFPGAリソースを割り当てる必要なしに、チャネル間で振幅と位相の調整を行うことができます。

クリックしてフルサイズの画像を表示

図6.16チャネルの受信I&Q位相調整は、MCSと自己完結型のシステムレベルのキャリブレーションアルゴリズムを使用して実現されます。 (出典:Analog Devices)

このシステムレベルのキャリブレーションアルゴリズムは、現在、MATLAB ® で実現されています。 完了するまでに約3秒かかります。ただし、ハードウェア記述言語(HDL)で実装されている場合、完全に自己完結型のアルゴリズムを維持しながら、このキャリブレーション時間をさらに短縮できます。さらに、MCSアルゴリズムに依存することにより、起動時にシステムの周波数と振幅がわかっている場合、ユーザーは、このシステムレベルのキャリブレーション方法で説明されている測定を行う代わりに、ルックアップテーブルから位相オフセット値をロードできます。この場合、システムレベルのキャリブレーション方法を使用して、工場でのキャリブレーション中にルックアップテーブルに保存された位相オフセットを設定できます。

結論

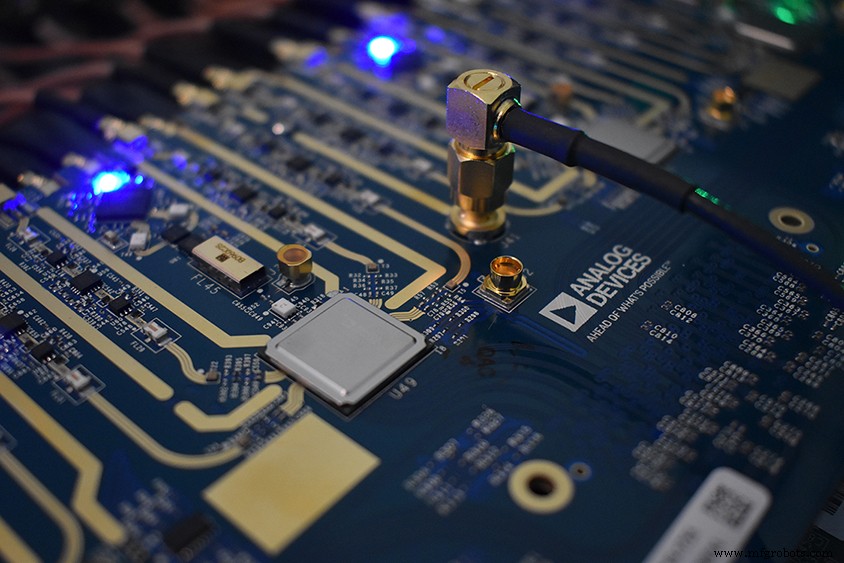

成功したMCSプロセスは、サブアレイのバックボーンとして4つのアナログデバイセズのAD9081 MxFETMICを使用して実証されています。プラットフォーム全体の温度勾配は、4つのADF4371PLLシンセサイザー内の位相調整ブロックを使用して補正されます。 HMC7043クロックICは、JESD204Cインターフェイスに必要なSYSREFおよびBBPクロックを分配するために使用されます。 AD9081内のMCSアルゴリズムにより、システムレベルのキャリブレーションが簡素化され、システムに存在する複数の周波数と温度勾配に対してパワーアップの決定論的位相が提供されます。工場でのキャリブレーション中にLUTを設定するために使用される、効率的なシステムレベルのキャリブレーションアルゴリズムも提示されているため、システムの起動時間が大幅に短縮されます。このプラットフォームを図7に示し、Quad-MxFEと呼びます。このシステムは、アナログ・デバイセズから購入できます。この作業は、フェーズドアレイレーダー、電子戦、計装、または5Gプラットフォームに存在するマルチチャネルシステムに関連しています。

図7.Quad-MxFEプラットフォームは、アナログ・デバイセズから購入できます。 (出典:Analog Devices)

参考資料

1デルジョーンズ。 「JESD204C入門書:新機能とその中身-パート1」 アナログダイアログ 、Vol。 53、No。2、2019年6月。

2デルジョーンズ。 「JESD204C入門書:新機能とその中身-パート2」 アナログダイアログ 、Vol。 53、No。3、2019年7月。

埋め込み