FINDRRAMアレイの応力と温度に関連するRTNとアニーリング

要約

この作業では、FinFET誘電体RRAM(FIND RRAM)デバイスの読み取り電流におけるランダムテレグラフノイズ(RTN)信号の観察結果を示します。 FIND RRAMセルのRTN信号は、デバイスがサイクリングストレスにさらされた後に変化することがわかります。サイクリングストレスを受けた後、RRAMセルはより頻繁で強いRTN信号を示す傾向が強くなります。 FIND RRAMセルのノイズレベルの増加は、一般に高温アニーリングによって軽減できます。このコンセプトにより、オンチップアニーリングスキームが提案され、実証されています。

はじめに

CMOSテクノロジの継続的なスケーリングにより、過去10年間で集積回路の特性とパフォーマンスが大幅に向上しました。ただし、テクノロジーノードが20 nm未満に縮小されると、デバイス特性の単一原子/電子による変動、たとえばランダムドーパント変動(RDF)が増加し、監視できない根本的な問題が発生します[1]。たとえば、キャリアの数や構造上の欠陥の変動は、スケーリングされたデバイスの出力とパフォーマンスにはるかに大きな影響を及ぼします。また、RDFとゲートラインエッジラフネス(LER)による変動に対するデバイスのスケーリングの影響もあります。報告されています[2、3、4]。ランダム電信ノイズ(RTN)は、NANDフラッシュやRRAMなどの小さな面積のデバイスにとってもう1つの大きな課題であると考えられています[5、6、7、8、9、10、11]。この作業では、nチャネルFinFETベースのFIND RRAMセルのRTNノイズを調査します。これは、1kビットアレイの標準ロジックプロセスですでに正常に実装されています[12]。サイクル応力と高温ベークに応じたRTNの変化が観察されます。この作業では、FIND RRAMセルのRTNノイズに対する応力と温度の影響を調査し、サイクリング後の時変読み取り電流ノイズを軽減するためのオンチップアニーリングスキームを提案します。

背景とメソッド

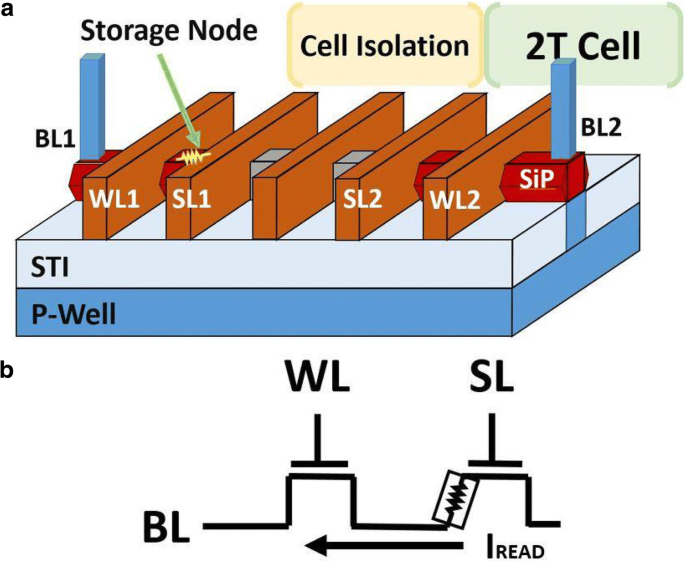

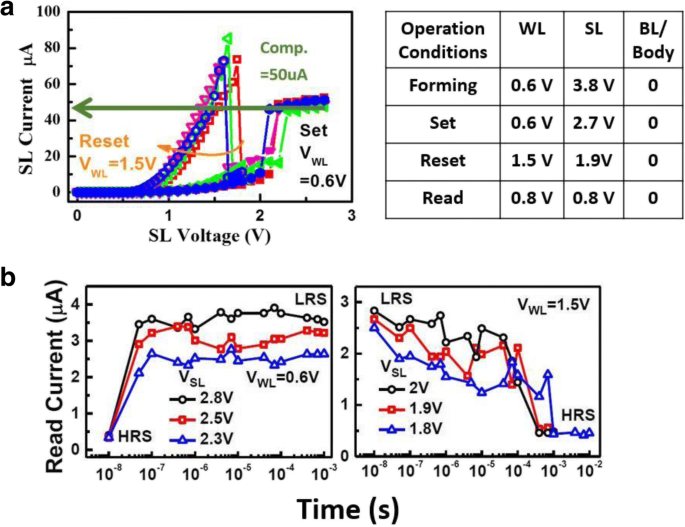

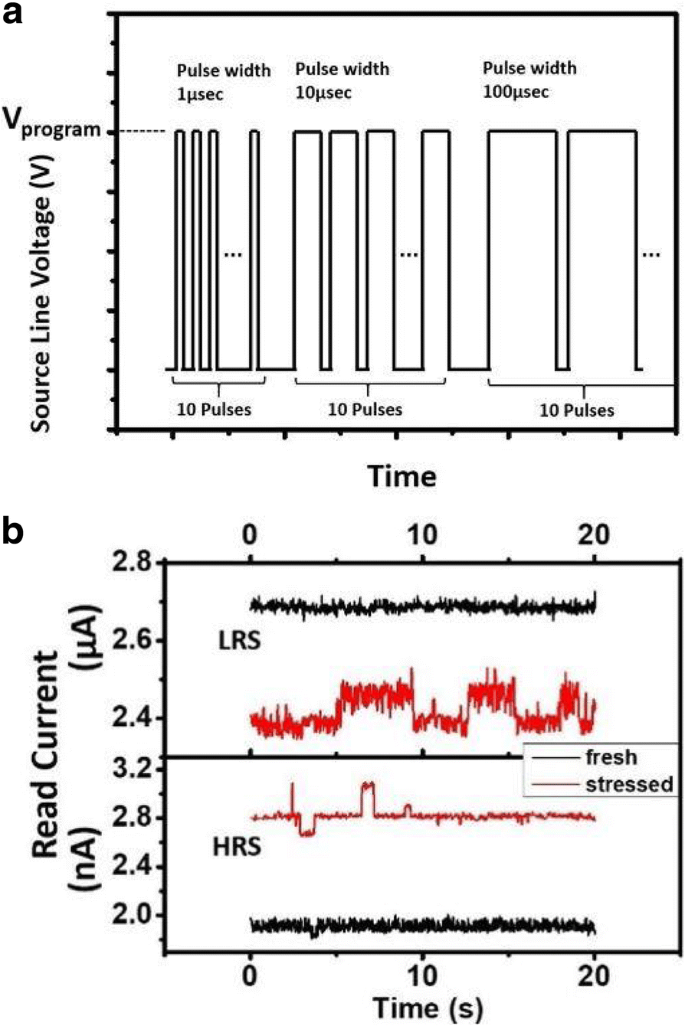

FIND RRAMは、2つのFinFETトランジスタで構成されています。 1つはRRAMノードの直列のWL選択トランジスタとして機能します。図1aに示すように、他のトランジスタのSiPとSLの間のhigh-kゲート誘電体は、ストレージノードとして機能します。 FINDデバイスは、標準のFinFETのゲート誘電体膜で構成されています。ゲート電極は上部電極がW、下部電極がTaNです。ゲートスタック酸化物はHfO 2 で構成されています / SiO 2 / TiNスタックレイヤー[12]。 FIND RRAMセルの読み取り条件を図1bに示します。ここでは、WLに0.8 Vを与えて選択トランジスタをオンにし、0.8VをSLに追加してデータを読み取るのに十分な読み取り電流を駆動します。高抵抗状態(HRS)と低抵抗状態(LRS)の状態間の抵抗スイッチングは、FINDRRAMセルでセット/リセットを実行することによって実現されます[13]。 FIND RRAMは、DCスイープ下でかなり安定した抵抗スイッチング機能を示します。図2aを参照してください。また、セットまでの時間とリセットまでの時間の特性を図2bにまとめています。図2aに示す動作条件は、低電圧動作が可能であることを示しています。セルは、目標の読み取り電流レベルに到達するために、セットとリセットの両方で複数のパルスサイクルを受けます。図3aに示すように、複数のパルスが印加された後にデバイスがセットまたはリセットに失敗すると、パルス幅が増加します。図3bに示すように、特徴的なRTN信号はLRSセルとHRS FINDRRAMセルの両方に見られます。電流伝導経路での電荷トラップとデトラップによって引き起こされるRTN信号は、大きな電流変動を引き起こす可能性があります[14、15、16、17]。

a CMOSFinFETテクノロジーと b によって実装された2T FINDRRAMセルの3Dイラスト 読み取り状態でのFINDRRAMのユニットセルの回路図を示します。ここで、VSL =VWL =0.8 Vで、BLはゼロにバイアスされています

。

FIND RRAMのDC抵抗変化型機能とその動作条件を( a )に示します。 )。その設定時間とリセット時間の特性は、( b )にまとめられています。 )

a セット/リセット操作を実行するために使用される増加するパルス幅の図。 1μsの最初のパルスの後、読み取り操作が実行され、読み取り電流がLRSの場合は3μA、HRSの場合は1μA未満の目標レベルに到達するかどうかが評価されます。必要な状態が達成されない場合、次のパルスが与えられます。パルス幅は10パルスごとに1桁拡張されます。 b VSL =VWL =0.8VおよびVBL =0でサンプリングされた室温での読み取り電流の比較(サンプリングレート500 Hz、100回のサイクル前後)

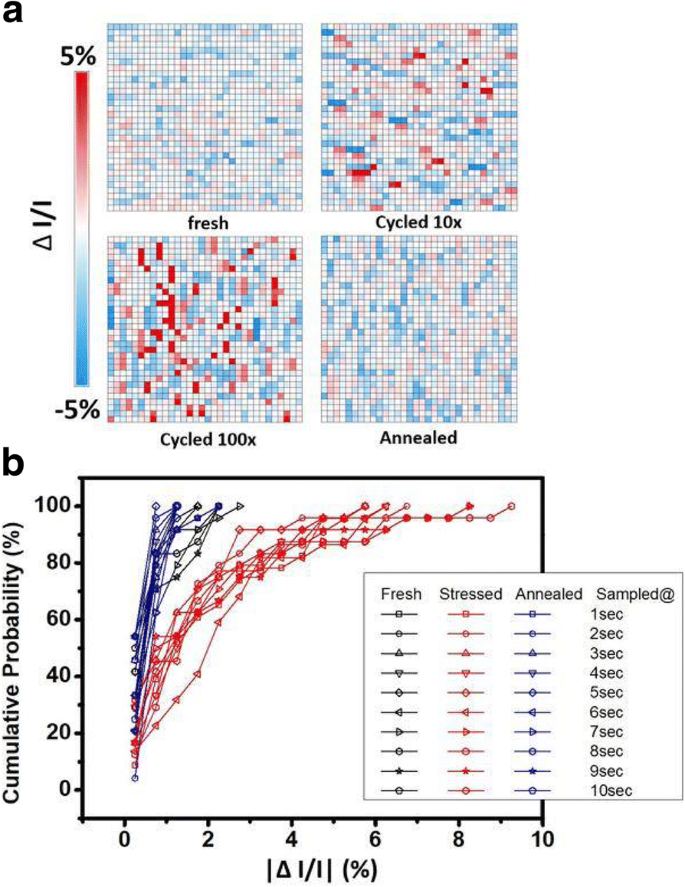

繰り返し循環する、つまり2つの状態を切り替えると、ゲート誘電体層のFinFETに応力が発生する可能性があることは十分に確立されています[18]。 FIND RRAMセルの応力がかかった遷移金属酸化物(TMO)層は、RTNノイズを示す傾向が強く、データの読み取り中に読み取りエラーと安定性の問題を引き起こす可能性のある時変読み取り電流につながります。この実験では、FIND RRAMのRTNに対するストレスの影響を観察するために、アレイの読み取り電流を新鮮な状態、10倍サイクル後、および100倍サイクル後にサンプリングしました。

ストレスを受けたFINDRRAMセルに対する温度の影響を調査するために、LRSで明確なRTN信号を持つサンプルは、最初に0°Cまで冷却され、次に徐々に50°Cまで加熱されます。このプロセス中、これらの温度での読み取り電流は、500Hzのレートで20秒間継続的にサンプリングされます。これにより、RTNが温度変化下でどのように動作するかについての手がかりが得られます。

結果と考察

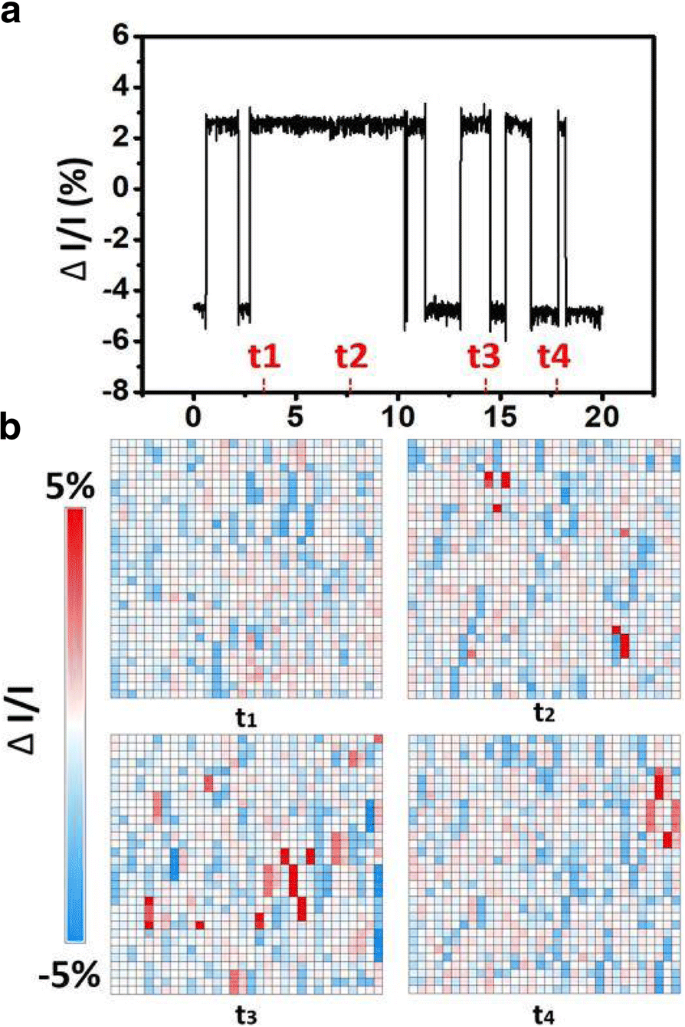

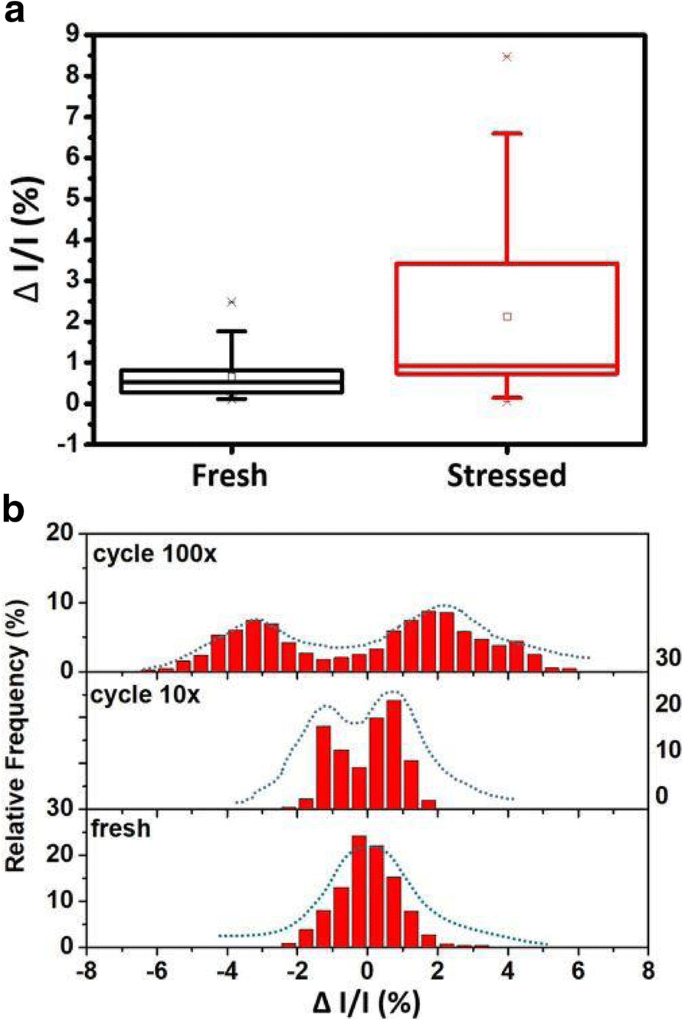

広範囲にわたる測定を通じて、RTNはより安定しており、LRSのFINDRRAMセルで簡単に観察できることがわかります。したがって、FIND RRAMセルのRTNに対するサイクリングとアニーリングの影響の研究では、次のセクションではLRSでのセルの調査に焦点を当てます。図4aに示すように、RTNノイズは時変の読み取り電流を引き起こし、読み取りエラーを引き起こします。この効果は、1kビットのセルアレイで観察できます。 10サイクルを経たアレイでは、20秒間隔で読み取り電流をサンプリングすると、読み取り電流に大きな変動が見られます。アレイ内の正規化されたビット電流マップを図4bに示します。ここで、LRSの電流変動は+ 5%に達する可能性があり、これはストレス後のゲートリーク電流で観察されるRTNに匹敵します[19]。ストレスの影響を調査するために、サイクリングストレスの前後の50セルの電流変動レベルを追跡しました。図5aのデータは、90%を超えるセルがサイクリング後にΔI/ Iの増加を示すことを示しています。つまり、FIND RRAMの時変ノイズは、セルがより多くのサイクリングストレスを経験するにつれて徐々に悪化することが示されています。新鮮な細胞と循環細胞の正規化された読み取り電流分布を比較すると、より多くの周期を経た細胞はより重要なRTN信号を示し、特定の状態で2つ以上のピーク電流分布を示すことがわかります。一方、新鮮な細胞は標準分布の電流分布を持っており、図5b [20、21]に示すように、変動に関係するRTNノイズがないことを示唆しています。これは、FIND RRAMが長いサイクリングストレスを受けると、RTNの追加により、そのビットセル電流がより急激に変動する可能性があることを示唆しています。

a 10サイクルを経たRRAMセルで500Hzのレートでサンプリングされた25°Cでの正規化された読み取り電流。これは、RTNが時変読み取り電流を引き起こすことを示しています。 b 10サイクルを経て、t1 =3、t2 =7.5、t3 =14、t4 =17.5sで同時にサンプリングされた1kbitアレイの正規化電流のプロットを示します。異なる時間のスナップショットを比較することにより、同じ読み取り条件で読み取り電流が変動します

a |ΔI/ I |の分布を比較するストレスの前後の50サンプルの。ストレス後、細胞は全体的に大きなΔI/ Iを示すことがわかります。下から上への箱ひげ図のパーセンタイル値は、それぞれ25、50、および75パーセンタイルポイントを表し、ひげは最大値と最小値を示します。 b 新鮮な状態と10および100サイクル後に測定されたセルの正規化された読み取り電流分布のヒストグラム。これは、FIND RRAMが長いサイクルストレスを受けると、RTNの追加により、そのビットセル電流がより急激に変動する可能性があることを示しています。

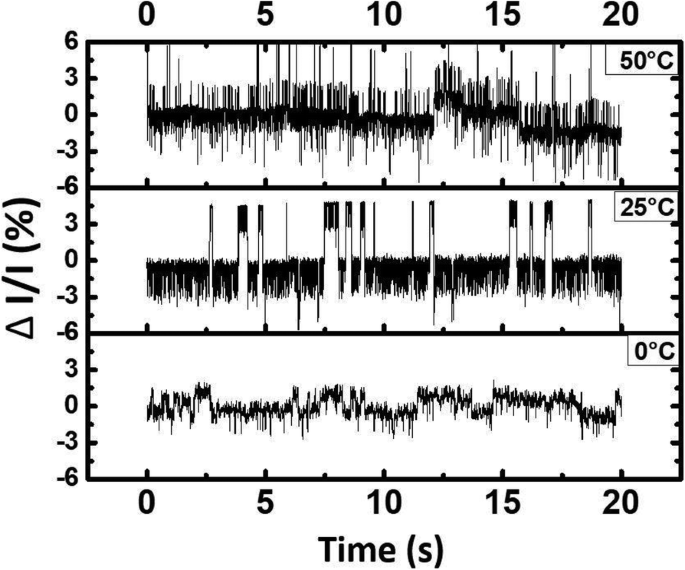

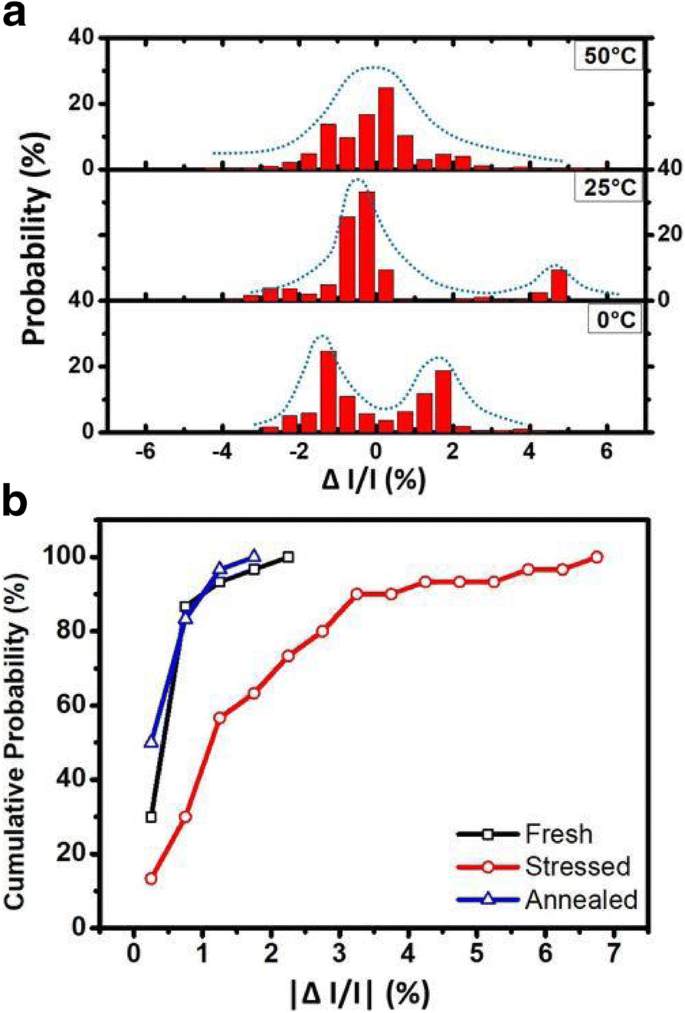

さまざまな温度段階での読み取り電流サンプルの正規化された結果を図6で比較します。RTNトラップのキャプチャ時間と放出時間は研究されており、温度とともに変化することが知られており、どちらも温度が上昇すると減少します[22、23 ]。予想どおり、RTNノイズの周波数は、温度が上昇するにつれて上昇します。つまり、0°Cでの読み取り電流の変動は、25°Cでの変動よりも発生頻度が低くなります。ただし、50°Cで測定すると、2つの状態間の電流変動は目立たなくなります。これは、0°C、50°C、および室温で測定された正規化された読み取り電流のヒストグラムをプロットした図7aでさらに明らかになります。 0°Cと25°Cの電流分布には2つの分布ピークがあり、導電経路を支配する単一のトラップ状態RTN [19]を示唆していますが、50°Cでのサンプリング電流の離散状態は目立たなくなります。これは、高温では、RTN信号を引き起こすトラップがアニーリング効果や欠陥再結合などの不安定性にさらされ、その結果、電子トラップ確率に影響を与え、RTN効果を緩和する可能性があることを示唆しています[27]。

500 Hzのサンプルレートで0、25、および50°Cで測定されたRTNノイズを使用して100サイクルを通過したRRAMセル(LRS状態)の正規化された読み取り電流の比較

a 0、25、および50°Cで測定されたLRS状態のセルの正規化された読み取り電流分布のヒストグラムの比較。 b |ΔI/ I |の累積確率の比較ストレス前、ストレス後、アニーリング後の30サンプルのそれぞれ。セルの大部分は、アニーリングプロセス後に元のΔI/ Iに戻ることがわかります

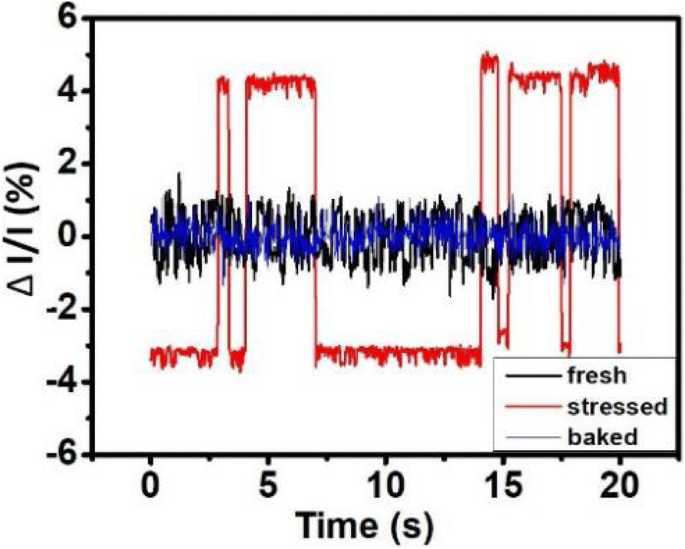

さらなる研究では、サンプルは75°Cまで加熱されます。これらのセルは30分後に室温まで冷却され、サンプルが採取されます。 30個のセルを選択し、フレッシュ、ストレス、およびアニーリング後の累積電流変動レベルを図7bで比較します。これは、ほとんどのセルがアニーリングプロセス後に元のΔI/ Iに戻ることを示しています。フレッシュ状態、ストレス状態、およびベイク後のセルからの正規化された読み取り電流を図8で比較します。ベイク後の電流はフレッシュの電流に似ており、高温ベイクがRTN信号を引き起こすトラップをアニールすることを示唆しています。図9aは、それぞれ、新鮮なセル、わずかにストレスがかかったセル、非常にストレスがかかったセル、およびベイク後の1kbitアレイの正規化された読み取り電流のプロットです。プロットから、RRAMに大きなストレスがかかると電流変動がより激しくなり、高温ベーク後に大幅に減少することが示されています。この効果はアレイ全体で観察でき、高温ベークが実際にRTNノイズを誘発するトラップにアニーリング効果を提供することを確認しています[24、25、26、27、28、29]。図9bは、10回の異なるサンプリングによって連続して得られたセルアレイのΔI/ I分布をさらに比較しています。同じアレイが、そのフレッシュ、ストレス、およびアニーリング後の状態で異なるΔI/ I分布を示すことがわかります。データは、アニーリングが、新しい状態のアレイのレベルと同様に、セルアレイが減少した電流変動を示すのに役立つことを示唆しました。この結果は、サイクリングストレス後にRTN信号を示したFINDRRAMセルの寿命を修正および延長するために使用できます。

25°C、500 Hzでサンプリングされた新鮮な細胞とストレスを受けた細胞の電流を、高温で焼き、室温まで30分冷却した後の細胞の電流と比較して読み取ります。これは、ベイク後、ストレスが軽減され、セルが新しいセルと同じように動作することを示しています

a 特定の時間に取得された1kbitアレイの正規化された読み取り電流は、新鮮な、軽いストレス、高いストレス、およびアニーリング後にプロットされます。アレイがより多くの応力を受けると、アレイ全体で変動の強いセルの数が大幅に増加し、アニーリング後に消滅することがわかりました。 b |ΔI/ I |の累積確率の比較1秒間隔の異なる時間インスタンスでの、フレッシュ、ストレス、およびアニーリング後の状態での同じアレイからの50サンプルの分布。応力後のサンプルの全体的なΔI/ Iは高くなり、アニーリング後に通常に戻ります

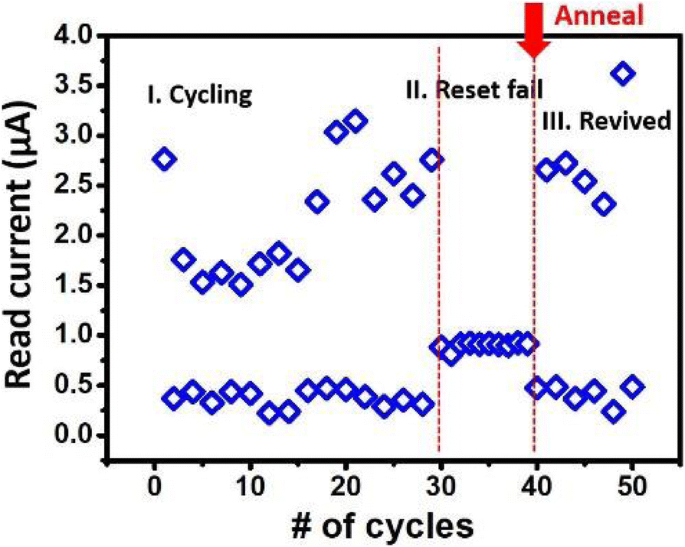

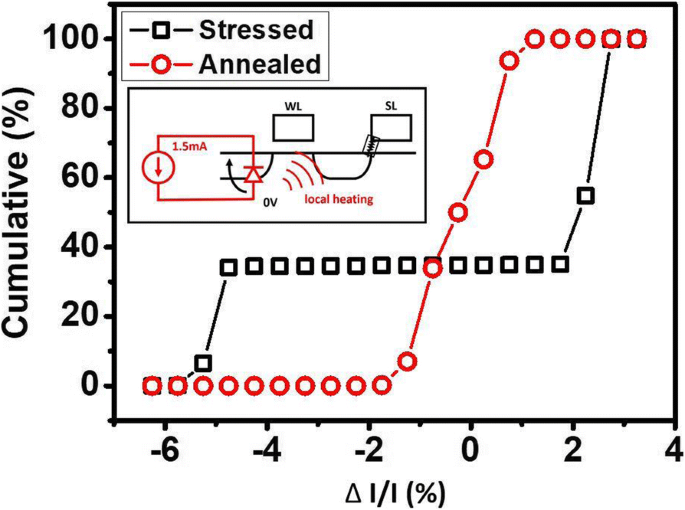

サイクリング中に中間状態でスタックしたいくつかの細胞は、高温処理後に復活することは言及する価値があります。 FinFET RRAMセルがLRSとHRSを循環するとき、一部のセルの導電性フィラメントは、簡単にリセットできないチャネルを形成する場合があります。ベークプロセスは、それらのセルにその酸素空孔を再分配するためのパスを提供し、その結果、HRSへの効果的なリセットを可能にします[30]。図10は、125°C、15分のベイク後に復活したHRSに切り替えることができなかったセルを示しています。これを念頭に置いて、FINDRRAMセルを局所的に加熱することを含むオンチップアニーリングメカニズムを提案します。図11aに示すように、選択したFinFETのドレイン接合部で順方向バイアスを介して、10秒周期で1.5mAの定電流がセルに印加されます。この大電流は、RRAM TMOの近くの閉じ込められた領域を加熱し、同様のアニーリング効果を提供します。図11bで、被試験デバイス(DUT)のアニーリング前後の読み取り電流を測定および分析します。連続的にサンプリングされた読み取り電流の累積分布は、オンチップアニーリングステップ後のセル上のRTNの除去を示しています。ここで、FIND RRAMのオンチップアニーリングは、ストレス後の典型的なRRAMセルへの公称応答を理解するために、連続したステップで単一セルに対して実行されました。アレイレベルの実験には、新しいオンチップアニーリング手順を開発する必要があります。

中間状態でスタックしているセルに125°Cのベイクを適用し、アニーリングプロセスを提供することで、これらのセルを機能状態に戻し、セルの寿命を延ばします

私たちが提案したオンチップアニーリングスキームでは、BLに-1 Vを印加すると、順方向バイアスと1.5 mAの測定電流が発生し、ストレスを受けたセルが加熱されてアニーリングされます。プロットでは、プロセスの前後のセルの正規化された電流の累積パーセンテージを比較することにより、RTNによって引き起こされる電流変動が大幅に減少していることがわかります

結論

この論文では、FINDRRAMセルアレイのRTNに対するストレスと温度の影響について説明します。サイクリングストレスによるRTNの増加が観察されます。 FINDRRAMでRTNの低減とTMOのストレス緩和に及ぼす高温処理の影響が観察されます。最後に、オンチップアニーリングスキームが提案され、実証されています。

略語

- FIND RRAM:

-

Fin電界効果トランジスタ誘電抵抗変化型メモリ

- HRS:

-

高抵抗状態

- LER:

-

ラインエッジの粗さ

- LRS:

-

低抵抗状態

- RTN:

-

ランダムな電信ノイズ

- TMO:

-

遷移金属酸化物

ナノマテリアル