Verilog の紹介

Verilog はハードウェア記述言語 (HDL) の一種です。 Verilog は、FPGA と ASIC を設計するために教育とビジネスで使用される 2 つの言語のうちの 1 つです。 FPGA と ASIC の仕組みに慣れていない場合は、FPGA と ASIC の概要についてこのページをお読みください。 Verilog と VHDL は、使用される最も一般的な 2 つの HDL です。 Java や C などの従来のソフトウェア言語と比較すると、Verilog の動作は大きく異なります。簡単な例を見てみましょう。

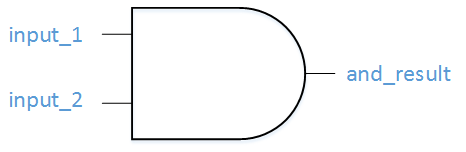

まず、記述する Verilog ファイルを作成します。 アンドゲート。復習として、単純な And ゲートには 2 つの入力と 1 つの出力があります。出力は、両方の入力が 1 に等しい場合にのみ 1 に等しくなります。以下は、Verilog で説明する And ゲートの図です。

アン アンド ゲート

アン アンド ゲート 始めましょう! Verilog の 1 つの基本単位はワイヤと呼ばれます。ここでは、ワイヤは 0 または 1 のみであると仮定しましょう。基本的なワイヤ ロジックは次のとおりです。

wire and_temp; assign and_temp = input_1 & input_2;

コードの最初の行で and_temp というワイヤを作成しています。コードの 2 行目では、作成したワイヤーを取得し、代入 しています。 ワイヤー。それを割り当てるために、Verilog ではアンパサンド (&) であるブール AND 関数を使用しています。上記のコードを説明するとしたら、次のように言うかもしれません。 input_1 と input_2 の AND 演算。"

Input_1 と Input_2 は、この Verilog コードへの入力です。入力と出力の完全なリストを表示しましょう。これは モジュール で行われます 意味。 Module は Verilog の予約済みキーワードで、入力と出力が定義されたコード ブロックの作成を示します。

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

これが基本モジュールです。これは、example_and_gate と呼ばれるモジュールと 3 つの信号、2 つの入力と 1 つの出力を定義します。すべてをまとめてファイルを完成させましょう。欠けているのは、出力 and_result の割り当てだけです . Verilog では、 // はコメントに使用されます。

///////////////////////////////////////////////////////////////////////////////

// File Downloaded from http://www.nandland.com

///////////////////////////////////////////////////////////////////////////////

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

wire and_temp;

assign and_temp = input_1 & input_2;

assign and_result = and_temp;

endmodule // example_and_gate

おめでとう!これで、最初の Verilog ファイルが作成されました。

愚かなゲートを作成するためだけに多くのコードを書かなければならなかったように見えますか?まず第一に、ゲートは愚かではありません。次に、HDL は比較的単純なタスクを実行するために多くのコードを必要とします。 Verilog は少なくとも VHDL よりも冗長ではないという事実に、ある程度の安心感を覚えることができます。ソフトウェアでは非常に簡単だったことが、Verilog や VHDL などの HDL では非常に長くかかるという事実に慣れてください。しかし、ソフトウェア担当者に、Conway のライフ ゲームを表示する VGA モニターに画像を生成するように依頼してください。ちなみにあの動画はFPGAで作っています。すぐにできるようになります!

Verilog