適切なRISC-Vカスタム命令を使用してアプリケーションを高速化するためのガイド

RISC-Vのオープン命令セットアーキテクチャ(ISA)は、実装の幅広い柔軟性を可能にし、ハードウェアとソフトウェアの設計のトレードオフを解決するための新しいアプローチを可能にするオプション機能を提供します。モジュール構造に基づいて、いくつかの標準的な拡張機能とオプションを使用して、ベースプロセッサを開始点として構成できます。しかし、真の価値は、実際には、RISC-Vが開発者に、革新的なアプリケーションのアイデアのニーズを独自に満たす新しい拡張機能、命令、および構成を作成する機会を提供することにあります。

固定ISAのソフトウェアチャレンジ

従来、ISAは、マイクロプロセッサまたはマイクロコントローラを販売したい、または他の人が使用できるように設計のライセンスを取得したい商業組織の知的財産(IP)でした。組み込み開発者は、ベンチマークソフトウェアを実行して、アプリケーションのニーズに最適なソリューションを決定する必要があります。必要なすべてのエコシステムを備えた独立したISAを開発するコストのため、半導体ベンダーは、主流のIPプロバイダーが提供する標準の固定ISAにますます依存し、ムーアの法則と統合された周辺機器に依存して、超低電力などの差別化を実現していました。 、顧客へ。

ここでの課題は、コードの実行に使用される命令を変更できないことです。したがって、たとえば暗号化アルゴリズムの最適化された命令によって得られる可能性のある効率は実現できません。これは、開発者のアプリケーションが遅すぎるか、消費電力が多すぎる可能性があるか、制御ループのハードリアルタイムの期限を定期的に逃していることを意味している可能性があります。世界で最高の意志を持っていても、これらは、半導体製造の改善やプロセスの縮小だけで解決するのが難しい要因です。

RISC-V ISAは、カリフォルニア大学バークレー校でプロジェクトとして開始され、現在は300人を超えるメンバーを擁する非営利団体であるRISC-V InternationalAssociationによって管理されています。これらは、ISA仕様、シミュレーターやコンパイラーなどのソフトウェアツール、およびそのような事業をサポートするために必要なエコシステムの残りの部分に貢献します。使用するのが理にかなっているかどうかは、ライセンスに関して無料であるか、それとも自由であるかという2つの要素のいずれかを活用できるかどうかによって異なります。

オープンで自由に利用できるため、教育と研究、および商用アプリケーションの両方で学界が簡単に使用できる基本的な処理プラットフォームを提供します。オープンISAは、商用IPプロバイダーからオープンソースプロジェクトやクリーンシートの自作設計に至るまで、半導体IPの調達を検討している開発者向けの多数のビジネスモデルもサポートしています。商業組織もこれを魅力的であり、FPGA、SoC、さらにはマイクロコントローラーや標準製品のコアに利用しています。

学界は自由を提供するため、コンピューティングの課題に対処するための新しいアプローチを調査し、新しい命令やその他のアクセラレータ、マルチコアおよびメニーコアの異種設計に加えて、さまざまなマイクロアーキテクチャオプションから何でも実装できます。これらのオプションの多くは、エンドアプリケーションの要件に合わせて調整されたカスタム命令を追加することで、エッジで動作する低電力の人工知能(AI)チップセットなど、複雑な課題に取り組みたいスタートアップや企業にとっても魅力的です。

エコシステムはRISC-Vの柔軟性が組み込まれた状態で確立されているため、標準の構成またはカスタム拡張機能は、ISA準拠のフレームワーク内のツールとソフトウェアを活用できるはずです。

オープンRISC-VISAの柔軟性を理解する

RISC-V ISAと関連ツールのアクセシビリティのおかげで、特定のアプリケーションでの使用への適合性を評価するための調査プロジェクトを簡単に開始できます。シミュレーションツールを使用すると、標準のベースISAを試して、すぐに使用できるパフォーマンスを判断できます。たとえば、適切な開始点は、整数「I」と乗算「M」拡張(RV32IMとして参照可能)を備えた32ビットRISC-V構成で、基本32ビット整数命令セットのサポートを提供します。より多くのオプションが利用可能ですが、この例ではこれで十分です。次に、これは、アクセス遅延や待機状態などのシミュレートされたメモリとともにインスタンス化されます。

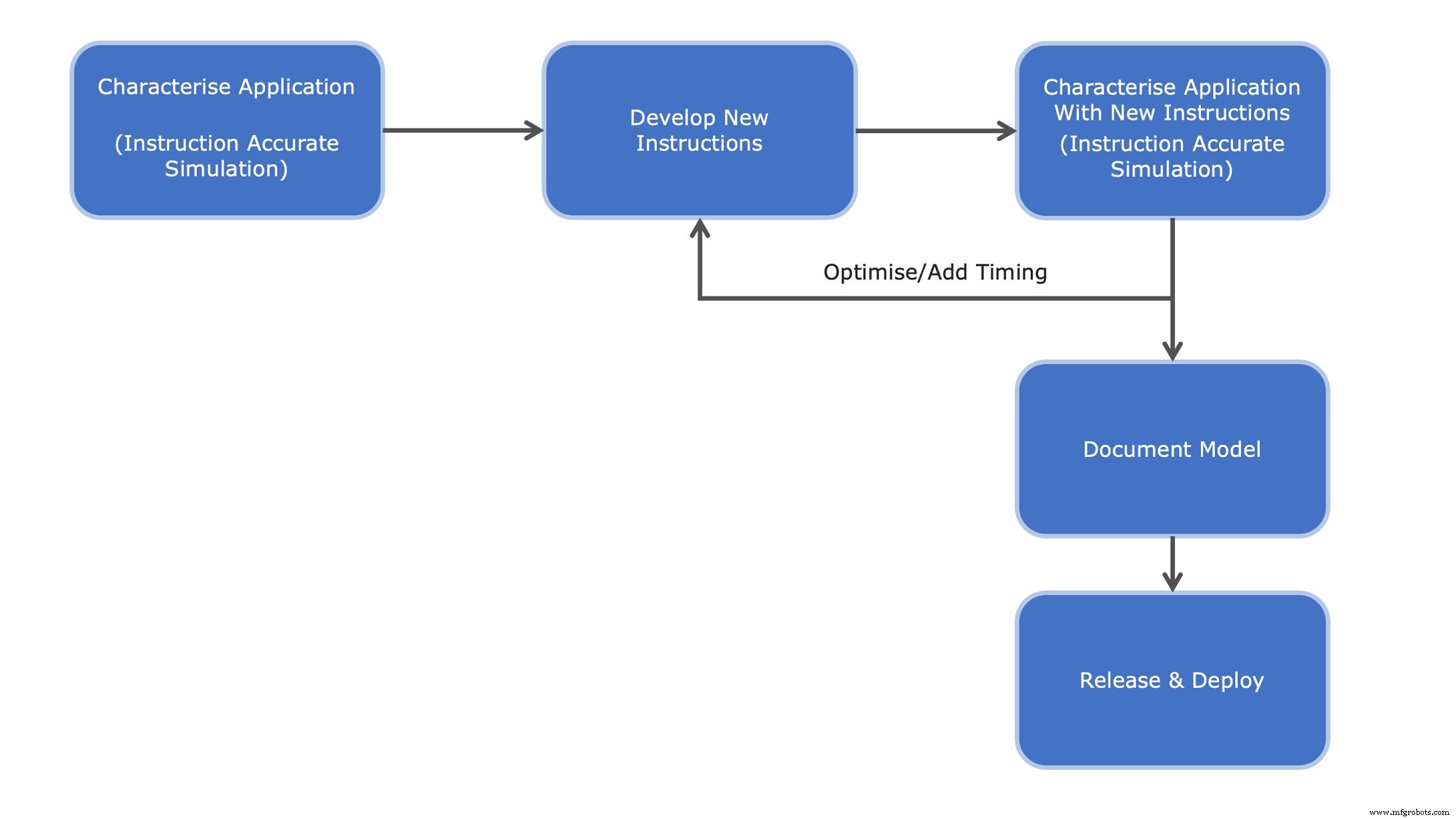

C / C ++で記述されたアプリケーションは、標準のツールチェーンを使用してクロスコンパイルできます。これは、ベアメタル上で実行されている場合もあれば、(リアルタイム)オペレーティングシステム(RTOS / OS)の一部として実行されている場合もあります。結果として得られるバイナリコードは、選択したベースプロセッサモデルを統合してシミュレーションできる命令セットシミュレータ(ISS)などのツールを使用して実行されます(図1)。この環境は、標準の入出力機能とホストファイルシステムへのアクセスも提供します。次に、Eclipseなどの標準の統合開発環境(IDE)ツールを使用して、GNUデバッガーGDBを介してインターフェイスし、コードの実行を制御できます。

ここから、プロファイリングと分析のプロセスを通じて、指導候補が特定され、設計され、モデル化されます。元のアプリケーションコードを基本的な機能モデルとして使用することにより、結果として得られる改善を迅速にテスト、検証し、パフォーマンスを比較することができます。このプロファイリングと分析の迅速な反復により、実装する価値のある命令の迅速な選択と最適化が可能になります。ドキュメントはモデルから生成でき、レジスタ転送ロジック(RTL)設計および最適化されたモデルの機能仕様の基礎を形成します。

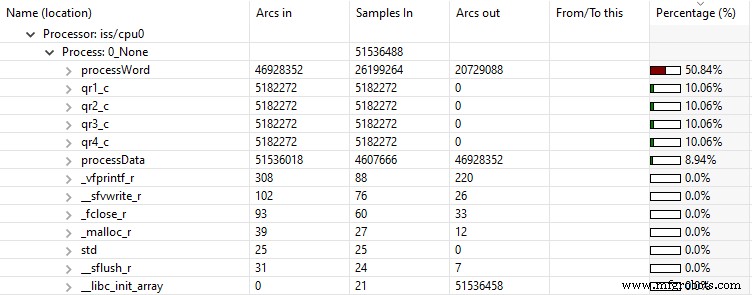

例として、ChaCha20などの暗号化アルゴリズムは特定のアプリケーションにとって重要な場合があります。利用可能なソースコードは、「バニラ」RV32IMベース用にコンパイルして実行し、基本ブロックプロファイリングを使用して推定命令サイクルタイミングで分析して、コードのどのセクションで費やされたかを判断できます。 ChaCha20アルゴリズムのコアは、クォーターラウンドと呼ばれるXORおよびローテーション命令を多用します(図2)。ブロックプロファイリングの結果は、実行時間の大部分がこれらの機能に費やされていることをすぐに明らかにします。

これらのホットスポットのグラフィカルな視覚化は、検証、分析、およびプロファイリング(VAP)ツールを使用して生成することもできます。テキスト出力を提供するのではなく、実行時間は折りたたみ可能な統計のツリーとして提供され、実行された命令の割合が高いホットスポットをより適切に視覚化するのに役立ちます。これは、関数 processWord()が表示されている図3で確認できます。 ChaCha20アルゴリズムを実装し、4つの qrx_c を順番に呼び出します。 必要な1/4ラウンド関数を実装するための関数。

コンパイラによって生成されたアセンブラコードを確認したり、基本ブロックプロファイリングを実行したりすることで、アルゴリズムの実装に使用された命令と命令の組み合わせを判別できます。ここから次のステップは、ISAの仕様の範囲内で、実行速度を向上させる可能性のあるカスタム命令を決定することです。

RISC-Vがもたらす可能性のある改善の決定

ChaCha20アルゴリズムは、7、8、12、および16ビットの左回転と組み合わせたXORを多用します。 RV32IM基本仕様の使用可能な命令を使用すると、これにはXOR命令とそれに続く左シフト命令が必要であることがわかります。これは、これらの2つのステップを、7、8、12、または16ビットの左回転とともにXORを実装する4つの専用命令に最適化する可能性があることを意味します。

ロードストアアーキテクチャであるため、カスタム命令では、操作するデータがこのRISC-Vの32ビットレジスタの1つにすでに存在していることを前提としている必要があります。これにより、 custom-1 に配置できるRタイプ(レジスタ)命令が必要であることがすぐに判断されます。 スペースをデコードします(図4)。

ISA定義では、結果の2つのソースレジスタとデスティネーションレジスタを規定するために、3つの事前定義されたビットブロックが予約されています。これにより、 funct3 と呼ばれるビットのブロックが残ります。 。これらの3ビットは、8つの可能な命令をエンコードする余地を提供し、そのうちの4つがこの例で使用されます。

これらの命令にRTLの詳細なハードウェア実装を必要とせずに、ISS環境でそれらをシミュレートして、直面している課題にまったくメリットがあるかどうかを確認することができます。 4つの新しい命令は、オープン仮想プラットフォーム(OVP)VMIアプリケーションプログラミングインターフェイス(API)を使用してモデル化されています。これにより、開発者は、ターゲットアプリケーションの新しい命令に基づいて、最適な望ましい結果を提供する命令の設計を迅速に繰り返すことができます。これが達成されて初めて、RTL実装にリソースをコミットする必要があります。

命令の初期機能評価の目的で、2つの可能なアプローチがあります。 1つ目は、アルゴリズムの元のC / C ++バージョンを呼び出して、新しい命令をこの関数にバインドすることです(図5a)。 2つ目は、同じ動作を作成するVMIモーフ命令としてそれらを実装することです(図5b)。これには、より効率的であるという利点があり、推奨されるアプローチです。

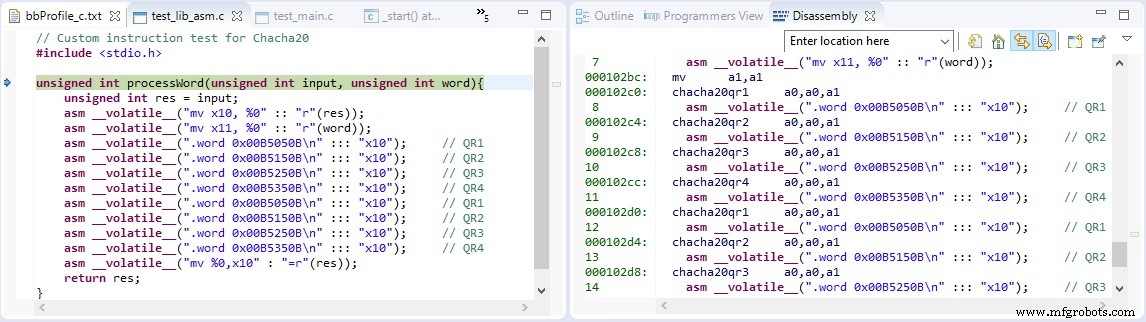

もちろん、新しい命令が存在するだけでは、コンパイラがすぐにそれらを利用できるわけではありません。したがって、元のC / C ++アプリケーションは、インラインアセンブラを使用して書き直し、新しい命令を使用するためにクロスコンパイルする必要があります。候補命令のプロファイリングと分析は反復的なタスクになる可能性があるため、組み込みベースのアプローチは、元のCアプリケーションを新しいカスタム命令を使用するように適応させる最も効率的な方法を提供します。

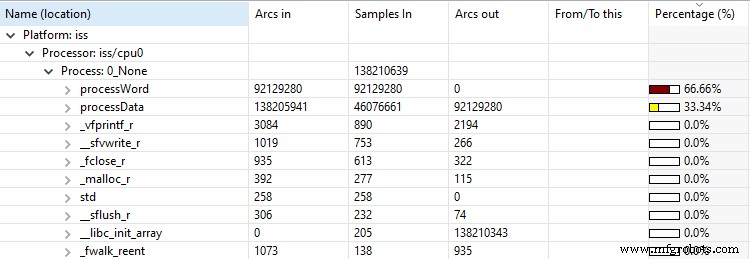

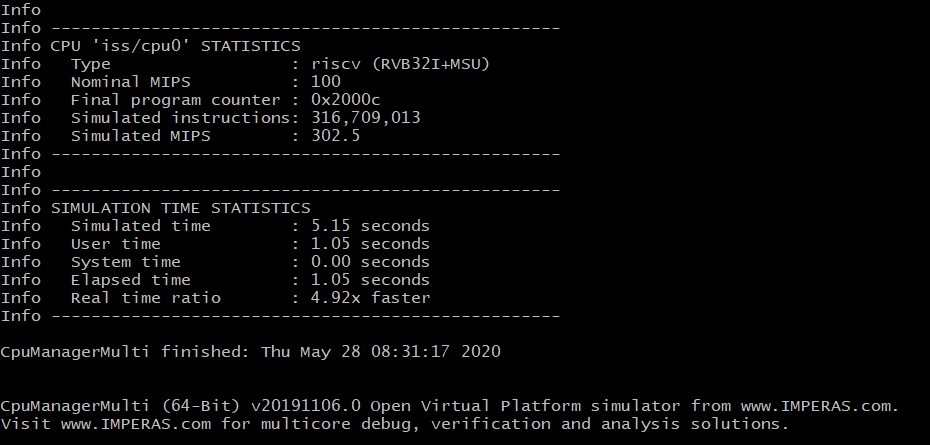

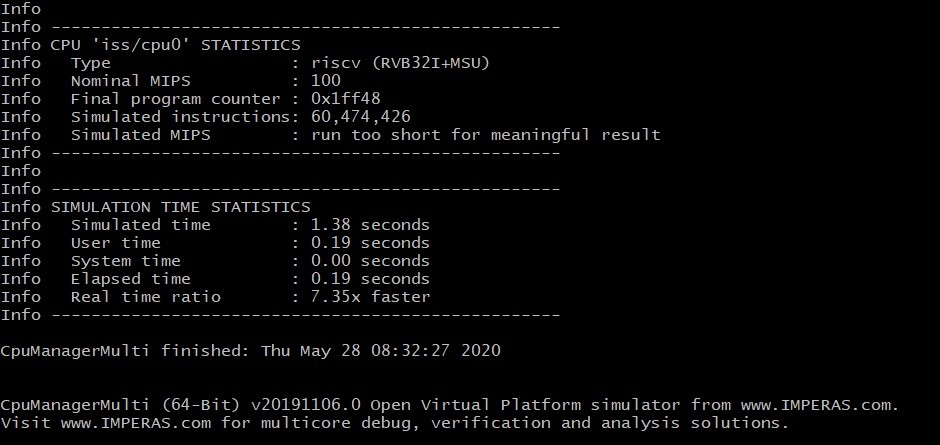

シミュレータにロードされたRISC-Vベースの実装も、新しい命令を利用するために、それらを認識する必要があります。これは、シミュレーションを再実行する前にモデルにそれらを含めることによって実現されます。この特定の例では、プロファイリングを繰り返すと、アルゴリズムの実行に費やされる全体的な時間が少なくなります(図6)。 Imperas VAPプロファイリングツールは、 processWord() 専用のインライン命令を使用する関数は、アルゴリズム実行全体の66%を占めるようになりましたが、アルゴリズムの全体的な実行時間は大幅に短縮されました(図6b)。

元のC実装の結果

情報シミュレートされた手順:316,709,013

情報シミュレートされた時間:5.15秒

カスタム手順による結果

情報シミュレートされた手順:60,474,426

情報シミュレートされた時間:1.38秒

正しい機能が決定されると、プロセッササイクルで各命令の実行時間を宣言することにより、モデルがさらに洗練されます。その後、シミュレーションのさらなるラウンドを使用して、最終的なハードウェア実装で発生する可能性のあるメモリアクセスに関連する待機状態を考慮に入れても、パフォーマンスの向上を判断できます。

一般的なオープンソースIDEおよびGDBツールとの緊密な統合のおかげで、ソリューションの完全なデバッグは、設計をハードウェア実装にコミットする前に、最適化されたRISC-V設計と組み合わせて行うことができます(図7)。

シミュレーションから実装への移行

潜在的なパフォーマンスの向上が決定されたら、次のステップでは、RTLに4つの新しい命令を実装する必要があります。実施された予備作業のおかげで、これは要件を定義する機能仕様になり、ゴールデンリファレンスモデルとしてRTL検証テスト計画の一部として使用することもできます。 Cアプリケーションでの組み込み関数の使用は、カスタム命令のプロファイリングと分析に役立ちましたが、このアプローチは、将来の本番コード開発にも利用できます。また、コンパイラツールチェーンの拡張機能として検討することもできます。

他の残りの重要なタスクであるドキュメントも、単純なプロセスです。すべてのオープン仮想プラットフォーム(OVP)高速プロセッサモデルには、変更および修正の機能をカバーするように拡張できるドキュメントが含まれています。与えられたテンプレートに従って、新しい命令を宣言および記述できるため、開発者コミュニティはそれらの機能を発見して利用することができます。次に、ドキュメントは、PDFを生成できるTeXファイルに変換されます(図8)。

概要

RISC-VのオープンISAの自由により、仕様で定義されている標準オプションと機能に加えて、ユーザーはさらにカスタム拡張機能と命令を開発できます。最も単純な方法では、商用およびオープンソースの実装を含む新しい創造的なビジネスモデルが可能になり、さらに、主流の従来のアプローチを超えた付加価値機能をより自由に探索できるようになります。

ただし、真の価値は、本格的で文書化され、サポートされているベースコアを採用し、特定のアプリケーションのニーズに合わせて変更することから得られます。注意深いアプリケーション分析、コードのプロファイリング、およびシミュレーションを通じて、固定ISAでは実現できなかった大幅なパフォーマンスの向上を実現できます。詳細なハードウェア実装を開始する前に、これらすべてを実際のアプリケーションワークロードで開発およびプロファイリングできます。

埋め込み

- Perfを使用した分散アプリケーションのプロファイリング

- バインダー噴射による3D印刷のショートガイド

- チタンを使用した3Dプリントのガイド

- マイクロチップ:COTSから耐放射線性のコアMCUを使用したスケールスペースアプリケーション

- ルネサス:産業用アプリケーション向けのEtherCATをサポートするRX72M MCU

- Axiomtek:統合されたレイヤー2マネージドPoEスイッチを備えた組み込みシステム

- 既存のサプライヤーとのコストの再交渉:ガイド

- CNCウッドルーター-見事なアプリケーション

- 保険におけるAI入門:入門ガイド

- 医学におけるAIの5つの実際のアプリケーション(例を含む)

- 高速鉄道用途向けのカスタムブレーキシューとパッドのガイド