スパイキングニューラルネットワーク用のニューロモルフィックAIチップがデビュー

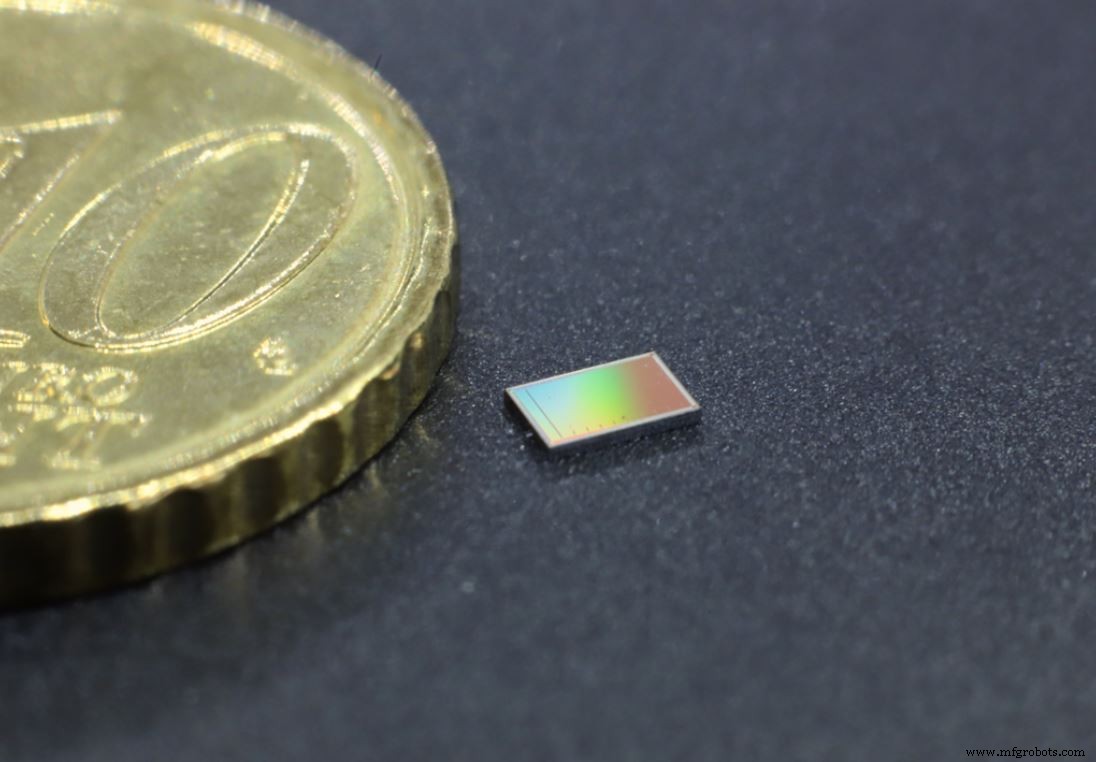

スパイキングニューラルネットワーク用のニューロモルフィックAIアクセラレータを製造しているオランダの新興企業、Innateraは、最初のチップを製造し、そのパフォーマンスを測定し、アーキテクチャの詳細を明らかにしました。

スパイキングニューラルネットワーク用のニューロモルフィックAIアクセラレータを製造しているオランダの新興企業、Innateraは、最初のチップを製造し、そのパフォーマンスを測定し、アーキテクチャの詳細を明らかにしました。

同社はまた、ケイデンスとシノプシスの共同創設者であるアルベルト・サンジョヴァンニ・ヴィンセンテッリが取締役会会長として同社に加わったことを発表しました。業界のベテランは現在、カリフォルニア大学バークレー校の教授です。

Innateraのチップは、オーディオ、ヘルス、レーダーアプリケーション向けのさまざまなSNNを高速化するように設計されています(画像:Innatera)

Innateraチップは、電気信号のスパイクのタイミングを使用してパターン認識タスクを実行する、脳生物学に基づくニューロモルフィックAIアルゴリズムの一種であるスパイキングニューラルネットワーク(SNN)を加速するように設計されています。 SNNは、主流のAIアルゴリズムとは構造が完全に異なるため、高速化のために専用のハードウェアが必要ですが、通常、センサーエッジアプリケーションに大幅な電力消費と遅延の利点を提供します。

スパイキングニューラルネットワークアルゴリズムとハードウェアに取り組んでいる他のほとんどの企業(たとえば、Prophesee)は、画像とビデオストリームをターゲットにしています。 Innateraは、音声(音声と音声の認識)、健康(バイタルサインの監視)、レーダー(プライバシーを維持する高齢者の転倒センサーなどの消費者/ IoTのユースケース向け)に重点を置くことを決定しました。

Marco Jacobs(画像:Innatera)

「これらのセンサーには、非常に平行な画像ではなく、時系列データが含まれています」と、Innateraのマーケティングおよび事業開発担当副社長であるMarco Jacobsは、 EE Times とのインタビューで述べています。 。 「私たちのアレイは時系列データの処理に特に優れています…それはテクノロジーにぴったりです。また、市場の観点からは、この分野で多くの興味深いアプリケーションが見られますが、それに対処するソリューションはそれほど多くありません。」

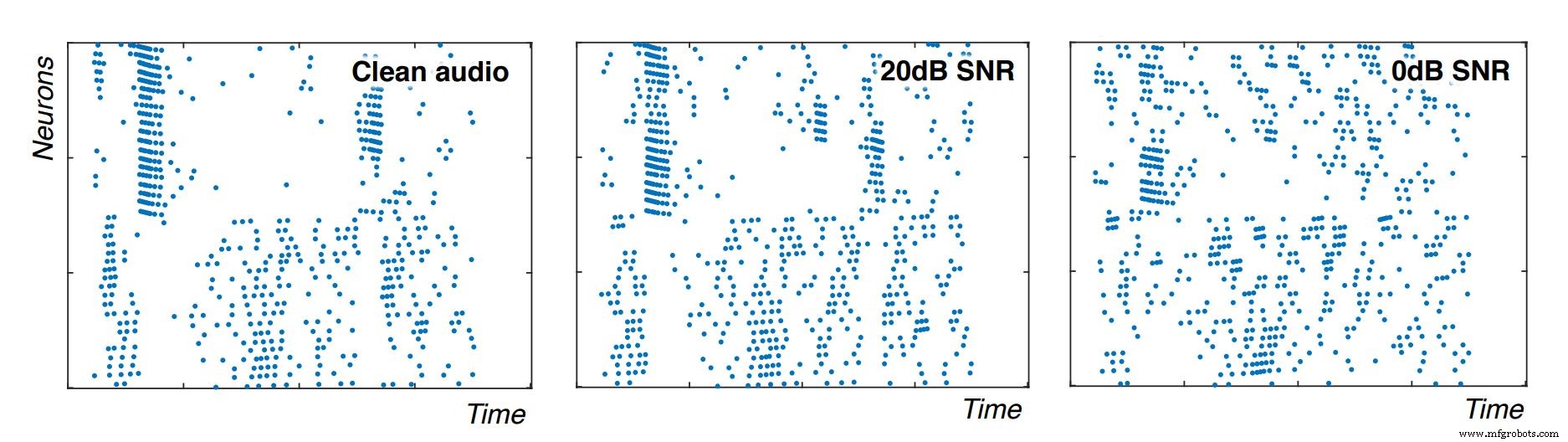

これら3つのアプリケーションに共通するもう1つの点は、センサーノードで処理が必要なため、電力エンベロープが非常にタイトであることです。 Innateraのテストでは、各スパイクイベント(入力データに応答して発火する各ニューロン)に必要なエネルギーはピコジュール未満でした。実際、TSMC28nmでは200フェムトジュール未満であることがInnateraによって確認されました。これは、生物学的ニューロンとシナプスによって使用されるエネルギーの量に近づいています。 InnateraのCEOであるSumeetKumarによると、典型的なオーディオキーワードスポッティングアプリケーションでは、推論ごとに500未満のスパイクイベントが必要であり、その結果、「サブミリワットの電力損失が深くなります」とのことです。この場合、一緒に発火するニューロンのクラスターは、音声の異なる音素を表します。

発火するニューロンのクラスター(ここではドットのグループ)は、音声の音素の検出を表します。入力データにはより多くのノイズが組み込まれているため、同じクラスターがほとんど存在しますが、見つけるのは困難です(画像:Innatera)

処理アーキテクチャ

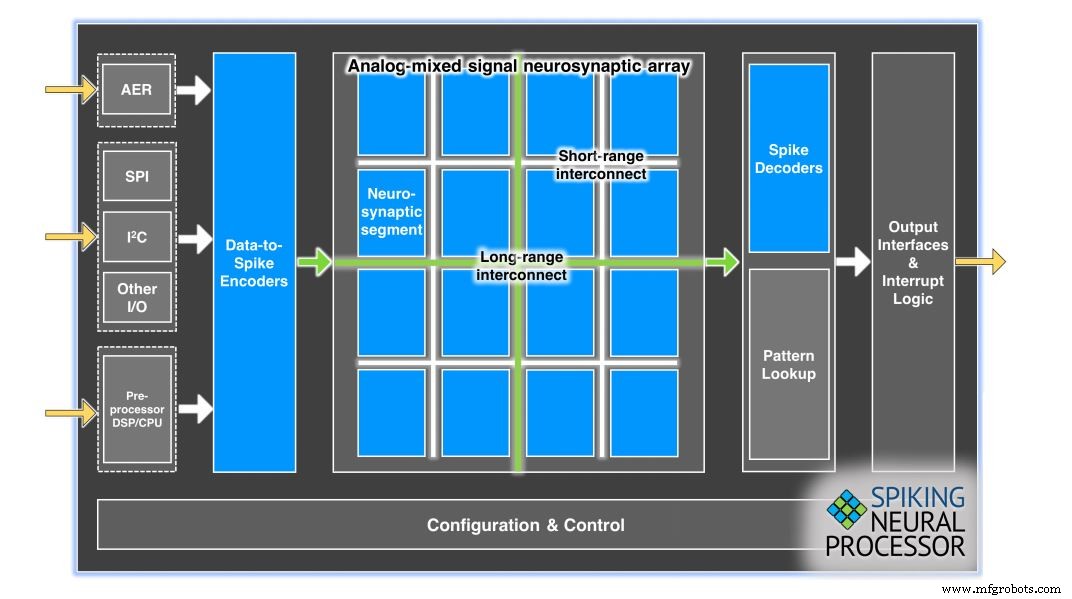

Innateraのスパイキングニューラルプロセッサは、スパイキングニューロンとシナプスの並列配列を使用して、きめ細かい時間的ダイナミクスで連続時間SNNを加速します。このデバイスは、データの処理方法に時間の概念を組み込むSNNの機能を活用するように設計されたアナログ/ミックスドシグナルアクセラレータです。

Innateraのスパイキングニューラルプロセッサには、超並列神経シナプスアレイとスパイクエンコーダおよびデコーダが含まれています(画像:Innatera)

Innateraのコンピューティングファブリックの重要な側面の1つは、そのプログラム可能性です。これは、2つの理由で重要です。

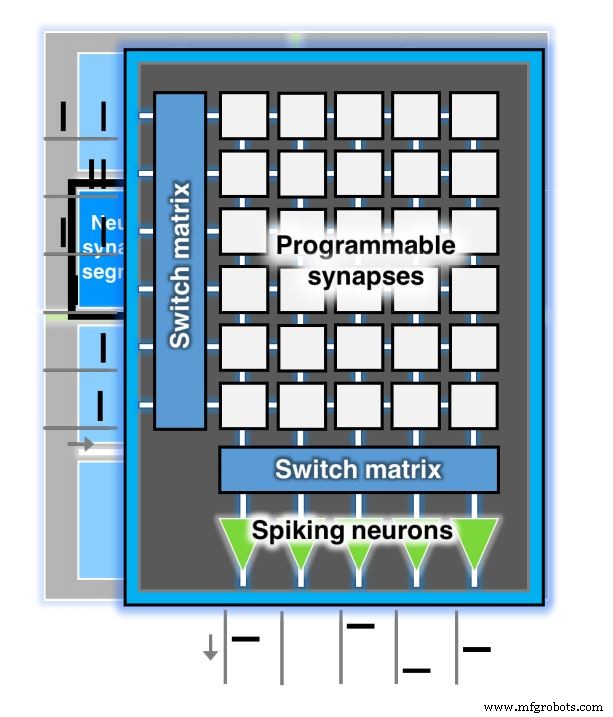

まず、さまざまなSNNをチップにプログラミングします。ニューロンは柔軟な方法で接続する必要があります。脳は非常に複雑なニューラルネットワークトポロジを使用して効率的に処理を行うため、ニューロン間の複雑な接続が必要であり、シリコンで再作成する必要があります。

Sumeet Kumar(画像:Innatera)

第二に、パフォーマンスを最適化するため。 SNNでは、情報を単語のビットとして表すのではなく、正確なタイミングのスパイクとして表します。スパイクのタイミングは、データに関する洞察を抽出するために、非常にきめ細かいレベルで操作する必要があります。したがって、ニューロンとそれらの間の接続(シナプス)は、複雑なタイミング動作を示す必要があります。これらの動作は、パフォーマンスを最適化するためにInnateraのSDKを介して調整できます。

Innateraは、そのチップをアナログ混合信号または「デジタルアシストアナログ」と表現しています。ニューロンとシナプスは、超低消費電力を維持するためにアナログシリコンに実装されています。アナログ電子機器は、連続時間ネットワークも可能にします(デジタル電子機器は離散化を必要とします)。これはSNNにとって重要です。なぜなら、SNNの性質は、本質的に時間の概念を持ち、一定期間にわたって特定の状態を保持できる必要があることを意味するからです。

「アナログドメインでは、これを行うのがはるかに簡単です。状態を維持する複雑さをネットワークトポロジに移す必要はありません」とKumar氏は述べています。 「私たちの計算要素は、当然、その状態情報を保持します。これが、私たちがアナログドメインで物事を行う理由です。」

Innateraの配列の計算セグメント。ニューロンは、注意深く一致するように設計されています。プログラム可能なシナプスは、マルチレベルのクロスバー構造に配置されています。 (ここでの黒い線/ダッシュは入力と出力のスパイクを表します)(画像:Innatera)

チップ上の計算要素間、および異なるチップ間の製造におけるわずかな不一致は、アナログドメインでニューラルネットワークを正確に実装するための問題になる可能性があります。 Innateraのソリューションは、ニューロンをセグメントと呼ばれるものにグループ化することです。セグメントは、パスの長さとニューロンの数に一致するように注意深く設計されています。

セグメント設計により、「基本的に、アナログ回路で通常発生するこれらの非理想性を最小限に抑えながら、最高のアナログ回路を使用できるようになります」とKumar氏は述べています。 「これはすべて、基本的に、セグメント内のニューロンが決定論的な動作を示し、隣接するニューロンと同様に機能することを確認するために行われました。」

異なるチップ間の不整合は、同じトレーニング済みネットワークがフィールド内のデバイスに展開されるときに問題を引き起こす可能性があります。 Innateraはソフトウェアでこれを回避します。

「不一致と変動性はSDKの奥深くで処理されます」とKumar氏は述べています。 「あなたがパワーユーザーであれば、その一部を公開することはできますが、一般的なプログラマーはそれについて気にする必要はありません。」

アプリケーション固有

デルフト工科大学からのスピンアウトであるInnateraは、ハードウェアに移行し、2020年末に向けて500万ユーロ(約600万ドル)のシードラウンドを調達する前に、すでに収益のある顧客とSNNアルゴリズムについて取り組んでいました。

>「私たちは実際に会社を設立して以来、多くの顧客と協力してきましたが、これらの取り組みは今も続いています。彼らは非常に成熟しています」とクマール氏は述べています。 「今年の後半に、これらの顧客の一部と一緒に、より多くのデモンストレーションを表示できるようになることを望んでいます。」

Kumar氏は、同社はコンピューティングソリューション企業としての焦点を維持している、つまり、ハードウェアとアプリケーション固有のSNNアルゴリズムの両方を含むターンキーソリューションを提供すると述べました。

Innateraの最初のチップは、オーディオ、ヘルス、レーダーのアプリケーションに適しています。会社のロードマップには、アプリケーションごとにさらに最適化されたチップを含めることができます。

「私たちは、さまざまなスパイキングニューラルネットワークを加速できるようにデバイスを設計しました」とKumar氏は述べています。 「[当社のチップ]は、これらのネットワークをアプリケーションドメイン全体に実装できます。しかし、ドメインを深く掘り下げると、ハードウェア設計を最適化する必要があるかもしれません。これは、将来的に検討するものです。現在、ハードウェアは特定のクラスのアプリケーションやスパイキングニューラルネットワークのスタイルに過度に特化しているわけではありません。目的は、一般的にアーキテクチャ内でさまざまなアプリケーションをサポートすることです。」

最初のチップのサンプルは、2021年の終わりまでに利用可能になる予定です。

>>この記事は、もともと姉妹サイトEEで公開されました。タイムズ。

>

関連コンテンツ:

- AIチップは低電力エッジデバイスを対象としています

- ツールチェーン、センサーボードはAIチップエコシステムを強化します

- 新しいAIアクセラレータモジュールがエッジパフォーマンスを強化します

- エッジのAI:2021年に何を探すべきか

- MCUにAIof Things(AIoT)を実装する方法

Embeddedの詳細については、Embeddedの週刊メールニュースレターを購読してください。

埋め込み

- Zynqベースの設計の協調シミュレーション

- ルネサス:日産が新しいスカイラインProPILOT2.0に採用した自動車用チップ

- CEVA:ディープニューラルネットワークワークロード用の第2世代AIプロセッサ

- AIコンピューティングのためのニューロモルフィックチップの主張

- 低電力レーダーチップはスパイキングニューラルネットワークを使用します

- Lanner:セルラーネットワーク上のIoTおよびSD-WAN用に認定されたLTE対応エッジゲートウェイ

- IBM at SPIE:7nmチップを超えた7つの進歩

- NPEはCampetellaRoboticCenterの米国デビューです

- 3Gは死んだ:製品設計者にとって次は何?

- LoRaWANは、IoT用の5Gネットワークを一時的に置き換えます

- ラティスセミコンダクターは、産業用自動化のために特別に設計されたチップを発売します