IBM at SPIE:7nmチップを超えた7つの進歩

2015年に業界初の機能的な7ナノメートルノード(7nm)テストチップを発表したとき、GLOBALFOUNDRIESとSamsungパートナーと一緒に、チップが「製造成熟度」に達するプロセスが、おそらく来年には早くなることを知っていました。半導体業界でその取り組みが加速する中、IBMは、7nmを超える次のノードの課題に焦点を当てることで限界を押し広げ続けています。

IBMチームは、今週の2017 International Society for Optics and Photonics(SPIE)AdvancedLithographyカンファレンスで7つの論文を発表しています。 7nmノードを超えた技術の探求と実現に焦点を当てています。そして、それは極紫外線(EUV)リソグラフィーから始まります。

IBMチームは、今週の2017 International Society for Optics and Photonics(SPIE)AdvancedLithographyカンファレンスで7つの論文を発表しています。 7nmノードを超えた技術の探求と実現に焦点を当てています。そして、それは極紫外線(EUV)リソグラフィーから始まります。

7nmチップを使用して、トランジスタのサイズ、さらにはトランジスタ間の配線に関連する、真に原子レベルの設計を作成しています。過度に複雑なパターニングスキームなしでこの種のスケーリングを実現するには、EUVが重要です。 EUVは、1回の露光で、以前の半導体パターニングプロセスでは達成できない高解像度パターンを作成できます。ただし、EUVパターニングを有効にするには、ニューヨーク州アルバニーとニューヨーク州ヨークタウンハイツにあるIBMの研究所にある特殊な機器、プロセス、およびノウハウが必要です。 SPIEで提示されたEUVマスク(回路設計をシリコンウェーハに印刷するために使用されるテンプレート)およびパターニング材料(光活性化「レジスト」または耐エッチング性材料)に関連するこれらの7つの進歩はすべて、7nm技術を実現する上で重要であると見なすことができます。およびそれ以降:

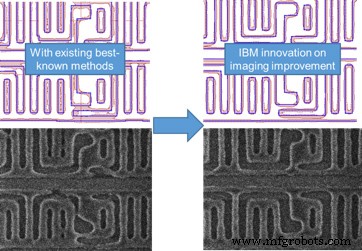

7nmノードを超えるノードでの設計意図の最適化:DTCOとEUVLの確率的緩和手法の共通部分 、マイケル・クルースは、彼の講演のタイトルが大きいにもかかわらず、配線設計の小さな変更が印刷条件を大幅に改善できることを示しています。図1で、彼は、マスク形状の最適化が正しく行われれば、7nmノード以降に必要な最小寸法で破損のない連続線を印刷できることを示しています。

図1 :EUVリソグラフィで実証された2次元金属配線のコントラスト最適化の改善。右に示すタイプの改善により、7nmノードの機能よりも小さい機能20-30 {ccf696850f4de51e8cea028aa388d2d2d2eef894571ad33a4aa3b26b43009887}をより堅牢に印刷でき、物理的/電気的変動を大幅に減らすことができます。

EUVリソグラフィーにおける代替マスクスタックの調査 Martin Burkhardtは、現在EUVマスクに使用されていない新しい材料の性能をシミュレートします。周期表全体を検討することにより、彼はさらに優れたコントラストを提供するEUVマスクが私たちの手の届くところにあることを説明することができます。これらの材料のいくつかを使用して実際にマスクを製造すると、EUV技術をさらに変更することなく、シリコンウェーハ上でより忠実なパターンが可能になり、業界は7nmを超えて簡単に拡張できるようになります。

EUVリソグラフィのラインエッジとライン幅の粗さの包括的な分析 、Ravi Bonamは、配線ラインの小さな欠陥や揺れを明確に特徴づける方法を示しています。そうすることで、EUVパターニングプロセスの製造可能性、およびチップの性能と歩留まりを向上させるために重要な、最も真っ直ぐな特徴を生み出す条件を示しています。

EUVレジストと無機ハードマスクの相互作用の基礎 、Dario Goldfarbは、これらのフィルム間の界面での物理的および化学的相互作用を改善することにより、パターン材料のフィルムスタック(パターンからウェーハへの転送ポイント)を改善することを目指しています。彼はこの理解を利用して、これらの材料を一緒に保持するための特定の化学的相互作用を作成します(図2を参照)。これは、これらの小さなEUVパターンの形状が、パターンを下の基板に転写するのに十分な時間、所定の位置に留まることができるようにするために重要です。

図2 :以前は無機シリコンハードマスクでパターン化できなかったEUVレジストを、レジスト/ハードマスクの組み合わせに合わせて表面をカスタマイズした後、明確にパターン化できるようになりました。

Dario Goldfarbの講演と同様のテーマで、Indira Seshadriは、ポリマーブラシを接着促進層として使用した極薄EUVパターニングスタックでデモンストレーションを行います。 、小さなEUVパターンの特徴と下にある基板の間を橋渡しするポリマーのような材料を採用することにより、これらの非常に高解像度のパターンを下の基板にエッチングし、意図した設計形状を維持することができます。これは、これらの長さで歩留まりの良いチップを確保するための鍵です。スケール。

非常に多くの新しい薄膜ソリューションが登場しているため、研究段階の早い段階で製造に値するプロセスを識別して改善する能力が重要です。 複合EUVパターニングフィルムスタックの欠陥密度の低下というタイトルの講演で 、Luciana Meliは、利用可能な欠陥検査技術のハイブリッドを使用して体系的なケーススタディを示し、7nm以上のEUV製造可能性に必要な低欠陥を実現するために必要なプロセスと材料の改善を示します。

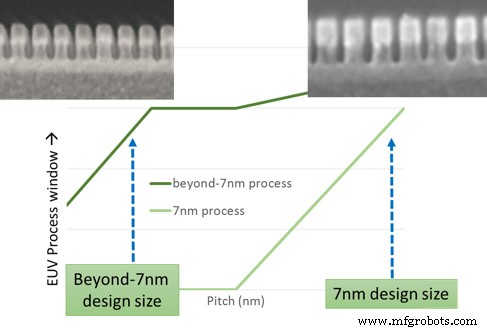

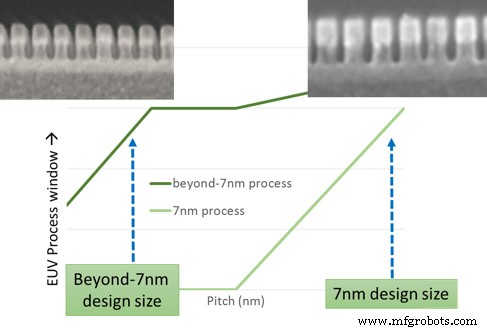

Anuja De Silvaは、イメージングと材料の改善に関するこれらの概念の多くをまとめて、 EUVリソグラフィの単一露光パターニング開発というタイトルの講演を行います。 、7nmノードを超えて必要な30nm以下の寸法での配線回路のパターン化の成功を示しています。これを達成する能力は、7nmノードで最初に利用可能になった機能からの大きな飛躍を表しており(図3を参照)、実際には7nmノード自体を改善できますが、彼女は、 7nmを超える技術に必要な寸法。

7nmチップには、ほぼ指の爪のサイズのスペースに200億個のトランジスタがあります。彼らはシステムやデバイスに参入し、機能を拡張し、ムーアの法則を拡張して、データ分析、コグニティブコンピューティング、および次世代のモバイルアプリが保持するあらゆるものでこれまで以上に要求の厳しいタスクを実行します。今年SPIEで発表された作業は、単一露光EUVで7nmプロセスをより堅牢にするだけでなく、今後数年間でさらに多くの電力/パフォーマンスの利点を実現するためのさらなるスケーリングを可能にするパターン化ソリューションに業界を近づけます。

>

図3 :パターン化プロセスの複数の側面に関する革新により、IBMは、7nmノードを超えて必要な機能サイズを提供する包括的なパターン化プロセス機能を提供できます。

2017SPIEでのその他のIBMプレゼンテーション

7nmノードを超えるノードでの設計意図の最適化:DTCOとEUVLの確率的緩和手法の共通部分 、Michael Crouse、Nicole Saulnier、Derren Dunn

EUVリソグラフィーにおける代替マスクスタックの調査 、Martin Burkhardt

リソグラフィ画像の計算を高速化するための非コヒーレントカーネルを使用したTCCの分解 アラン・ローゼンブルース

PEALD蒸着によるTi含有ハードマスクの開発 アヌジャデシルバ

ロジックおよびメモリアプリケーション用のDSAパターン化オプション チャーリー・リュー

EUVテストビークルを使用したサブ60nmでのDSA収縮プロセスとCD整流効果の電気的研究 チェンチー

高度なノードで真のオーバーレイに到達する Chiew-Seng Koay

全有機高χブロック共重合体の配向制御のためのトップコートフリー戦略 ダンサンダース

相関ベースルールシステム(デザインアーク)の識別と信頼性感度分析 エリックイーストマン

設計技術の共同最適化のための高度な高速3DDSAモデルの開発とキャリブレーション カファイライ

RIEガスのリソグラフィーフィルムへの予期しない影響 マーティングロード

ハイブリッド計測と機械学習を使用した電気試験の予測 メアリーブレトン

フォトニック導波路アプリケーションのRIE最適化によるSiおよびSiNのLERの削減 ネイサン・マルチャック

相変化メモリアプリケーション向けの自己組織化パターン化戦略 R.ブルース

マルチチャネルゲートオールアラウンド(GAA)デバイスのプロセス統合のための材料特性評価 Raja Muthinti

EUVリソグラフィのラインエッジとライン幅の粗さの包括的な分析 ラビボナム

ナノマテリアル

- チップ用タングステンチタン合金ターゲット

- 半導体チップ用の高純度タングステンターゲット

- 最良の結果を得るためにSkypeの最小ネットワーク要件を超える

- AIコンピューティングのためのニューロモルフィックチップの主張

- スパイキングニューラルネットワーク用のニューロモルフィックAIチップがデビュー

- IBMの科学者がナノスケール用の温度計を発明

- IBM 5 in 5:「オンチップ」の医療ラボは、ナノスケールで病気を追跡するための健康探偵として機能します

- IBM Researchers Take Home Innovation Prize for Semiconductor Research

- IBMがモノのインターネット向けのハイブリッドブロックチェーンアーキテクチャを発表

- AIOpsを超えて:効果的なIT運用のための可観測性

- 最適化された加工のための7つの要件