TIPS-ペンタセンベースの有機電界効果トランジスタの移動度と形態に及ぼすその場アニーリング処理の影響

要約

この研究では、下部ゲート上部接触構造を備えた有機電界効果トランジスタ(OFET)をスプレーコーティング法を使用して製造し、その場でのアニーリング処理がOFET性能に及ぼす影響を調査しました。従来のポストアニーリング法と比較して、60°Cのその場アニーリング処理によるOFETの電界効果移動度は、0.056から0.191 cm 2 にほぼ4倍向上しました。 /対。 TIPS-ペンタセン膜の表面形態と結晶化は、光学顕微鏡、原子間力顕微鏡、およびX線回折によって特徴づけられました。移動度の増加は、主に結晶化の改善と高度に秩序化されたTIPS-ペンタセン分子に起因することがわかりました。

背景

有機電界効果トランジスタ(OFET)は、柔軟な電子ペーパー、フラットパネルディスプレイ、RFID(Radio Frequency Identification)タグ、およびロジックサーカスでの実用的なアプリケーションの有望な候補としてかなりの注目を集めています[1,2,3,4、 5,6,7]。これまで、ブレードコーティング[6、8、9]、インクジェット印刷[10、11]、グラビア印刷[12、13]、最近登場したスプレー技術[14、15、16]などのいくつかの戦略があります。電子デバイスの製造のための効率的な方法であることが証明されました。これらの方法の中で、スプレーコーティングは製造におけるその独特の利点のために集中的に研究されてきました。スプレーコーティング法では、溶液濃度を低くする必要があるため、毒性の少ない溶媒への溶解度が低いさまざまな材料を適用できます[17]。さらに、スプレーコーティングにより、製造速度が向上し、さまざまな基板との適合性が向上し[18]、シャドウマスクを介してさまざまな形状のフィルムをパターン化できます[19]。さらに、スピンキャスティング、ブレードコーティング、グラビア印刷などの他の方法と比較して、スプレーコーティングプロセスでは、デバイスの最下層に損傷を与えることなく連続フィルムを実現できます。溶媒含有量、液滴サイズ、凝固を制御するだけです。ダイナミクス。

これまでの研究では、スプレーコーティングによって高性能OFETを実現するために、いくつかの新しい製造方法が適用されてきました。キムらスプレー印刷された有機半導体活性層を使用して製造されたOFETの性能に対する液滴サイズの影響を調査しました[16]。 Park etal。溶媒支援後処理法を使用して、溶媒含有量の集中的な研究を行いました[20]。一方、基板加熱は、半導体膜の結晶化度を高める効果的な方法であることが実証されています[21、22]。そのために、複数の研究が開発されました。 Sarcletti etal。有機半導体の移動度に対する表面エネルギーと基板温度の相互影響を研究しました[23]。また、Padma etal。誘電体/半導体界面での銅フタロシアニン薄膜の成長モードに対する基板温度の影響を調査しました[24]。続いて、Mikayelyan等。真空蒸着膜の構造と形態に及ぼす基板温度の影響を研究しました[25]。また、亀裂進展に対する熱焼鈍効果も調査されています[26]。多くの研究がデバイス製造技術の固有の電気的特性の改善に焦点を合わせていますが、スプレーコーティングされたOFETの研究分野におけるその場アニーリング処理の影響はあまり注目されていません。一方、OFETの従来の解決プロセスでは、通常、生産の中断とベーキング処理が必要であり、プロセスには時間がかかります。したがって、新しいアニーリング処理技術の開発は、スプレープロセスの可能性を最大限に活用するための重要なステップです。

この研究では、高性能OFETの製造に簡単なその場アニーリング処理を導入し、さまざまな基板温度をその場アニーリング処理に適用しました。 60°Cのその場アニーリング処理により、OFETデバイスの移動度は0.056から0.191 cm 2 に大幅に向上しました。 / Vsは、主に結晶化の改善に起因し、6,13-ビス(トリイソプロピル-シリルエチニル)ペンタセン(TIPS-ペンタセン)分子を秩序化させました。この性能向上のメカニズムを解明するために、光学顕微鏡、原子間力顕微鏡(AFM)、およびX線回折(XRD)を使用して、TIPS-ペンタセン膜の形態と結晶化を分析しました。私たちの研究は、単純なその場アニーリング処理で、その場アニーリング法の条件を注意深く制御することにより、効率的な製造プロセスを備えた高性能OFETを実現できることを示しています。

メソッド

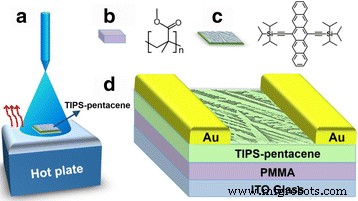

デバイス製造装置を図1(a)に示します。ポリ(メチルメタクリレート)(PMMA)と6,13-ビス(トリイソプロピル-シリルエチニル)ペンタセン(TIPS-ペンタセン)の化学構造をそれぞれ図1(b)と(c)に示します。 PMMA誘電体を使用したOFETのボトムゲート上部接触構成を図1(d)に示します。インジウムスズ酸化物(ITO)でコーティングされたガラスは、基板とゲート電極として使用されました。 OFETは次の手順で製造されました。まず、ポリテトラフルオロエチレン(PTFE)ホルダーに配置されたITOガラスを、洗剤、アセトン、脱イオン水、イソプロピルアルコールでそれぞれ15分間超音波洗浄しました。 PMMAは、100 mg / mLの濃度でアニソールに溶解しました。次に、ゲート誘電体として機能する520 nm PMMAフィルムを基板上にスピンコーティングし、150°Cで1時間空気中でベークして、溶媒の残留物を除去しました。第三に、30 nmのTIPS-ペンタセン活性層は、その場でのアニーリング処理を伴うスプレーコーティングプロセスを介してホットプレート上に配置された基板上に堆積され、TIPS-ペンタセン溶液の濃度はジクロロベンゼン中で3 mg / mLでした。実験中、スプレーコーティングの速度は20 µL / s、高さ(エアブラシから基板まで)は12 cmで、すべての実験は室温(20°C)で行われました。最後に、50 nmの厚さの金(Au)が、シャドウマスクによってTIPS-ペンタセン膜上にソース電極とドレイン電極として熱的に堆積されました。 TIPS-ペンタセンフィルムの厚さは、ステッププロファイラーによって特徴づけられました。純粋なPMMA層とPMMA / TIPS-ペンタセン層を別々に測定し、TIPS-ペンタセン膜の厚さを減算することで計算できます。デバイスのチャネル幅/長さの比率は100( L =100μm、 W =1 cm)。すべてのデバイスの電気的特性は、大気雰囲気下でケースレー4200ソースメーター(米国オハイオ州クリーブランド)を使用して測定されました。電界効果移動度(μ )は、飽和状態で| I の最も高い勾配から抽出されました。 DS | 1/2 対 V GS 次の方程式を使用してプロットします。

$$ {I} _ {\ mathrm {DS}} =\ left(W / 2L \ right)\ mu {C} _ {\ mathrm {i}} \ left({V} _ {\ mathrm {GS}} -{V} _ {\ mathrm {TH}} \ right)$$

a スプレーコーティングによるOFET製造の概略図。 b 、 c PMMAとTIPSの分子構造-ペンタセンと d この研究で使用されたOFETのデバイスアーキテクチャ

ここで私 DS はドレイン-ソース電流であり、 L (100μm)および W (1 cm)は、それぞれチャネルの長さと幅です。 C i は誘電体層の単位あたりの静電容量であり、 V GS および V TH はそれぞれゲート電圧とスレッショルド電圧です。 TIPS-ペンタセンの表面形態は、光学顕微鏡(U-MSSP4、OLYMPUS)および原子間力顕微鏡(AFM)(MFP-3D-BIO、Asylum Research)を使用してタッピングモードで特性評価され、構造特性は加速電圧30kV、印加電流20 mAでの粉末X線回折(XRD、TD-3500、Dandong、中国)。

結果と考察

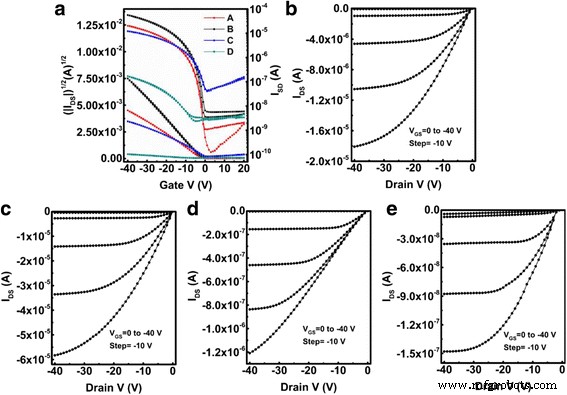

20分間の120°Cのポストアニーリング処理に基づくOFETはデバイスAとして製造され、60、90、および120°Cの温度でのその場アニーリング処理に基づくOFETはデバイスB、C、およびDとして製造されました。 、 それぞれ。ソース-ドレイン電圧( V でテストされた典型的な伝達特性 DS )-40 Vおよびゲート電圧( V GS )20〜-40 Vがテストされ、図2aに示されています。出力特性は V でテストされました DS −40Vおよび V GS 図2b–eに示すように、-10 Vのステップで0〜-40Vになります。飽和電流( I )を含むいくつかの基本的なパラメータ on )、電界効果移動度(μ )、しきい値電圧( V T )、サブスレッショルドスイング(SS)、およびオン/オフ比( I on / 私 オフ )、OFETの性能を評価するために使用できるものを表1にまとめています。

a デバイスA〜Dの伝達曲線。 b – e デバイスA、B、C、およびDのそれぞれの出力曲線

当然のことながら、すべてのデバイスが典型的なp型トランジスタの特性を示しました。その場でのアニーリング処理がOFETの電子特性に多大な影響を与えることがはっきりとわかります。特に、60°Cのその場アニーリング処理により、 V の正のシフトを含め、OFETの電気的性能が正常に向上しました。 TH (-1.7から-0.9 V)、および増加するμ (0.056〜0.191 cm 2 / Vs);デバイスBの移動度はポストアニーリングされたデバイスAの移動度のほぼ4倍です。ただし、90°Cのその場アニーリング処理を適用すると、順方向ドリフトを含む基板温度の上昇に伴い、デバイスのパフォーマンスが大幅に低下します。 V の TH -0.9から2.0Vになり、μが減少します。 0.191〜0.04 cm 2 の範囲 /対。さらに、その場でのアニーリング温度が120°Cに上昇すると、事態はさらに悪化し、 I が明らかに低下します。 on 12.1〜0.17μAおよびμ 0.04〜0.0005 cm 2 / Vsが得られました。その結果、デバイスCおよびDのパフォーマンスは、ポストアニールされたデバイスAよりもはるかに劣っていました。

異なるアニーリング処理を用いたスプレーコーティング法によって調製されたOFETの代表的な伝達および出力プロットを図2に示します。デバイスBは、ゼロに近いしきい値電圧と狭いしきい値下スイングを含む、最高の電気的性能を示すことがはっきりとわかります。 。しかしながら、その場でのアニーリング処理における基板温度の上昇に伴い、電気的性能の減衰が明らかになった。サブスレッショルドスイングは、その場でのアニーリング温度とともに明らかな増加傾向を示しました。これは、誘電体層と半導体層の間の界面でのトラップ密度が比較的高いことを意味します[27]。

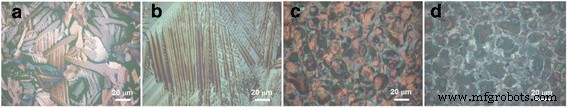

TIPS-ペンタセンフィルムの表面形態を精査するために、光学顕微鏡を使用しました。図3に示すように、TIPS-ペンタセン膜の多様な形状と形態が得られ、光学顕微鏡からは明らかに異なる結晶粒径を見ることができます。大きな結晶粒が図3a、bに示され、60°Cのその場アニーリング処理を施したTIPS-ペンタセン膜ははるかに均一であり、細くて長い粒がチャネルの方向に沿って成長していることがわかります。これは、TIPS-ペンタセン分子のより良い組織化を示しており、OFETデバイスのより良い電気的性能をもたらします。ただし、テンプレートの温度が90または120°Cに上昇すると、図3c、dに示すように、デバイスCおよびDに小さな粒子の円形の形態が現れ始めます。以前の研究によると、TIPS-ペンタセン膜の形態の変化は、OFETデバイスの電気的特性の変化につながるでしょう[28、29、30]。

スプレーコーティングされたTIPS-ペンタセン層の光学顕微鏡画像。 a 室温の基板温度に続いて、120°Cで20分間のポストアニーリング、 b – d それぞれ60、90、120°Cのその場アニーリング温度

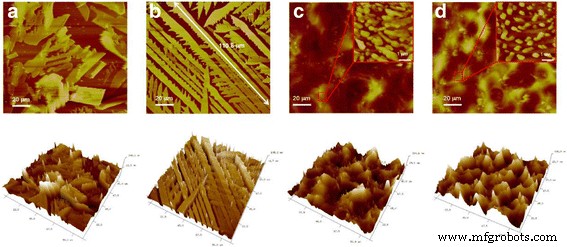

さらに、AFMを使用して、スプレーコーティングされたTIPS-ペンタセンフィルムの形態を特徴付けました。図4bに示すように、PMMA誘電体上に秩序だったTIPS-ペンタセン粒子が形成されますが、図4aにはさまざまな形状の不規則な結晶粒子が示され、図3aおよびbの光学顕微鏡画像とよく一致します。興味深いことに、基板温度が60°Cを超えると、TIPS-ペンタセン膜の形態に大きな変化が見られます。図4c、dは、高密度の小さなTIPS-ペンタセン粒子を含む典型的なスプレーされた丸い形態を示しています。これらの粒子は、挿入図に示すように、さまざまなサイズの多くの島クラスターからなる微結晶形態を示します。さらに、アニーリング温度を120°Cにさらに上げると、はるかに小さな粒子配列が形成され、結晶粒界が豊富なまばらな分布になり、キャリア輸送に悪影響を及ぼします[16、31、32]。このような結果は、アニーリング温度が膜形成特性に大きく影響し、膜の形態に大きな違いをもたらす可能性があることを示しています。

スプレーコーティングされたTIPS-ペンタセン層のAFM高さと3D画像。 a RTの基板温度(120°Cで20分後のアニーリングが続きます)。 b – d それぞれ60、90、120°Cのその場アニーリング温度。 インセット :高倍率AFM;インサートのスキャンサイズバーは1μmです

ご覧のとおり、基板温度の変化により、形態と粒子サイズが異なります。そして、デバイスBの最大の形態は、適切なアニーリング温度だけでなく、分子の自己組織化に適した条件にも起因する可能性があります。 OFETを比較的低い基板温度で調製すると、溶媒の穏やかな蒸発を維持できるため、溶媒の蒸発速度が低下し、連続する液滴によってフィルムが濡れたままになります。実際、この基板温度の変調は、溶媒の蒸発速度に直接影響します。より低いアニーリング温度は、TIPS-ペンタセン結晶が秩序だった分子とともにゆっくりと成長することを可能にし[33]、より高い基板温度は、溶媒の比較的遅い乾燥プロセスなしで、迅速な凝固に貢献します[34]。したがって、スプレープロセス中の分子の自己組織化により長い時間が得られました。これは、より高度な相分離とより大きなドメインサイズの原因となります[33、35、36]。その結果、細くて長い粒子が形成され、チャネル領域でのキャリア輸送用のブリッジは、110.8μmより長いこれらの長い粒子を介して構築できます[37]。

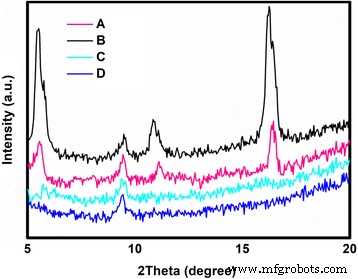

スプレーコーティングされたTIPS-ペンタセンフィルムの分子配向とパッキングをさらに調査するために、XRDが導入されました。図5に示すように、個々のトレースは、反射(00 l )に割り当て可能な一連の狭いブラッグピークを示します。 )のTIPS-ペンタセン[38]であり、密度は、基板温度がTIPS-ペンタセン分子の結晶化度に劇的に影響することを示しています[39]。ポストアニーリング処理を施したデバイスAと比較して、デバイスBのピーク強度は最も強く、TIPS-ペンタセン膜の顕微鏡写真と一致しており、60°Cのinsituアニーリング処理で堆積したTIPS-ペンタセンが最高の結晶化度をもたらすことを示しています。 TIPS-ペンタセンの。基板温度が90°Cと120°Cに上昇すると、TIPS-ペンタセンの劣った秩序が形成され、これがデバイスの性能低下の原因となりました[40]。

ポストアニーリングとinsituアニーリング処理の両方を使用したスプレーコーティングされたTIPS-ペンタセンフィルムの正規化されたXRDスペクトル

結論

要約すると、TIPS-ペンタセンにその場アニーリング処理をスプレーコーティングすることによってOFETを製造およびテストし、得られた膜の表面形態と結晶化を調査しました。結果は、TIPS-ペンタセンベースのOFETの電気的性能が活性層の処理条件と強い相関関係があることを示しています。テンプレート温度が60°Cの場合、その場アニーリング法で製造されたOFETの移動度は0.056から0.191 cm 2 に増加します。 /対。性能の向上は、より高い結晶化と秩序化された粒子に起因していました。スプレーコーティング法のこのinsituアニーリング処理は、高性能OFETの製造に効果的な方法であるだけでなく、低コストの製造とアプリケーションの多様性の可能性が高いと期待されています。

ナノマテリアル

- 最高品質のオーガニックスパイスとプレミアムサービスをお客様にお届けします!

- ICAをロードしたmPEG-ICAナノ粒子の調製とLPS誘発性H9c2細胞損傷の治療におけるそれらの応用

- 色素増感太陽電池の光学的および電気的特性に及ぼすTiO2中の金ナノ粒子分布の影響

- MnХFe3−XО4スピネルの構造的および磁気的特性に及ぼす接触非平衡プラズマの影響

- NiO光電陰極に及ぼすポリエチレングリコールの影響

- ヘリウム水素を順次注入したバナジウム合金の微細構造と硬化に及ぼす焼鈍の影響

- 金属および金属酸化物ナノ粒子のグリーン合成と単細胞藻類Chlamydomonasreinhardtiiに対するそれらの効果

- チタニアナノチューブの熱伝導率に及ぼす形態と結晶構造の影響

- 階層的SnO2ブルーミングナノフラワーの微細構造とそれらのガス検知特性に及ぼす界面活性剤の影響

- 廃水処理と管理におけるIoTの概念を理解する

- テンパリングとアニーリングの違い