FPGAを使用した組み込み設計:ハードウェアリソース

編集者注:スマートな製品設計のための高度なアルゴリズムが出現し続けるにつれて、開発者は、これらのアルゴリズムに関連する処理要求を満たすことができる組み込みシステムの実装に苦労することがよくあります。 FPGAは必要なパフォーマンスを提供できますが、FPGAを使用したデザインは、FPGAプログラミングの専門家の権限に限定されると長い間考えられてきました。しかし、今日では、より強力なFPGAとより効果的な開発環境が利用できるようになり、FPGA開発に幅広くアクセスできるようになりました。この抜粋、 『Architecting High-Performance Embedded Systems』の第4章では、FPGAデバイス、実装言語、FPGA開発プロセスの包括的なレビューと、FPGAの実装を開始する方法の詳細なウォークスルーを提供しています。設計。完全な抜粋は、次の一連の記事で紹介されています。

編集者注:スマートな製品設計のための高度なアルゴリズムが出現し続けるにつれて、開発者は、これらのアルゴリズムに関連する処理要求を満たすことができる組み込みシステムの実装に苦労することがよくあります。 FPGAは必要なパフォーマンスを提供できますが、FPGAを使用したデザインは、FPGAプログラミングの専門家の権限に限定されると長い間考えられてきました。しかし、今日では、より強力なFPGAとより効果的な開発環境が利用できるようになり、FPGA開発に幅広くアクセスできるようになりました。この抜粋、 『Architecting High-Performance Embedded Systems』の第4章では、FPGAデバイス、実装言語、FPGA開発プロセスの包括的なレビューと、FPGAの実装を開始する方法の詳細なウォークスルーを提供しています。設計。完全な抜粋は、次の一連の記事で紹介されています。

1:ハードウェアリソース(この記事)

2:実装言語

3:開発プロセス

4:プロジェクトの構築

5:実装

ジム・レディンによる「高性能組み込みシステムの設計」から採用。

>

最初のFPGAプログラムの開発

この章では、リアルタイム組み込みシステムでのFPGAデバイスの効果的な使用について説明し、標準のFPGAに含まれる機能要素について説明します。 ハードウェアを含むFPGAデザイン言語の範囲 説明言語 ( HDL )、ブロック線図法、およびCやC ++を含む一般的なソフトウェアプログラミング言語が紹介されています。この章では、FPGA開発プロセスの概要を説明し、システム要件の説明から始まり、低コストのFPGA開発ボードに実装された機能システムで終わるFPGA開発サイクルの完全な例で締めくくります。

この章を完了すると、FPGAをリアルタイム組み込みシステムアーキテクチャに適用する方法を理解し、FPGA集積回路を構成するコンポーネントを理解できるようになります。 FPGAアルゴリズムの設計で使用されるプログラミング言語について学習し、FPGAベースのアプリケーションを開発するための一連の手順を理解します。また、無料のFPGAソフトウェアツールを使用して、低コストの開発ボードで完全なFPGA開発例を実行しました。

この章では、次のトピックについて説明します。

- リアルタイム組み込みシステム設計でのFPGAの使用

- FPGA実装言語

- FPGA開発プロセス

- 最初のFPGAプロジェクトの開発

技術的要件

この章のファイルは、https://github.com/PacktPublishing/Architecting-High-Performance-Embedded-Systemsで入手できます。

リアルタイム組み込みシステム設計でのFPGAの使用

FPGAの要素で見たように 第1章のセクション 、ハイパフォーマンスの設計 組み込みシステム 、一般的なFPGAデバイスには、多数のルックアップテーブル、フリップフロップ、ブロックRAMエレメント、DSPスライス、およびその他のコンポーネントが含まれています。これらの各コンポーネントの詳細な機能を理解することは有益ですが、そのような懸念はFPGA開発プロセス中に必ずしも有益ではありません。覚えておくべき最も重要な制約は、特定のFPGAパーツ番号にはこれらの各要素が有限数含まれていることであり、その特定のFPGAモデルを対象とした場合、デザインはこれらの制限を超えることはできません。

代わりに、組み込みシステムの要件ステートメントの観点からFPGA開発プロセスを表示する方が生産性が高くなります。やや任意に選択したFPGAモデルを対象としたFPGAデザインの開発を開始できます。開発が進むにつれて、リソースの制限に達するか、現在ターゲットになっているFPGAには存在しないデザインに必要なFPGA機能を特定する可能性があります。その時点で、別の、より有能なターゲットを選択して、開発を続けることができます。

または、デザインの開発が完了に近づくと、最初に選択したターゲットFPGAに過剰なリソースが含まれていることに気付く場合があります。より小さなFPGAを選択することでデザインを改善でき、コストの削減、ピンの削減、パッケージサイズの削減などのメリットがあります。消費電力を削減します。

これらの状況のいずれにおいても、ターゲットFPGAを同じファミリ内の別のモデルに切り替えるのは一般的に簡単です。これまでに作成した開発ツールとデザインアーティファクトは、新しくターゲットにしたFPGAモデルで完全に再利用できるはずです。同じベンダーのFPGAの別のファミリ、または別のベンダーのモデルに切り替える必要が生じた場合、切り替えにはさらに多くの作業が必要になる可能性があります。

この議論のポイントは、高性能組み込みシステム開発の取り組みの最初に特定のFPGAモデルを特定することはそれほど重要ではないことを強調することです。代わりに、初期の検討事項では、設計の一部としてFPGAを使用するという決定を検証することに焦点を当てる必要があります。次に、FPGAが最適な設計アプローチである場合は、適切なFPGAベンダーとデバイスファミリの選択に進みます。

この本のサンプルプロジェクトは、FPGA開発ツールのザイリンクスVivadoファミリに基づいています。一部のザイリンクスFPGAファミリ用に開発するには、Vivadoライセンスを購入する必要がありますが、使用するArtix-7のFPGAデバイスはVivadoで無料でサポートされています。 Artix-7 FPGAファミリは、高性能、低消費電力、および総システムコストの削減という属性を兼ね備えています。同様のFPGAデバイスファミリと開発ツールスイートは、他のFPGAベンダーから入手できます。

FPGAの開発はかなり複雑なプロセスであり、さまざまなタイプの分析と設計データの入力が必要です。これらのトピックを抽象的すぎるレベルで説明することを避け、実際のサンプルプロジェクトの観点から具体的な結果を提示するために、本全体でVivadoを使用します。ここで説明するツールと手法に慣れたら、他のベンダーの同様のツールを使用してそれらを適用できるようになります。

次のセクションでは、FPGAファミリとそれらのファミリ内の個々のモデルのいくつかの重要な差別化機能について説明します。これには、ブロックRAMの量、使用可能なI / O信号の量と種類、専用のオンチップハードウェアリソース、およびFPGAパッケージ内の1つ以上のハードウェアプロセッサコア。

ブロックRAMと分散RAM

RAMをブロックする FPGA内にメモリの領域を実装するために使用されます。特定のメモリ領域は、ビット単位の幅(通常は8ビットまたは16ビット)と、メモリ領域内の格納場所の数を定義する深さで指定されます。

FPGAのブロックRAMの総量は、通常、キロビットで指定されます。 ( Kb )。使用可能なブロックRAMの量は、FPGAファミリ間および特定のファミリ内のモデル間で異なります。ご想像のとおり、より大きく、より高価な部品には、通常、ブロックRAMとして使用できるリソースの量が多くなります。

ザイリンクスFPGAでは、また他のベンダーのFPGAでも程度は異なりますが、ブロックRAMに加えて、分散RAMと呼ばれる別のカテゴリのメモリを使用できます。 分散RAM ルックアップテーブルで使用されるロジック要素から構築され、これらのデバイスの回路を再利用して、それぞれが16ビットを含むRAMの小さなセグメントを形成します。これらのセグメントは、必要に応じて集約して、より大きなメモリブロックを形成できます。

ブロックRAMは、プロセッサキャッシュメモリの実装やI / Oデータのストレージバッファなど、従来RAMに関連付けられていた目的で使用される傾向があります。分散RAMは、中間計算結果の一時的な保存などの目的で使用される場合があります。分散RAMはルックアップテーブル回路に基づいているため、デザインで分散RAMを使用すると、ロジック操作の実装に使用できるリソースが削減されます。

ブロックRAMは、シングルポートまたはデュアルポートを持つことができます。シングルポートブロックRAMは、動作中にRAMの読み取りと書き込みを行うプロセッサの一般的な使用パターンを表します。

デュアルポートブロックRAMは、2つの読み取り/書き込みポートを提供します。どちらも同じメモリ領域を同時にアクティブに読み取りまたは書き込みできます。

デュアルポートブロックRAMは、異なるクロック速度で動作するFPGAの一部間でデータが転送される状況に最適です。たとえば、I / Oサブシステムは、着信データストリームを受信するときに、数百MHzのクロック速度を持つ場合があります。 I / Oサブシステムは、FPGAの高速I / Oチャネルの1つを介して到着するときに、着信データをブロックRAMに書き込みます。異なるクロック速度で動作するFPGA内の別のサブシステムは、I / Oサブシステムの動作を妨げることなくブロックRAMの2番目のポートからデータを読み取ることができます。

ブロックRAMは、先入れ先出しでも動作します。 ( FIFO )モード。着信シリアルデータストリームの例では、I / Oサブシステムはデータワードが到着したときにFIFOに挿入でき、処理サブシステムは同じ順序でデータワードを読み取ることができます。 FIFOモードのブロックRAMは、FIFOが満杯、空、ほぼ満杯、またはほぼ空のいずれであるかを示す信号を提供します。 ほぼ完全の定義 およびほとんど空 システム設計者次第です。 ほぼ空を割り当てた場合 FIFOに残っているアイテムが16未満であることを意味するため、FIFOがほとんど空であると示さない場合はいつでも、データの可用性をさらにチェックしなくても16アイテムを読み取ることができます。

ブロックRAMをFIFOモードで使用する場合、FIFOにアイテムを挿入するロジックは、FIFOがいっぱいのときに書き込みを試行せず、FIFOからのロジック読み取りは、FIFOが空のときに読み取りを試行しないことが重要です。これらのイベントのいずれかが発生すると、システムはデータを失うか、未定義のデータの処理を試みます。

FPGA I / Oピンと関連機能

FPGAは高性能アプリケーションでの使用を目的としているため、FPGAのI / Oピンは通常、さまざまな高速I / O規格を実装できます。 FPGA開発ツールスイートを使用したデザインの実装中に、システム開発者は、FPGAパッケージの特定のピンに機能を割り当て、適切なインターフェイス規格で動作するように各ピンを構成するなどのタスクを実行する必要があります。 FPGAモデルコード内の入力信号と出力信号を正しいパッケージピンに関連付けるには、追加の手順を実行する必要があります。

ピンレベルでは、個々のI / O信号はシングルエンドまたは差動のいずれかです。

シングルエンド信号 アースを基準にしています。従来のトランジスタ-トランジスタロジック ( TTL )および相補型金属酸化膜半導体 ( CMOS )デジタル信号は、グランドに対して0〜5VDCの範囲で動作します。

最新のFPGAは通常、従来の5 VDC信号範囲をサポートしていませんが、代わりに、低電圧範囲で動作するTTLおよびCMOS信号をサポートしているため、消費電力が削減され、速度が向上します。 低電圧TTL ( LVTTL )信号は0〜3.3VDCの範囲で動作します。 低電圧CMOS ( LVCMOS )信号は、1.2、1.5、1.8、2.5、および3.3 Vの信号電圧で選択できます。これらの信号タイプは、LVCMOS12、LVCMOS15、LVCMOS18、LVCMOS25、およびLVCMOS33と呼ばれます。 高速トランシーバーロジックなど、他の高性能シングルエンド信号タイプも利用できます。 ( HSTL )およびスタブシリーズ終端ロジック ( SSTL 。

シングルエンド信号は、押しボタン入力の読み取りやLEDの点灯など、低周波の目的で広く使用されています。シングルエンド信号は、I2CやSPIなどの多くの低速通信プロトコルでも使用されます。シングルエンド信号の重要な欠点は、信号を伝送するワイヤおよびプリント回路基板のトレースに結合されたノイズが、受信機への入力を破壊する可能性があることです。この問題は、差動信号を使用することで大幅に減らすことができます。

最高のデータ転送速度を得るには、差動シグナリングが推奨されるアプローチです。

差動信号 一対のI / Oピンを使用し、反対の信号を2つのピンに駆動します。

言い換えると、一方のピンはより高い電圧に駆動され、もう一方のピンはより低い電圧に駆動されて0データビットを表し、ピン電圧は逆になって1ビットを表します。差動受信機は2つの信号を減算して、データビットが0か1かを判断します。差動信号を伝送する2つのワイヤまたはトレースは物理的に非常に接近して配置されているため、一方の信号に結合するノイズはもう一方の信号に結合します。非常によく似た方法で。減算操作はノイズの大部分を除去し、シングルエンド信号よりもはるかに高いデータ転送速度で信頼性の高い操作を可能にします。

多くの差動信号規格が標準FPGAでサポートされています。 HSTLとSSTLのいくつかの差動バージョンが定義されており、それぞれにさまざまな信号電圧レベルがあります。

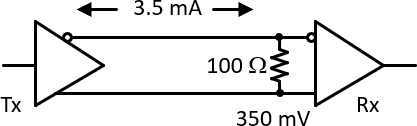

低電圧差動信号 ( LVDS )は1994年に標準として導入され、さまざまなアプリケーションで使用され続けています。 LVDSシグナリングトランスミッタは3.5mAの定電流を生成し、レシーバの抵抗を流れる電流の方向を切り替えて、図4.1 に示すように0と1のデータ値を表す状態変化を生成します。 :

図4.1–LVDSインターフェース

LVDS通信では、他の差動およびシングルエンド信号規格と同様に、送信機と受信機の間の通信パスのインピーダンスが終端インピーダンス(LVDSの場合は100オーム)と厳密に一致することが重要です。通信チャネルのインピーダンスが終端インピーダンスと一致しない場合、回線上で反射が発生し、信頼性の高いデータ受信が妨げられる可能性があります。

差動信号トレースペアのインピーダンスは、ペアトレースの形状とグランドプレーンとの関係の関数です。 第6章で見るように 、 KiCadを使用した回路の設計 、高速差動信号規格の要件を満たす回路基板を設計するのは簡単です。

特殊なハードウェアリソース

FPGAには通常、一般的に必要とされる機能専用のハードウェアリソースが含まれており、合成されたFPGA機能を使用するよりもハードウェアに効率的に実装されるか、FPGAコンポーネントで実装できません。これらのリソースの例を次に示します。

- 外部ダイナミックRAMへのインターフェース ( DRAM )これらのインターフェイスを大量に保存する場合、通常、DDR3などの一般的なDRAM規格をサポートします。

- アナログ-デジタル変換器。

- フェーズロックループ。複数のクロック周波数を生成するために使用されます。

- デジタル信号処理積和 ( MAC )ハードウェア。

これらのハードウェアリソースにより、幅広い機能を備えた複雑なシステムの開発が可能になります。ハードウェアのパフォーマンスは、FPGAロジックリソースを使用して合成された同等の機能よりも大幅に優れているため、MAC操作などの機能専用のハードウェアが提供されます。

プロセッサコア

一部のFPGAファミリには、ソフトウェアのピーク実行速度とFPGAで実装されたアルゴリズムのパフォーマンス上の利点を組み合わせる目的でハードウェアプロセッサコアが含まれています。たとえば、ザイリンクスZynq-7000ファミリは、ハードウェアARMCortex-A9プロセッサを従来のFPGAファブリックと統合しています。

ハードウェアプロセッサを必要としないFPGAデザインは、ソフトプロセッサと呼ばれるFPGAリソースを使用してプロセッサを実装できます。 。ソフトプロセッサは高度に構成可能ですが、通常、ハードウェアに実装されているプロセッサのパフォーマンスに匹敵することはできません。

次のセクションでは、FPGAアルゴリズムの開発に使用される主要なプログラミング言語とデータ入力方法を紹介します。

PacktPublishingの許可を得て転載。 Copyright©2021Packt Publishing

>

ジム・レディン Ledin Engineering、Inc。のCEOです。Jimは、組み込みソフトウェアおよびハードウェアの設計、開発、およびテストの専門家です。彼はまた、組み込みシステムのサイバーセキュリティ評価と侵入テストでも活躍しています。彼は理学士号を持っていますアイオワ州立大学で航空宇宙工学の学位を取得し、M.S。ジョージア工科大学で電気およびコンピューター工学の学位を取得。ジムは、カリフォルニアで登録された専門の電気技師、Certified Information System Security Professional(CISSP)、Certified Ethical Hacker(CEH)、およびCertified Penetration Tester(CPT)です。

ジム・レディン Ledin Engineering、Inc。のCEOです。Jimは、組み込みソフトウェアおよびハードウェアの設計、開発、およびテストの専門家です。彼はまた、組み込みシステムのサイバーセキュリティ評価と侵入テストでも活躍しています。彼は理学士号を持っていますアイオワ州立大学で航空宇宙工学の学位を取得し、M.S。ジョージア工科大学で電気およびコンピューター工学の学位を取得。ジムは、カリフォルニアで登録された専門の電気技師、Certified Information System Security Professional(CISSP)、Certified Ethical Hacker(CEH)、およびCertified Penetration Tester(CPT)です。 >

関連コンテンツ:

- オープンソースツールはFPGAプログラミングを簡素化するのに役立ちます

- FPGAまたはASICでの浮動小数点アルゴリズムの実装

- ディープラーニングにFPGAを活用する

- ソフトウェアツールは、AIアプリケーション用にGPUコードをFPGAに移行します

- FPGAはスバルEyesightビジョンベースADASのASICに取って代わります

- フラッシュベースのFPGAが機能安全要件をどのように簡素化するか

- インスタントオンFPGAのメリットを享受する

- 高速NORフラッシュを使用したFPGA構成

- 新しいミッドレンジシステム要件を満たすためにFPGAテクノロジがどのように進化しているか

Embeddedの詳細については、Embeddedの週刊メールニュースレターを購読してください。

埋め込み

- 接続されたハードウェア設計でコストのかかる驚きを回避する方法

- 組み込みシステム設計とは:設計プロセスのステップ

- EclipseIoTによるIoT開発の簡素化

- テスト駆動開発によるステートマシンの開発

- AIが組み込まれたビッグデータをスマートデータに変換

- コミュニティ主導のリソースは、ハードウェア設計のセキュリティの弱点を追跡します

- サイプレス:ModusToolbox Suiteは、IoT設計の複雑さを緩和します

- ラティス:MachX03D FPGAは、ハードウェアの信頼のルート機能でセキュリティを強化します

- デザインキットは、光学センサーで血圧を測定します

- Java 9 - リソースの改善を試す

- 添加物を含むすべて