FPGAを使用した組み込み設計:プロジェクトの構築

編集者注:スマートな製品設計のための高度なアルゴリズムが出現し続けるにつれて、開発者は、これらのアルゴリズムに関連する処理要求を満たすことができる組み込みシステムの実装に苦労することがよくあります。 FPGAは必要なパフォーマンスを提供できますが、FPGAを使用したデザインは、FPGAプログラミングの専門家の権限に限定されると長い間考えられてきました。しかし、今日では、より強力なFPGAとより効果的な開発環境が利用できるようになり、FPGA開発に幅広くアクセスできるようになりました。この抜粋、 『Architecting High-Performance Embedded Systems』の第4章では、FPGAデバイス、実装言語、FPGA開発プロセスの包括的なレビューと、FPGAの実装を開始する方法の詳細なウォークスルーを提供しています。設計。完全な抜粋は、次の一連の記事で紹介されています。

編集者注:スマートな製品設計のための高度なアルゴリズムが出現し続けるにつれて、開発者は、これらのアルゴリズムに関連する処理要求を満たすことができる組み込みシステムの実装に苦労することがよくあります。 FPGAは必要なパフォーマンスを提供できますが、FPGAを使用したデザインは、FPGAプログラミングの専門家の権限に限定されると長い間考えられてきました。しかし、今日では、より強力なFPGAとより効果的な開発環境が利用できるようになり、FPGA開発に幅広くアクセスできるようになりました。この抜粋、 『Architecting High-Performance Embedded Systems』の第4章では、FPGAデバイス、実装言語、FPGA開発プロセスの包括的なレビューと、FPGAの実装を開始する方法の詳細なウォークスルーを提供しています。設計。完全な抜粋は、次の一連の記事で紹介されています。

1:ハードウェアリソース

2:実装言語

3:開発プロセス

4:プロジェクトの構築(この記事)

5:実装

ジム・レディンによる「高性能組み込みシステムの設計」から採用。

最初のFPGAプロジェクトの開発

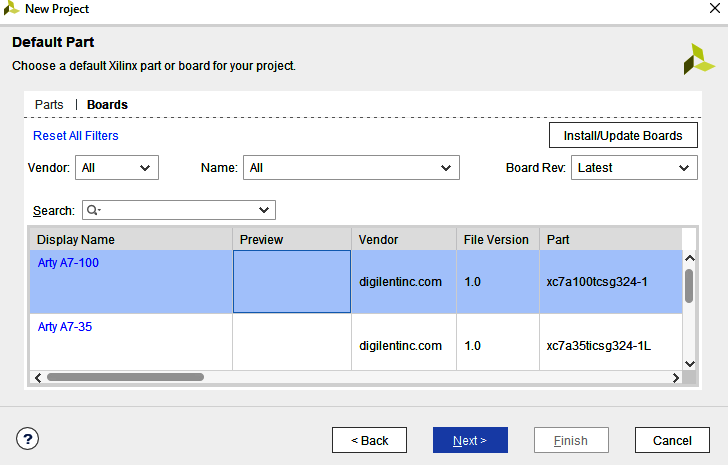

このセクションでは、Digilent ArtyA7開発ボードにインストールされたザイリンクスArtix-7FPGAデバイスを使用して、シンプルでありながら完全なプロジェクトを開発および実装します。このボードには2つのバリエーションがあります。モデル番号が-35Tで終わる低コストバージョン(US $ 129)と、モデル番号が-100Tで終わるより高性能で高価なバージョン(US $ 249)です。 2つのボードの唯一の違いは、ボードにインストールされているArtix-7FPGAのモデルです。ご想像のとおり、-35Tのリソースは-100Tよりも少なくなっています。

このプロジェクトでは、-35Tまたは-100Tバリアントのいずれかを使用できます。開発プロセスの唯一の違いは、必要に応じて正しいボードモデルを指定することです。ただし、後の章では、デジタルオシロスコーププロジェクトの設計例のリソース要件のために-100Tバリアントが必要になるため、より高性能なボードをお勧めします。

Arty A7ボードは、https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/や、Amazonなどの他のソースから購入できます。

このプロジェクトの目的では、対象のボード上のリソースは、FPGAデバイス自体、および4つのスイッチ、4つのプッシュボタン、および5つのLEDです。このプロジェクトでは、Vivadoツールスイートをインストールし、プロジェクトを作成し、HDLコードを入力し、コードをテストし、最終的にビットストリームを生成してボードにダウンロードする方法を示します。ボードにビットストリームをダウンロードした後、システムの動作を手動でテストできるようになります。また、Arty A7ボードのフラッシュメモリにFPGAイメージをプログラムして、ボードの電源がオンになるたびにロードおよび実行されるようにする方法についても説明します。

プロジェクトの説明

このプロジェクトでは、FPGAに4ビットのバイナリ加算器を実装します。ここでは、複雑なHDLモデルの実装ではなく、ツールのセットアップと使用方法の学習に重点を置いているため、これは意図的に非常に単純な設計です。

ボード上の4つのスイッチは1つの4ビット2進数を表し、4つのプッシュボタンは別の4ビット番号を表します。 FPGAロジックは、これら2つの数値の間で加算演算を継続的に実行し、結果を4つのLEDに4ビットの2進数として表示し、5番目のLEDはキャリービットを表します。

4ビット加算器コードは、ハードウェア設計言語で説明されているシングルビット全加算器回路に基づいています。 第1章のセクション 、高性能組み込みシステムの設計 。

Vivadoツールのインストール>

このプロジェクトおよび今後の章のプロジェクトでは、FPGA開発ツールのザイリンクスVivadoスイートを使用します。これらのツールは無料で利用でき、WindowsおよびLinuxオペレーティングシステムでサポートされています。ツールはどちらのオペレーティングシステムにもインストールできます。このセクションの説明では、Windowsバージョンのツールについて説明しますが、Linuxにインストールする場合は、違いは明らかです。異なるオペレーティングシステムでのVivadoツールの操作はほぼ同じである必要があります。

- まだお持ちでない場合は、https://www.xilinx.com/registration/create-account.htmlでザイリンクスユーザーアカウントを作成してください。

- https://xilinx.comにアクセスして、ユーザーアカウントにログインします。ログインしたら、https://www.xilinx.com/support/download.htmlのツールダウンロードページにアクセスします。

- ザイリンクスユニファイドインストーラー:Windows自己解凍型Webインストーラーをダウンロードします。 。おそらく入手可能な最新バージョンを選択する必要がありますが、この本で使用されているバージョンをフォローしたい場合は、バージョン 2020.1 を選択してください。 。

- インストーラファイルの名前は、Xilinx_1_0602_1208_Win64.exeのようになります。ダウンロードディレクトリでこのファイルを見つけて実行します。 Microsoftで確認されていないアプリのインストールについて警告するダイアログが表示された場合は、[とにかくインストール]をクリックします。 。

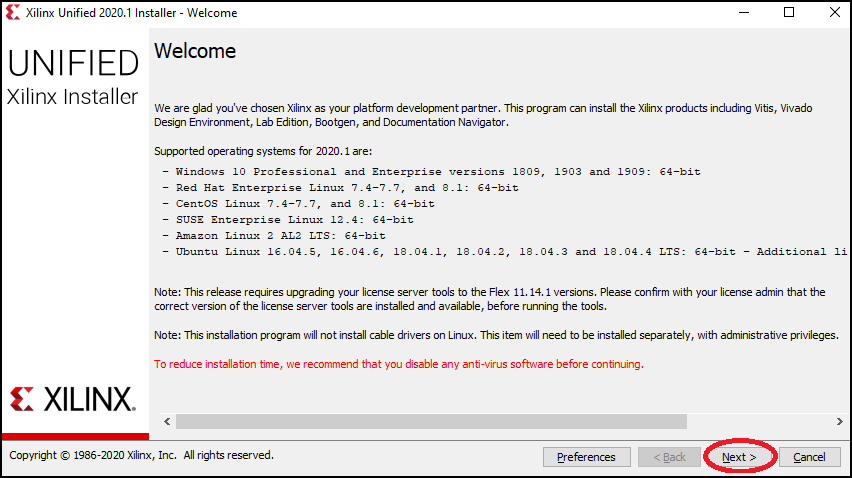

- ようこそのとき 画面が表示されたら、[次へ]をクリックします :

図4.3–インストーラーのようこそダイアログ

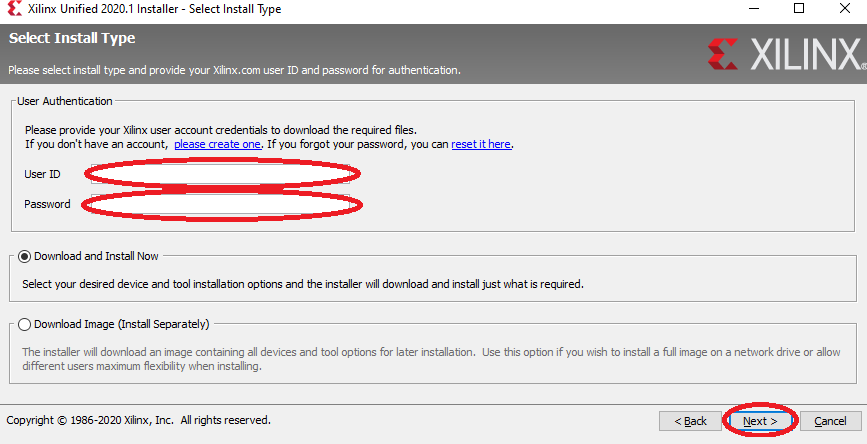

- 次の画面で、xilinx.comのユーザーIDとパスワードを入力し、[次へ]をクリックします。 :

図4.4–インストーラーのログインダイアログ

- 次のダイアログでは、いくつかのライセンス契約に同意するように要求されます。 同意するというチェックボックスをオンにします 、[次へ]をクリックします 。

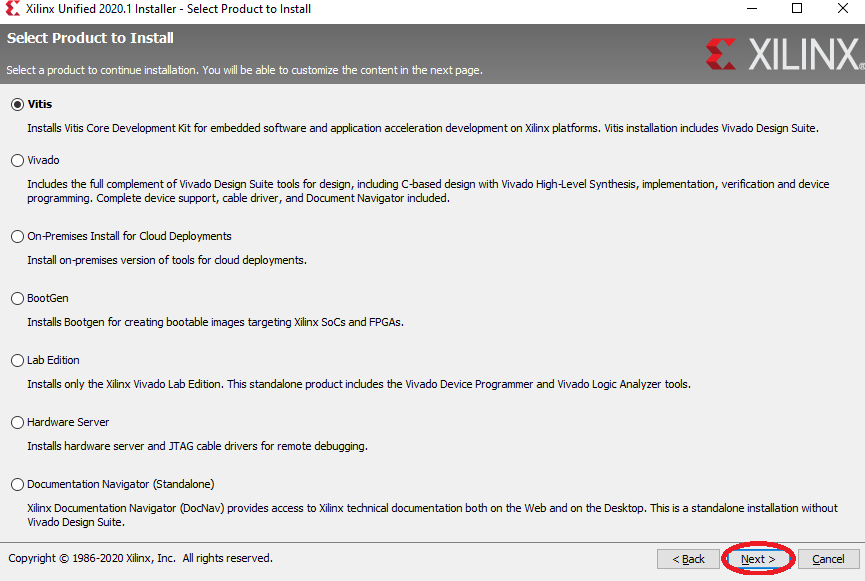

- 次のダイアログで、 Vitis を終了します インストールする製品として選択し、次へをクリックします 。 Vitisには、Vivadoツールスイートとその他のザイリンクス開発ツールのコレクションが含まれています。

図4.5–インストーラー製品の選択ダイアログ

- 次のダイアログでは、インストールするソフトウェアコンポーネントを選択できます。選択範囲をデフォルト値のままにして、次へをクリックします 。

- 次のダイアログでは、宛先ディレクトリを選択し、プログラムのショートカットオプションを指定できます。 C:\ Xilinxの宛先ディレクトリが適切な場所です。このディレクトリが存在しない場合は作成してください。 次へをクリックします 。

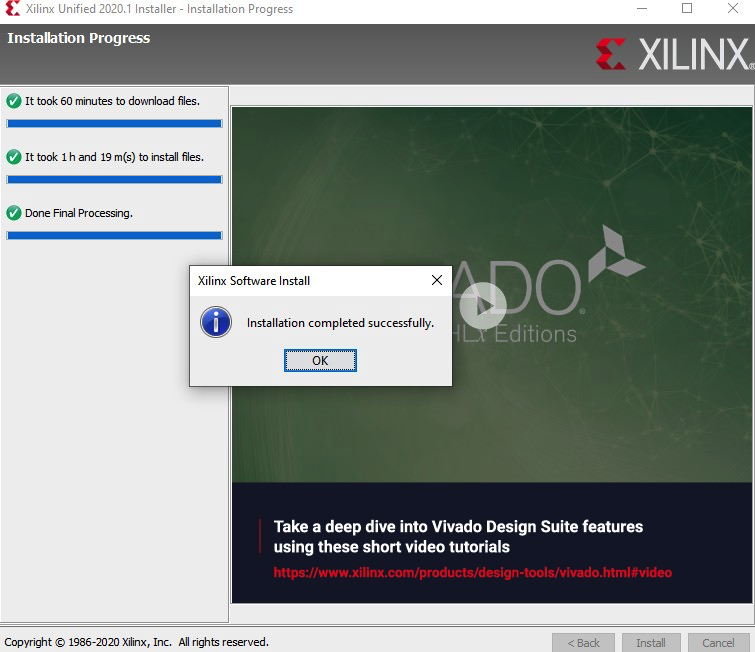

- 次のダイアログには、インストールオプションの概要が表示されます。 インストールをクリックします インストールを続行します。コンピュータの速度とインターネット接続によっては、インストールが完了するまでに数時間かかる場合があります。

図4.6–インストール完了ダイアログ

インストールが完了したら、次に最初のプロジェクトを作成します。

プロジェクトの作成

次の手順に従って、ArtyA7ボード用の4ビットバイナリ加算器プロジェクトを作成およびビルドします。

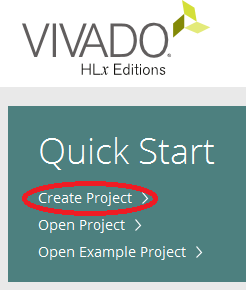

- Vivado 2020.1 というタイトルのデスクトップアイコンを見つけます (または、異なる場合はバージョン番号を探して)ダブルクリックします。

- Vistaでメイン画面が表示されたら、プロジェクトの作成をクリックします。 クイックスタート セクション:

図4.7–Vivadoクイックスタートダイアログ

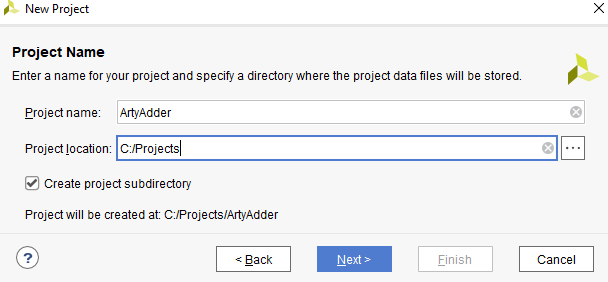

- これにより、新しいVivadoプロジェクトの作成が開始されます ウィザード。 次へをクリックします プロジェクト名に到達するには ページを開き、プロジェクト名としてArtyAdderと入力します。プロジェクトに適切なディレクトリの場所を選択し、チェックボックスをオンにしてサブディレクトリを作成し、[次へ]をクリックします 。この本の例では、すべてのプロジェクトの場所としてC:\ Projectsディレクトリを使用します。

図4.8– [プロジェクト名]ダイアログ

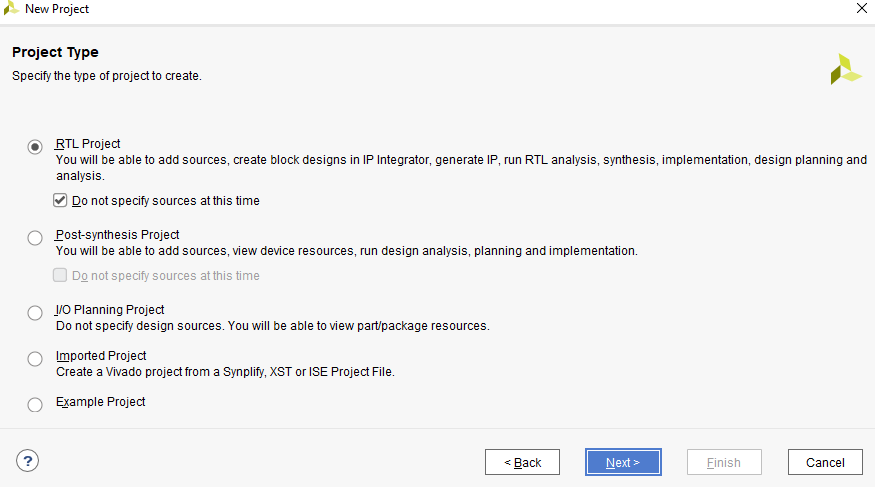

- プロジェクトタイプ ダイアログで、 RTLプロジェクトを選択します 現時点ではソースを指定しないの横にあるチェックボックスをオンにします 。 次へをクリックします :

図4.9– [プロジェクトタイプ]ダイアログ

- デフォルトの部分 ダイアログで、ボードをクリックします タブを押して、検索にArtyと入力します 分野。使用しているボードの種類に応じて(またはまだボードを持っていない場合)、 Arty A7-100 のいずれかを選択します。 または Arty A7-35 次へをクリックします :

図4.10–デフォルトのパーツダイアログ

- 新しいプロジェクトの概要 ダイアログで、完了をクリックします 。

これで、空のプロジェクトが作成されました。次のセクションでは、このプロジェクトの論理回路設計を含むVHDLソースファイルを作成します。

VHDLソースファイルの作成>

次の手順では、VHDLソースファイルの作成、ソースコードの入力、FPGAデザインのコンパイルのプロセスについて説明します。

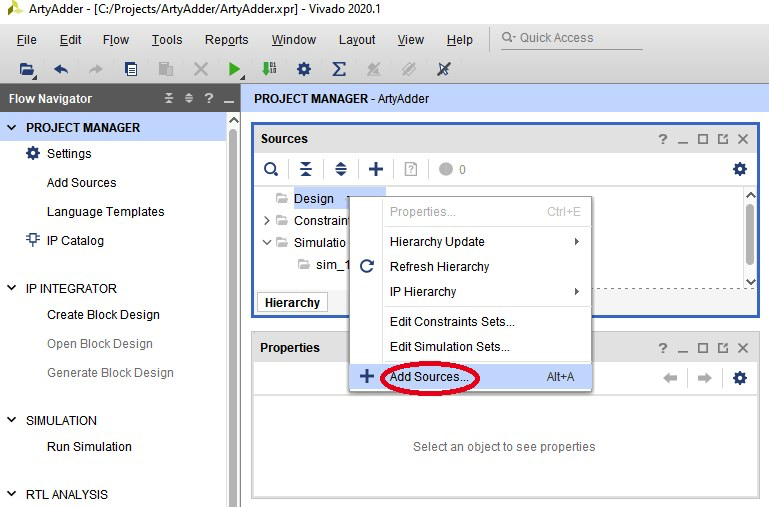

- 出典 サブウィンドウで、デザインソースを右クリックします ソースの追加…を選択します :

図4.11–ソースの追加…メニューの選択

- ソースの追加 ダイアログで、デザインソースの追加または作成を確認します が選択されたら、[次へ]をクリックします 。

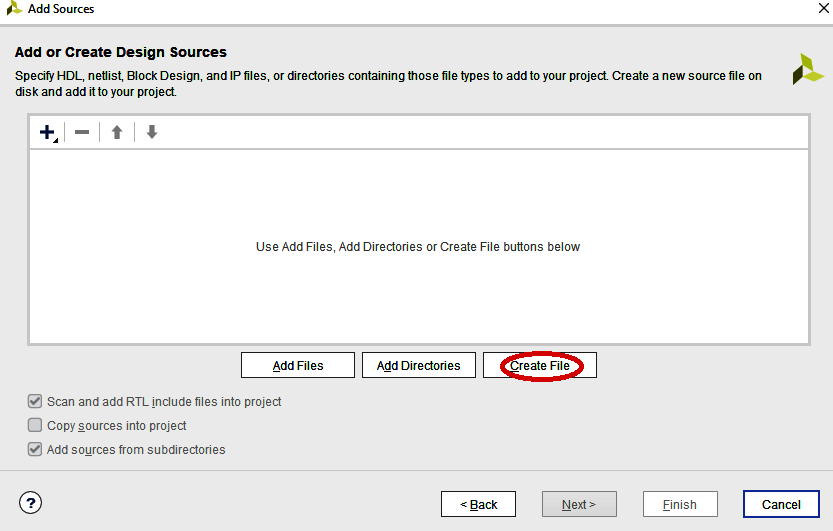

- デザインソースの追加または作成 ダイアログで、ファイルの作成をクリックします :

図4.12– [デザインソースの追加または作成]ダイアログ

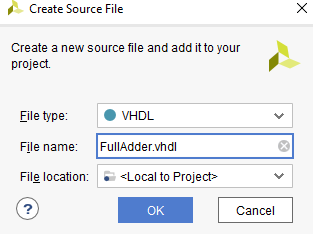

- ファイル名FullAdder.vhdlを入力し、 OK をクリックします :

図4.13– [ソースファイルの作成]ダイアログ

- 前の2つの手順を繰り返して、Adder4.vhdlという名前の別のファイルを作成し、[完了]をクリックします。 デザインソースの追加または作成 ダイアログ。

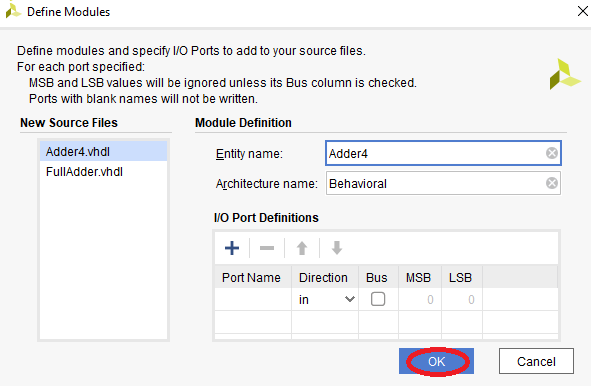

- モジュールの定義 次にダイアログが表示されます。ここには何も入力しません。 OK をクリックします これを閉じるにはこれらの値を使用するかどうかを確認するメッセージが表示されます。 はいをクリックします :

図4.14– [モジュールの定義]ダイアログ

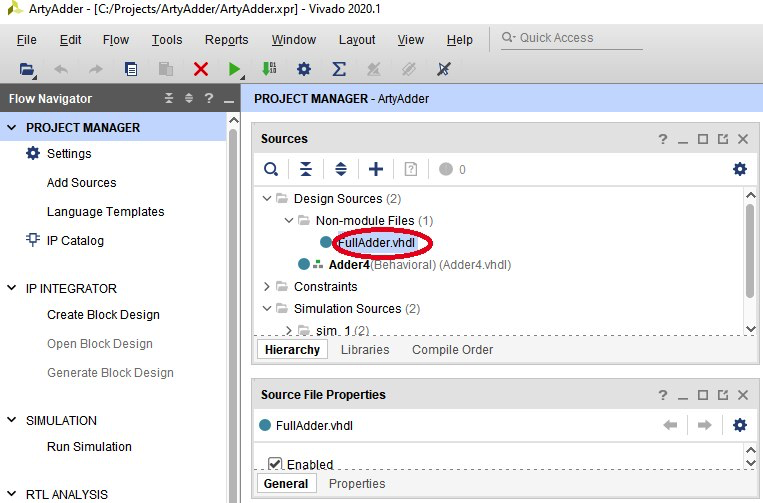

- 非モジュールファイルを展開します デザインソースの下 、次にFullAdder.vhdlをダブルクリックします。エディタウィンドウが開き、空のFullAdder.vhdlファイルが表示されます。

図4.15–新しく作成されたソースファイル

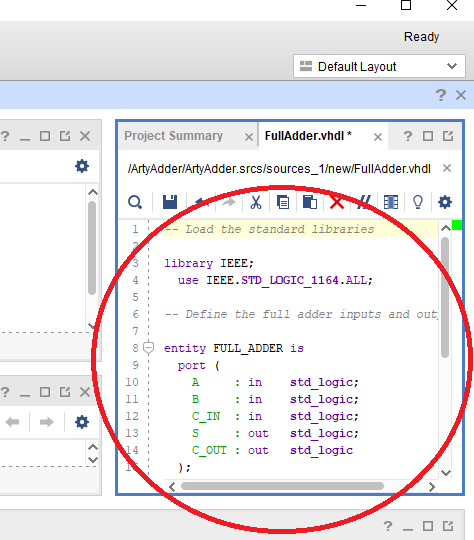

- 次のVHDLコードをFullAdder.vhdlエディタウィンドウに入力します。

-標準ライブラリライブラリIEEEをロードします。 IEEE.STD_LOGIC_1164.ALLを使用します;-全加算器の入力と出力を定義します。 --FULL_ADDERの全加算器アーキテクチャの動作を定義しますisbeginS <=(A XOR B)XOR C_IN; C_OUT <=(A AND B)OR((A XOR B)AND C_IN);アーキテクチャの動作を終了します;

これは、ハードウェア設計言語で調べたのと同じシングルビット全加算器コードです。 第1章、高性能組み込みシステムの設計のセクション 。 図4.16 は、Vivadoエディタウィンドウにコードを表示します:

図4.16–FullAdder.vhdlソースコード

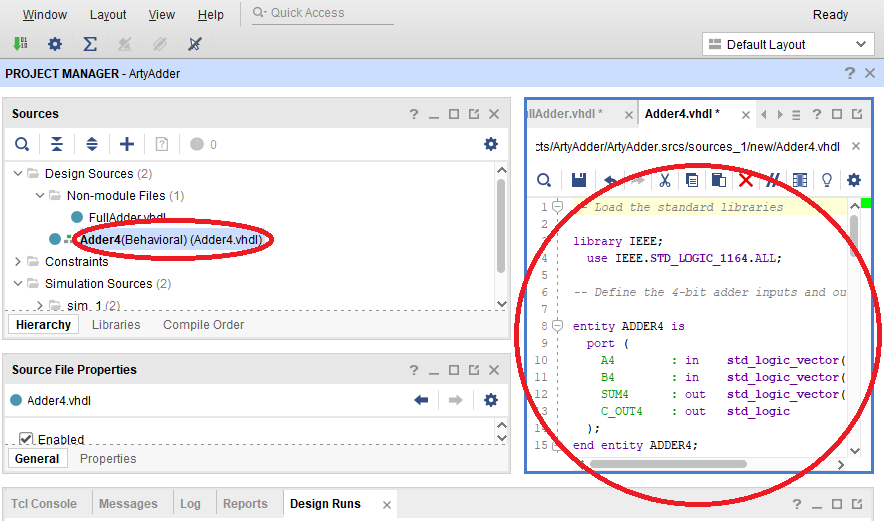

- 同様に、 Adder4(Behavioral)(Adder4.vhdl)をダブルクリックします。 デザインソースの下 。 Adder4.vhdl の自動的に入力されたコンテンツを削除します エディタウィンドウで、次のコードを Adder4.vhdl に入力します 編集者:

-標準ライブラリライブラリIEEEをロードします。 IEEE.STD_LOGIC_1164.ALLを使用; -4ビット加算器の入力と出力を定義); C_OUT4:out std_logic); end entity ADDER4; -4ビット加算アーキテクチャの動作を定義しますADDER4の動作は-完全加算器コンポーネントの以前の定義を参照しますFULL_ADDERはポート(A:std_logic; B:in std_logic; C_IN:in std_logic; S:out std_logic; C_OUT:out std_logic);エンドコンポーネント; -4ビット加算器信号c0、c1、c2で内部的に使用される信号を定義します:std_logic; begin-最初の加算器へのキャリー入力は0に設定されますFULL_ADDER0:FULL_ADDERポートマップ(A => A4(0)、 B => B4(0)、C_IN => '0'、S => SUM4(0)、C_OUT => c0); FULL_ADDER1:FULL_ADDERポートマップ(A => A4(1)、B => B4(1)、C_IN => c0、S => SUM4(1)、C_OUT => c1); FULL_ADDER2:FULL_ADDERポートマップ(A => A4(2)、B => B4(2)、C_IN => c1、S => SUM4(2)、C_OUT => c2); FULL_ADDER3:FULL_ADDERポートマップ(A => A4(3)、B => B4(3)、C_IN => c2、S => SUM4(3)、C_OUT => C_OUT4);アーキテクチャの動作を終了します;

このコードは、シングルビット全加算器の4つのコピーをインスタンス化します。最下位加算器へのキャリーはゼロに設定され、各加算器からのキャリーは次に重要な加算器に波及します。 2つの4ビット数値を加算した結果は、4ビットの結果と1ビットのキャリーです。

図4.17–Adder4.vhdlソースコード

次の記事では、Artyボードの設計をテストし、設計を実装する方法を示します。

PacktPublishingの許可を得て転載。 Copyright©2021Packt Publishing

>

ジム・レディン Ledin Engineering、Inc。のCEOです。Jimは、組み込みソフトウェアおよびハードウェアの設計、開発、およびテストの専門家です。彼はまた、組み込みシステムのサイバーセキュリティ評価と侵入テストでも活躍しています。彼は理学士号を持っていますアイオワ州立大学で航空宇宙工学の学位を取得し、M.S。ジョージア工科大学で電気およびコンピューター工学の学位を取得。ジムは、カリフォルニアで登録された専門の電気技師、Certified Information System Security Professional(CISSP)、Certified Ethical Hacker(CEH)、およびCertified Penetration Tester(CPT)です。

ジム・レディン Ledin Engineering、Inc。のCEOです。Jimは、組み込みソフトウェアおよびハードウェアの設計、開発、およびテストの専門家です。彼はまた、組み込みシステムのサイバーセキュリティ評価と侵入テストでも活躍しています。彼は理学士号を持っていますアイオワ州立大学で航空宇宙工学の学位を取得し、M.S。ジョージア工科大学で電気およびコンピューター工学の学位を取得。ジムは、カリフォルニアで登録された専門の電気技師、Certified Information System Security Professional(CISSP)、Certified Ethical Hacker(CEH)、およびCertified Penetration Tester(CPT)です。 >

関連コンテンツ:

- FPGAを使用した組み込み設計:ハードウェアリソース

- FPGAを使用した組み込み設計:実装言語

- FPGAを使用した組み込み設計:開発プロセス

- オープンソースツールはFPGAプログラミングを簡素化するのに役立ちます

- FPGAまたはASICでの浮動小数点アルゴリズムの実装

- ディープラーニングにFPGAを活用する

- ソフトウェアツールは、AIアプリケーション用にGPUコードをFPGAに移行します

- FPGAはスバルEyesightビジョンベースADASのASICに取って代わります

Embeddedの詳細については、Embeddedの週刊メールニュースレターを購読してください。

埋め込み