6MOSトランジスタリーク電流の原因

リーク電流は、特に低いしきい値電圧で、電力損失の原因となる可能性があります。 MOSトランジスタに見られる6種類のリーク電流について学びます。

MOSトランジスタについて説明する場合、短チャネルデバイスには基本的に6種類のリーク電流成分があります。

- 逆バイアス-pn接合リーク電流

- サブスレッショルドリーク電流

- ドレインによるバリア低下

- V th ロールオフ

- 動作温度の影響

- ゲート酸化物リーク電流への、およびゲート酸化物リーク電流を介したトンネリング

- 基板からゲート酸化物へのホットキャリア注入によるリーク電流

- ゲート誘導ドレイン低下(GIDL)によるリーク電流

続行する前に、次の情報に備えるためのMOSトランジスタの基本概念に精通していることを確認してください。

1。逆バイアスpn接合リーク電流

MOSトランジスタのドレイン/ソースおよび基板の接合部は、トランジスタの動作中に逆バイアスされます。これにより、デバイスに逆バイアスされたリーク電流が発生します。このリーク電流は、逆バイアス領域での少数キャリアのドリフト/拡散と、アバランシェ効果による電子正孔対の生成が原因である可能性があります。 pn接合の逆バイアスリーク電流は、ドーピング濃度と接合面積に依存します。

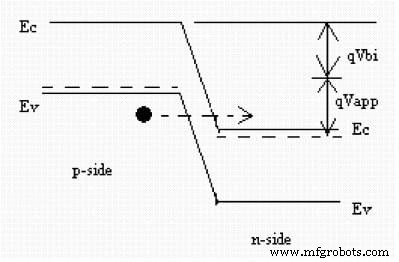

ドレイン/ソース領域と基板領域の高濃度にドープされたpn接合の場合、バンド間トンネリング(BTBT)効果が逆バイアスリーク電流を支配します。バンド間トンネリングでは、電子はp領域の価電子帯からn領域の伝導帯に直接トンネリングします。 BTBTは、10 6 を超える電界で表示されます。 V / cm。

図1。 MOSトランジスタの逆バイアスpn接合におけるバンド間トンネリング。すべての画像は、K.Royらの「ディープサブマイクロメートルCMOS回路におけるリーク電流メカニズムとリーク低減技術」の好意で使用されました。 Proc。 IEEE、Vol。 91、No。2、2003年2月。

この記事の文脈では、電子のエネルギーがポテンシャル障壁よりもはるかに小さい場合でもトンネル現象が発生すると定義していることに注意してください。

2。サブスレッショルドリーク電流

ゲート電圧がしきい値電圧(V th )よりも低い場合 )がゼロより大きい場合、トランジスタはサブスレッショルドまたは弱い反転領域でバイアスされていると言われます。弱い反転では、少数キャリアの濃度は小さいですが、ゼロではありません。このような場合、| V DS の一般的な値 |> 0.1Vで、電圧降下全体がドレイン-基板のpn接合で発生します。

Si-SiO 2 に平行なドレインとソース間の電界成分 インターフェースは小さいです。この無視できる電界のため、ドリフト電流は無視でき、サブスレッショルド電流は主に拡散電流で構成されます。

ドレイン誘導障壁低下(DIBL)

サブスレッショルドリーク電流は、主にドレイン誘導障壁低下またはDIBLによるものです。短チャネルデバイスでは、ドレインとソースの空乏領域が相互作用し、ソースでのポテンシャル障壁を低減します。その後、ソースは電荷キャリアをチャネルの表面に注入して、サブスレッショルドリーク電流を発生させることができます。

DIBLは、高いドレイン電圧と短チャネルデバイスで顕著です。

V th ロールオフ

MOSデバイスのしきい値電圧は、チャネル長の減少により減少します。この現象はV th と呼ばれます ロールオフ(またはしきい値電圧ロールオフ)。短チャネルデバイスでは、ドレインおよびソースの空乏領域がチャネル長にさらに入り、チャネルの一部を空乏化します。

このため、チャネルを反転するために必要なゲート電圧は低くなり、しきい値電圧が低下します。この現象は、ドレイン電圧が高い場合に顕著になります。サブスレッショルド電流はスレッショルド電圧に反比例するため、スレッショルド電圧を下げるとサブスレッショルドリーク電流が増加します。

動作温度の影響

温度も漏れ電流に影響します。しきい値電圧は、温度の上昇とともに低下します。つまり、サブスレッショルド電流は温度の上昇とともに増加します。

3。ゲート酸化物漏れ電流へのトンネルおよびゲート酸化物漏れ電流

短チャネルデバイスでは、ゲート酸化物が薄いと、SiO 2 全体に高電界が発生します。 層。電界が高く、酸化物の厚さが薄いと、電子が基板からゲートにトンネルし、ゲートからゲート酸化物を介して基板にトンネルし、ゲート酸化物のトンネル電流が発生します。

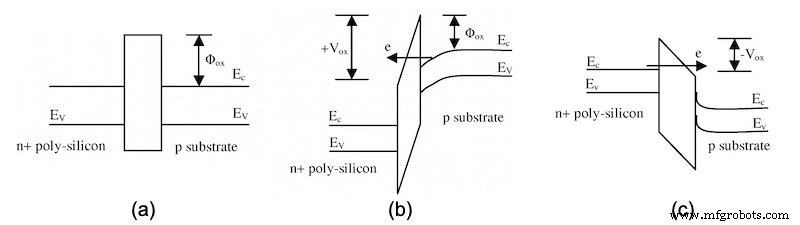

図のようなエネルギーバンド図を検討してください。

図2。 (a)を使用したMOSトランジスタのエネルギーバンド図 フラットバンド、(b) 正のゲート電圧、および(c) 負のゲート電圧

最初の図、図2(a)は、フラットバンドMOSトランジスタの図です。つまり、電荷が存在していません。

ゲート端子が正にバイアスされると、エネルギーバンド図は2番目の図(図2(b))に示すように変化します。強く反転した表面の電子は、SiO 2 にトンネルを掘ります。 ゲート電流を発生させる層。

一方、負のゲート電圧が印加されると、n +ポリシリコンゲートからの電子がSiO 2 にトンネルします。 図2(c)に示すように、ゲート電流を発生させる層。

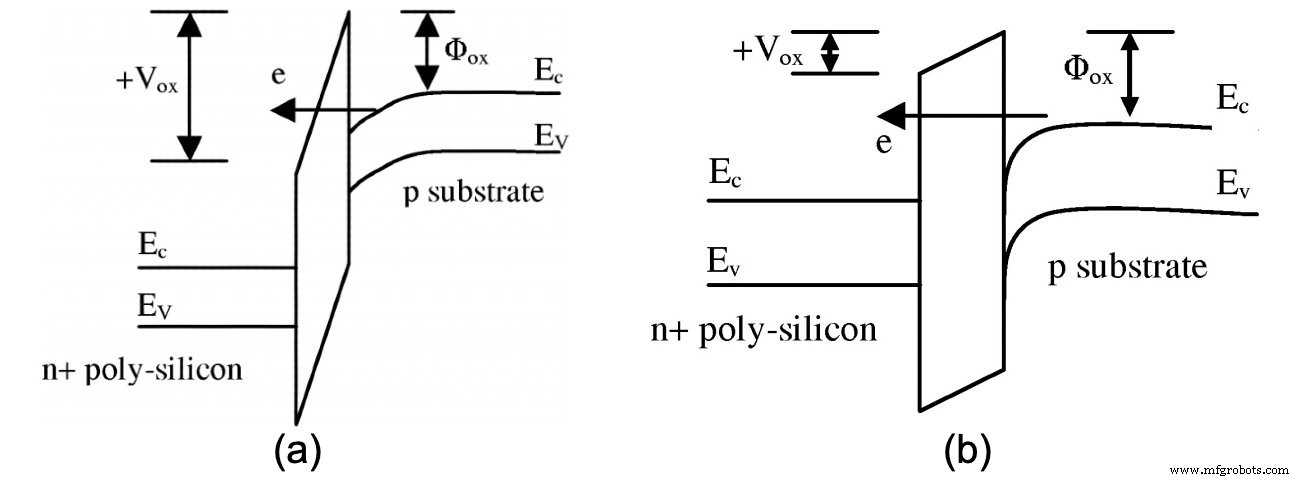

ファウラー-ノルドハイムトンネリングと直接トンネリング

ゲートと基板の間には、主に2種類のトンネリングメカニズムがあります。それらは:

- Fowler-Nordheimトンネリング。電子は三角形のポテンシャル障壁を通り抜けます

- 電子が台形のポテンシャル障壁をトンネリングする直接トンネリング

図3。 (a)を示すエネルギーバンド図 Fowler-Nordheimは、酸化物の三角形のポテンシャル障壁と(b)をトンネリングします。 酸化物の台形ポテンシャル障壁を介した直接トンネリング

上記の図3(a)と3(b)に、両方のトンネリングメカニズムのエネルギーバンド図を示します。

4。基板からゲート酸化物へのホットキャリア注入によるリーク電流

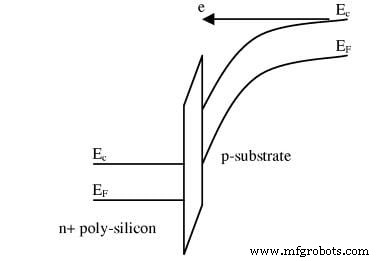

短チャネルデバイスでは、基板と酸化物の界面近くの高電界が電子または正孔にエネルギーを与え、それらが基板と酸化物の界面を通過して酸化物層に入ります。この現象は、ホットキャリア注入として知られています。

図4。 高電界により十分なエネルギーを獲得し、酸化物障壁ポテンシャルを越える電子を示すエネルギーバンド図(ホットキャリア注入効果)

この現象は、正孔よりも電子に影響を与える可能性が高くなります。これは、電子の有効質量が小さく、正孔に比べてバリアの高さが低いためです。

5。ゲート誘導ドレイン低下(GIDL)による漏れ電流

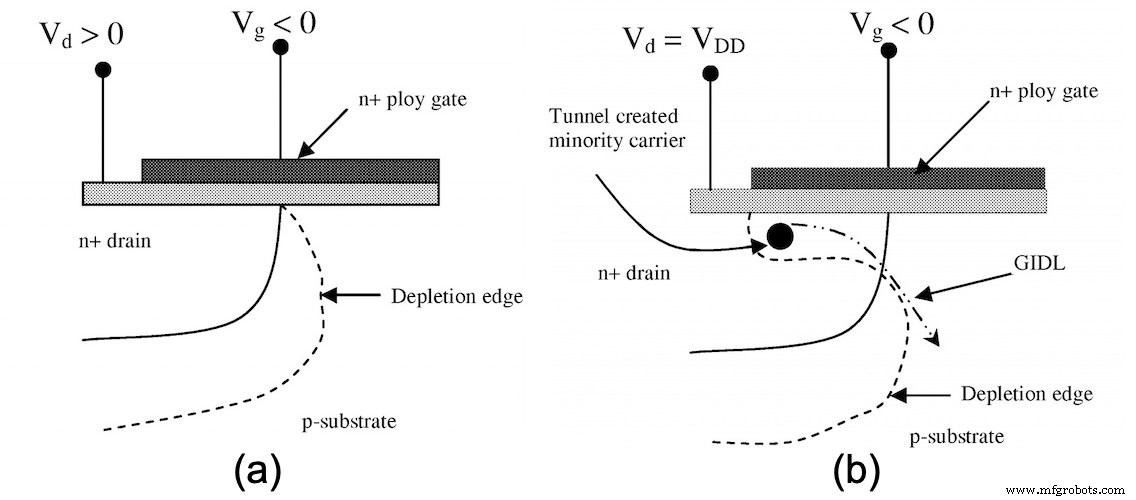

p型基板を備えたNMOSトランジスタを考えてみましょう。ゲート端子に負の電圧がある場合、正の電荷は酸化物と基板の界面にちょうど蓄積します。基板に蓄積された正孔により、表面は基板よりも高濃度にドープされたp領域として動作します。

これにより、ドレイン-基板界面に沿った表面の空乏領域が薄くなります(バルクの空乏領域の厚さと比較した場合)。

図5。 (a) 表面に沿ったドレイン-基板界面での薄い空乏領域の形成と(b) アバランシェ効果とBTBTによって生成されたキャリアによるGIDL電流の流れ

空乏領域が薄く、電界が高いため、アバランシェ効果とバンド間トンネリング(この記事の最初のセクションで説明)が発生します。したがって、ゲートの下のドレイン領域に少数キャリアが生成され、負のゲート電圧によって基板に押し込まれます。これにより、リーク電流が増加します。

6。パンチスルー効果による漏れ電流

短チャネルデバイスでは、ドレイン端子とソース端子が近接しているため、両方の端子の空乏領域が一緒になり、最終的にはマージされます。このような状態で、「パンチスルー」が発生したと言われています。

パンチスルー効果は、ソースからのキャリアの大部分のポテンシャル障壁を下げます。これにより、基板に入るキャリアの数が増えます。これらのキャリアの一部はドレインによって収集され、残りはリーク電流の原因になります。

これで、MOSトランジスタに関連する6種類のリーク電流に精通しているはずです。これらの概念についてさらに質問がある場合は、以下にコメントを残してください。

埋め込み