新しいMLベースのツールは、自動化されたチップ設計フローの最適化を提供します

顧客がより多くの機能とより小さなデバイス、そしてより低い電力消費を要求するにつれて、チップ設計がますます複雑になっているという事実については議論の余地がありません。この需要を満たすために、エンジニアは過負荷になり、需要とタイムリーな製品開発に追いつくためのサポートが必要になっています。

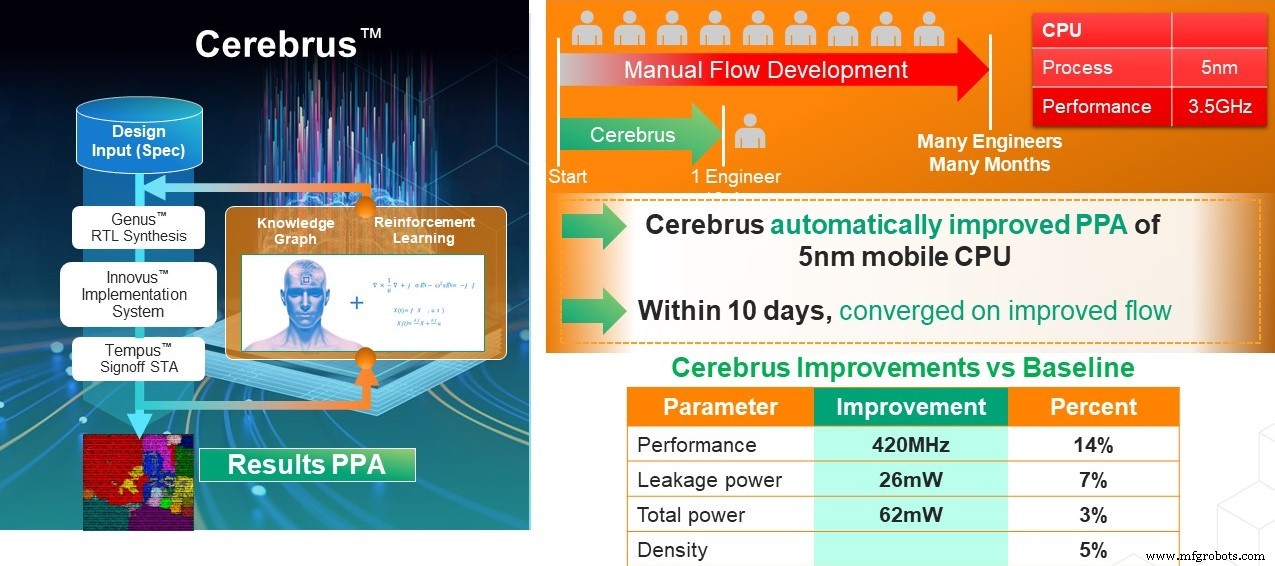

これに対処するために、Cadence Design Systemsは、機械学習(ML)を使用してCadence RTLからサインオフへの実装フローを推進する新しいツールを導入し、最大10倍の生産性と20%のPPA(電力、パフォーマンス、および面積)を実現しました。 )実装の改善。その新しいCerebrusIntelligent Chip Explorerは、従来の人間主導の設計探索よりも効率的なオンサイトおよびクラウドコンピューティングリソース管理機能を提供します。また、多くのノードと、消費者、ハイパースケールコンピューティング、5G通信、自動車、モバイル設計などの複数のエンドアプリケーションにわたるPPAと生産性を向上させます。

Embedded.comのブリーフィングで、ケイデンスの製品管理グループディレクターであるRod Metcalfeは、次のように述べています。「これは、MLを使用した最初のフルフローデジタル最適化ツールです。これは重要です。設計の複雑さが増すにつれて、チップ設計にはより多くの機能とインテリジェンスが必要になりますが、これらのタスクを実行できるエンジニアの数には制約があります。設計者が手動のフロー開発を行っており、設計目標を達成するためにループを反復処理しているのを今でも見ています。これには膨大なエンジニアリング作業が必要であり、スケーラブルではありません。そこでCerebrusが登場し、大規模なコンピューティングを使用して設計自動化の生産性を向上させます。」

Metcalfeは、Cerebrusが5nmモバイルCPUのPPAを自動的に改善するために、改善された設計フローに10日以内に収束するために1人のエンジニアしか必要としなかった例を強調しました(下の図を参照)。

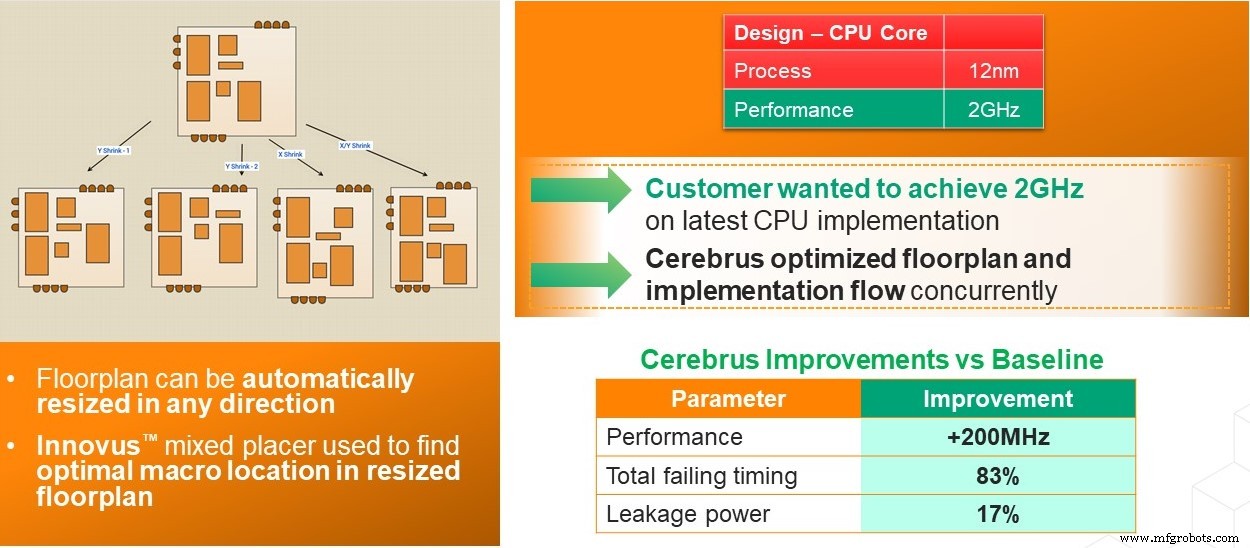

より高いレベルの別の例は、下の図のように、自動化されたフロアプランの最適化です。

CerebrusのようなMLベースのツールを使用することの影響は、設計チームが過去の設計知識を再利用する自動化された方法を持っていることです。以前は、新しいプロジェクトごとに手動で再学習することに余分な時間を費やしていました。したがって、ケイデンス氏は、CerebrusはML主導のデジタルチップ設計でEDA業界に革命をもたらし、エンジニアリングチームは手動プロセスをオフロードできるため、組織に大きな影響を与える機会が増えると述べました。業界が高度なノードに移行し続け、設計のサイズと複雑さが増すにつれて、Cerebrusは設計者がPPAの目標をより効率的に達成できるように支援します。

このツールに対する初期の顧客の支持は、ルネサスとサムスンファウンドリーからのものでした。

ルネサスの共有研究開発EDA部門のデジタル設計技術部門のディレクターである柴谷聡氏は、次のように述べています。「新しいプロセスノードを使用する新製品のパフォーマンスを効率的に最大化するには、エンジニアリングチームが使用するデジタル実装フローを継続的に更新する必要があります。自動化された設計フローの最適化は、はるかに高いスループットで製品開発を実現するために重要です。革新的なML機能とCadenceRTL-to-signoffツールを備えたCerebrusは、自動化されたフロー最適化とフロアプラン探索を提供し、設計パフォーマンスを10%以上向上させました。」

一方、SamsungFoundryの設計技術担当副社長であるSangyunKimは、次のように述べています。「最新のプロセスノードを展開し続けるため、設計技術の共同最適化(DTCO)プログラムの効率は非常に重要です。 。ケイデンスとの長期的なパートナーシップの一環として、サムスンファウンドリーは複数のアプリケーションでCerebrusとケイデンスのデジタル実装フローを使用してきました。数か月の手作業と比較して、わずか数日で最も重要なブロックの一部で8%を超える電力削減が見られました。さらに、自動フロアプラン配電ネットワークのサイジングにCerebrusを使用しているため、最終的な設計タイミングが50%以上向上しています。

Cerebrusの主な機能と利点は次のとおりです。

- 補強ML : 人間のエンジニアが自然に試したり探索したりできないフローソリューションをすばやく見つけて、PPAと生産性を向上させます。

- MLモデルの再利用 :設計学習を将来の設計に自動的に適用できるようにし、より良い結果が得られるまでの時間を短縮します。

- 生産性の向上 :1人のエンジニアが同時に多数のブロックに対して完全なRTLからGDSへのフローを自動的に最適化できるため、完全な設計チームの生産性が向上します。

- 大規模分散コンピューティング :スケーラブルなオンプレミスまたはクラウドベースの設計探索を提供して、フローの最適化を高速化します。

- 使いやすいインターフェース: 強力なユーザーコックピットにより、インタラクティブな結果分析と実行管理により、設計指標に関する貴重な洞察を得ることができます。

Cerebrusは、より広範なCadenceデジタルフルフローの一部であり、Genus合成ソリューション、Innovus実装システム、Tempusタイミングサインオフソリューション、Joules RTL電源ソリューション、Voltus IC電源整合性ソリューション、およびPegasus検証システムとシームレスに連携して、お客様に高速パスを提供します。閉鎖とより良い予測可能性を設計するため。

埋め込み

- 新しいレベルのエッジAIへのシフトアップ

- Pulsicは、回路図エディタでリアルタイムのアナログチップレイアウトプレビューを提供します

- プロジェクトは、IoTセキュリティの信頼できる設計と検証のフローを調査します

- SIMULIAタイヤのエンジニアリングと設計

- ペンシルベニア州は、フィラデルフィアの学生が製造業の機会を発見するのに役立つ新しい資金を提供しています

- 調整されたプリフォームの設計エンジニアリング

- オープンフロントデザインなどのバー/チャッカー

- 新しいトランジスタ設計は、ハッカーから保護するために主要なコンピュータチップハードウェアを偽装します

- Sandvikが新しいターニングコンセプトを発表

- 新ライン統合の展望

- 新しいツールを追加する方法