非同期リセットの同期と配布–課題と解決策

非同期リセットと同期ロジッククロック間の調整が不足していると、電源投入時に断続的に障害が発生します。この一連の記事では、非同期リセットの要件と課題について説明し、ASICとFPGAの設計の高度なソリューションを探ります。

非同期リセットは、電源投入後に同期回路を既知の状態にするために、VLSI設計で従来から採用されています。非同期リセットリリース操作は、リセットとクロック間の競合の可能性による同期の失敗を排除するために、同期ロジッククロック信号と調整する必要があります。このような調整が不足していると、電源投入時に断続的に障害が発生します。大規模なマルチクロックドメイン設計を検討すると、問題が悪化します。同期の問題に加えて、数百万のフリップフロップへの非同期リセットの配布は困難であり、CTS(Clock Tree Synthesis)と同様の技術が必要であり、同様のエリアとルーティングリソースが必要です。

非同期リセットの要件と課題を、同期と配布の問題に焦点を当てて確認します。リセット同期(リセットツリーソース同期)および配布(リセットツリー合成)の従来のソリューションの欠点について説明します。より高速で単純なタイミングコンバージェンスとより信頼性の高いリセット同期および分散のための高度なソリューションが提示されます。 ASIC設計とFPGA設計のさまざまなアプローチについて詳しく説明します。

パート1(この記事)では、非同期リセットを取り巻く問題について説明し、それらの問題を解決するためのアプローチの概要を説明します。パート2では、ASICおよびFPGAでの正しい非同期リセットの追加ソリューションについて説明します。いくつかの有用な特殊なケースについては、パート3で説明します。

1。非同期リセットの課題

ロジックを既知の状態にするために、通常、リセット機能がデジタルVLSI設計に含まれています。リセットは主に制御ロジックに必要であり、データパスロジックから削除してロジック領域を減らすことができます。リセットは、クロック信号に対して同期または非同期のいずれかです。

同期リセットにはアクティブクロックが必要であり、クロックサイクルに関連する特定の遅延が発生し、データパスのタイミングに影響を与える可能性があります。一方、同期リセットは決定論的であり、準安定性は発生しません。

非同期リセットは、フリップフロップを既知の状態にするためにアクティブクロックを必要とせず、同期リセットよりもレイテンシが低く、データパスのタイミングに影響を与えない特別なフリップフロップ入力ピンを利用できます。ただし、非同期リセットにはいくつかの欠点があります。

-

フリップフロップに準安定状態を引き起こし、非決定的な動作を引き起こす可能性があります。

-

DFTを有効にするには、非同期リセットに直接アクセスできるようにする必要があります。

-

非同期リセットは、耐放射線性アプリケーションで信頼性の問題を引き起こす可能性があり、シングルイベントトランジェント(SET)現象の影響を受けやすくなります[1]。

どのタイプのリセットが優れているかについての議論はさておき[2]、この記事では、非同期リセットに関連する問題と解決策に焦点を当てます。このホワイトペーパーで紹介する手法のいくつかは、非同期リセットと同期リセットの両方に適用できます。

非同期リセットは、デジタルデザインで広く採用されています。非同期リセットの一般的なドライバーは、電源の状態(RC回路、ウォッチドッグデバイス)、手動リセットボタン、およびマイクロプロセッサーなどの外部マスターに応じて、外部ポートです。

多くの場合、非同期リセットは同期リセットに置き換えることができますが、非同期リセット機能が必須である場合もあります。 1つの例は、電源投入時にアクティブクロックを取得しない(クロックが不安定であるか、電力削減のためにゲートされる)同期設計ですが、外部インターフェイスに特定の既知の状態が必要です。もう1つの例は、アクティブクロックがない、電源投入プロセス中の電力を最小限に抑えるために必要な低電力設計です。

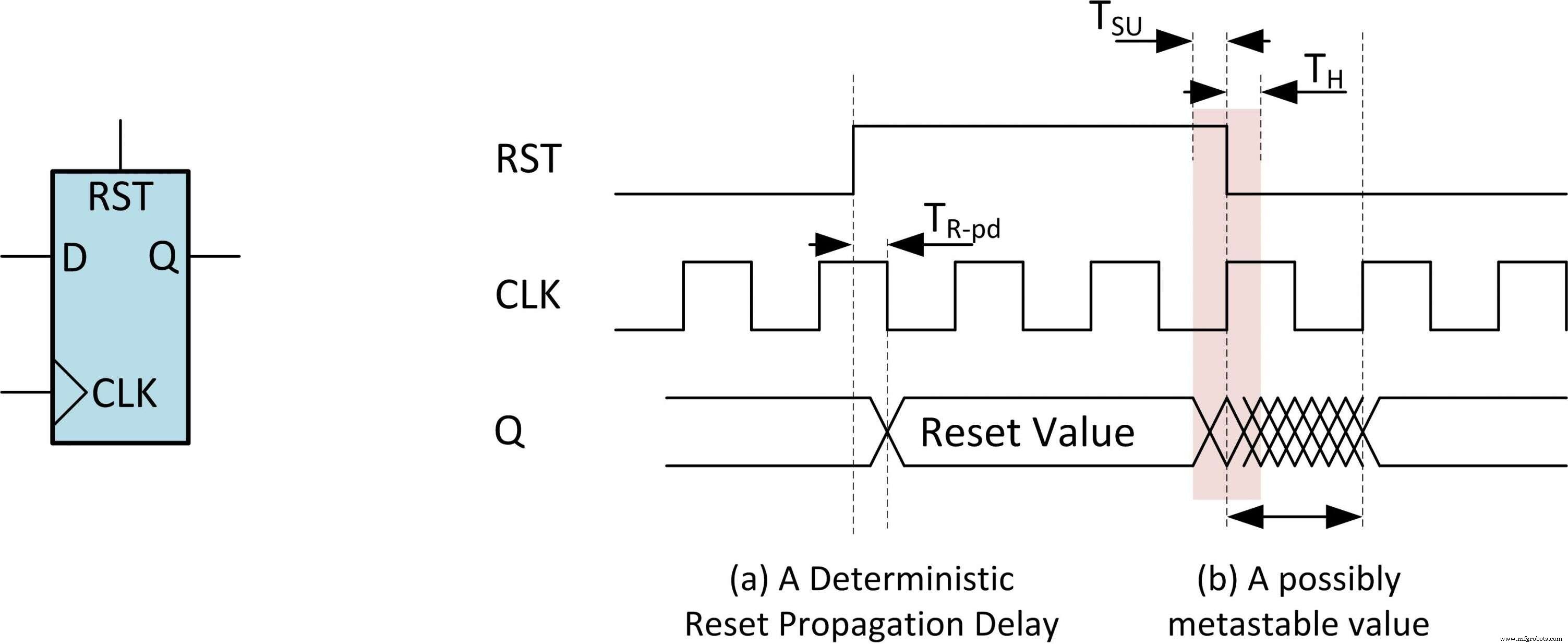

非同期リセットの採用は簡単ではありません。リセットアサーション中は、クロックとリセットの間の相対的なタイミングは無視できますが、リセットリリースはクロックに同期する必要があります。リセットリリースエッジの同期を回避すると、準安定状態につながる可能性があります。図1を参照すると、アクティブな高非同期リセットが示されています。リセットアサーション(a)は、決定論的に制限された時間内にフリップフロップ出力Qに影響を与えます(伝搬遅延、T R-pd )およびクロック信号CLKに関係なく。リセットリリース(b)の間、クロックポートCLKに対してRSTポートのセットアップとホールドのタイミング条件が満たされる必要があります。 RSTポートのセットアップおよびホールド条件(リセットリカバリおよびリムーバルタイミングとも呼ばれます)に違反すると、フリップフロップが準安定になり、不明な状態に切り替わって設計が失敗する可能性があります。この状況は、フリップフロップデータポートDのセットアップおよびホールド条件の違反に似ていることに注意してください。

クリックして大きな画像を表示

図1:アクティブハイ非同期リセットアサーションとリリース。 (a)非同期リセットアサーション(b)タイミング違反のある非同期リセットリリース。 (出典:vSync Circuits)

埋め込み