高PSRRのナノスケール低電力抵抗なし電圧リファレンス

要約

この論文では、高電源除去比(PSRR)を備えたナノワットの抵抗のないサブスレッショルド電圧リファレンスを紹介します。自己バイアスMOS分圧器は、全電圧リファレンスにバイアス電流を提供するために提案されています。これは、しきい値電圧特性を含む正の温度係数(TC)電流です。生成された電流を異なるしきい値電圧のトランジスタに注入することにより、負のTCが大幅に低減されたデルタしきい値電圧が実現され、同時に生成された正のTCアイテムによって温度補償されます。したがって、温度安定電圧基準は、低消費電力と高PSRRを備えた提案されたコンパクト化された方法で達成されます。 65 nm CMOSテクノロジーによる検証結果は、最小供給電圧が0.00182 mm 2 で0.35Vまで低くなる可能性があることを示しています。 アクティブエリア。生成される基準電圧は148mVで、TCは-30〜80°Cの温度範囲で28 ppm /°Cです。ライン感度は1.8mV / V、100HzでのフィルタリングコンデンサなしのPSRRは53dB、消費電力は2.28nWです。

はじめに

電圧リファレンスは、電子システムのコアモジュールの1つであり、医療用電子機器、電力管理、ワイヤレス環境センサー、および通信回路で広く使用されています。電子システムの供給電圧は技術の進歩とともに低下し続けるため、ナノスケール技術による低電力電圧リファレンスの要件は非常に高まっています[1、2]。

従来の電圧リファレンスは、バンドギャップリファレンス(BGR)回路に基づいています。これは、 V の加重和です。 BE および熱電圧[3、4]。ただし、 V の非線形温度動作のため BE 、BGRの精度を向上させるために曲率補償アプローチを使用することが不可欠です[5、6]。 BGRのもう1つの欠点は、消費電力です。 V BE プロセス改善により収縮することなく約0.7Vであり、供給電圧を完全に制限します。これらにより、BGRは低電圧およびナノスケールのアプリケーションには不適切になります。

低電力動作を実現するために、MOSのみのサブスレッショルド電圧リファレンスが徐々に採用されています[7、8、9、10]。弱い反転領域のトランジスタは、電流が非常に小さい低電力アプリケーションに固有の利点があるため、相対電圧リファレンスの消費電力を効果的に削減できます。さらに、金属酸化物半導体電界効果トランジスタ(MOSFET)の特性はプロセスの改善と一致しているため、MOSFETに基づく電圧リファレンスは高度な技術により適応性があります。さらに、低電力アプリケーションでは抵抗の使用も避ける必要があります。電圧リファレンスの電流は通常、抵抗値に反比例するため、低消費電力は高抵抗を意味し[10]、大きなチップ領域を占める大きなノイズを引き起こす可能性があります。

電源除去比(PSRR)は、電圧リファレンスのもう1つの重要なパラメータです。 PSRRを改善するための従来のソリューションは、追加の増幅器[11]、長チャネルトランジスタ[12]、カスコード構造、追加のゲインステージ[13]など、チップ面積と消費電力を犠牲にします。

上記の問題を克服するために、この概要では、ナノスケールプロセスなどの高度な技術に適した、PSRRの高いナノワットMOSFETベースの抵抗のないサブスレッショルド電圧リファレンスを提案します。 PSRR拡張用の自己バイアスMOSFET分圧器は、提案された電圧リファレンスで採用されており、しきい値電圧特性を含む正の温度係数(TC)電流を生成できます。この電流は、電圧リファレンス全体のバイアス電流として機能します。さらに、バイアス電流に埋め込まれたしきい値電圧は、紙の異なるしきい値電圧でMOSFETにバイアス電流を注入することによって再現されます。提案された方法では、デルタしきい値電圧( ∆V TH )負のTCが大幅に減少します。さらに、絶対温度に比例する加重(PTAT)項目も取得され、ΔVの加重和が得られます。 TH PTAT電圧も同時に実現します。 2つの異なるしきい値電圧の相互TCキャンセルにより、温度補償のために必要なPTAT電圧を大幅に下げることができます。この方法により、MOSFETのみの抵抗のない電圧リファレンスが、低消費電力のコンパクトな構造によって実現されます。

メソッド

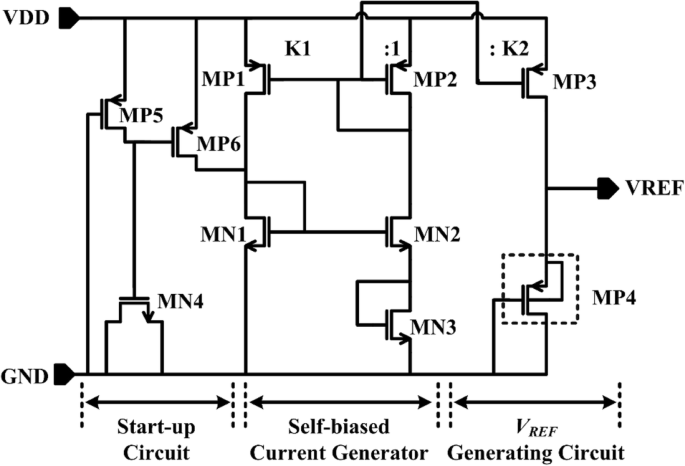

図1に示すように、提案された電圧リファレンスは、起動回路、自己バイアス電流発生器、および V で構成されています。 REF 生成回路。すべてのnチャネルMOSFETは、中程度のしきい値電圧のN型金属酸化物半導体(mvtNMOS)です。 MP4は高しきい値電圧トランジスタのP型金属酸化物半導体(hvtPMOS)であり、他のpチャネルMOSFETは中しきい値電圧PMOS(mvtPMOS)です。図1に示すすべてのトランジスタは、起動回路のトランジスタを除いて、サブスレッショルド領域で動作します。

提案された電圧リファレンスの概略図

起動回路

起動回路はMP5、MP6、MN4で構成されています。電源投入段階の開始時に、MP6のゲート電位は低く、MP6がオンになります。 MP6で発生する電流により、MN1とMN2のゲート電位が上昇し、回路全体が動作を開始します。同時に、MP5は起動コンデンサMN4を充電します。 MN4の充電手順では、トランジスタMP6が徐々にオフになります。これにより、追加の電力損失なしに、起動回路が提案された電圧リファレンスのコアから切り離されます。この方法により、提案された電圧リファレンスは、縮退ポイントを回避しながら、目的の動作ポイントで機能することができます。

自己バイアス電流ジェネレータ

図1の中央部分は、MOSFETのみの分圧器に基づく自己バイアス電流発生器です。この部分では、電圧リファレンス全体に対して正のTCを持つバイアス電流が生成されます。これは、NMOSの中間しきい値電圧に関連しています。提示されたバイアス電流の独自の特性を採用して、提案された電圧リファレンスを便利な方法で実現します。これについては、「方法」セクションで分析します。

サブスレッショルド領域のトランジスタの電圧電流特性に関しては、サブスレッショルドのトランジスタのドレイン電流は V にほとんど依存しなくなります。 DS V で DS > 4 V T 、ここで V T =kT / q は熱電圧、 k はボルツマン定数、 q は電気素量であり、 T は絶対温度です。したがって、電流は次のように表すことができます。

$$ {I} _ {\ mathrm {D}} ={SI} _ {\ mathrm {SQ}} \ exp \ left(\ frac {V _ {\ mathrm {GS}}-{V} _ {\ mathrm { T} \ mathrm {H}}} {mV _ {\ mathrm {T}}} \ right)$$(1)ここで、 S =W / L はアスペクト比、 m サブスレッショルドスロープファクター V TH はしきい値電圧であり、 I SQ 特定の電流を表し、次のように表されます:

$$ {I} _ {\ mathrm {SQ}} =\ mu {C} _ {\ mathrm {OX}} \ left(m-1 \ right){V_T} ^ 2 $$(2)ここでμ はキャリア移動度であり、 C OX は単位面積あたりの酸化物の静電容量です。

したがって、MN1、MN2、およびMN3によって形成されるMOSFETのみの分圧器を流れる電流は、次のように表すことができます。

$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 1} ={S} _ {\ mathrm {MN} 1} {I} _ {\ mathrm {SQN}} \ exp \ left( \ frac {V _ {\ mathrm {GS} \ _ \ mathrm {MN} 1}-{V} _ {\ mathrm {T} \ mathrm {HN}}} {mV _ {\ mathrm {T}}} \ right) $$(3)$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 2} ={S} _ {\ mathrm {MN} 2} {I} _ {\ mathrm {SQN}} \ exp \ left(\ frac {V _ {\ mathrm {GS} \ _ \ mathrm {MN} 2}-{V} _ {\ mathrm {T} \ mathrm {HN}}} {mV _ {\ mathrm {T} }} \ right)$$(4)$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 3} ={S} _ {\ mathrm {MN} 3} {I} _ {\ mathrm {SQN}} \ exp \ left(\ frac {V _ {\ mathrm {GS} \ _ \ mathrm {MN} 3}-{V} _ {\ mathrm {T} \ mathrm {HN}}} {mV_ { \ mathrm {T}}} \ right)$$(5)ここで私 SQN はNMOSと V の比電流です THN はNMOSのしきい値電圧です。

MN2とMN3のアスペクト比は同じであるため、 I D_MN2 =私 D_MN3 、 V GS_MN2 = V GS_MN3 保証されています。これにより、 V GS_MN1 =2 V GS_MN2 。さらに、PMOSトランジスタはカレントミラーを形成し、電流比 K を定義します。 1 =S MP1 / S MP2 および K 2 =S MP3 / S MP2 。 MN1とMN2の間のドレイン電流の関係は、次のように表すことができます。

$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 1} ={K} _1 {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 2} $$(6)式と組み合わせる。 (3)–(6)、 V GS_MN2 および私 D_MN2 によって与えることができます:

$$ {V} _ {\ mathrm {GS} \ _ \ mathrm {MN} 2} ={mV} _ {\ mathrm {T}} \ ln \ left(\ frac {K_1 {S} _ {\ mathrm { MN} 2}} {S _ {\ mathrm {MN} 1}} \ right)$$(7)$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 2} ={S} _ {\ mathrm {MN} 2} {I} _ {\ mathrm {SQN}} \ exp \ left(\ ln \ frac {K_1 {S} _ {\ mathrm {MN} 2}} {S _ {\ mathrm {MN } 1}}-\ frac {V _ {\ mathrm {T} \ mathrm {HN}}} {mV _ {\ mathrm {T}}} \ right)$$(8)分析の便宜のために、式。 (8)は次のように省略できます:

$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 2} ={aT} ^ {2- {n} _1} \ exp \ left(b- \ frac {V _ {\ mathrm {T } \ mathrm {HN}}} {mV _ {\ mathrm {T}}} \ right)$$(9)ここで、 a =S MN2 μ n 0 C OX ( m − 1)( k / q ) 2 および b = ln( K 1 S MN2 / S MN1 )は温度に依存しません、μ n 0 はキャリア移動度の温度に依存しない要因であり、 n 1 はキャリア移動度の絶対温度指数項であり、通常は約1.5です。

式に示すように。 (9)、しきい値電圧 V THN は絶対温度(CTAT)を補完し、熱電圧 V T 絶対温度(PTAT)に比例します。温度が上がると、 V THN /( mV T )が減少するため、バイアス電流の正の電流特性が向上します。

この方法により、正のTCバイアス電流はMOSFETのみの構造によって実現され、NMOSしきい値電圧の特性を備えています。

V REF 生成回路

V REF 生成回路は図1の右側に示されています。これは、MP3とMP4の2つのトランジスタによってのみ形成されています。サブスレッショルド領域の操作により、 I D_MP4 次のように書くことができます:

$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MP} 4} ={S} _ {\ mathrm {MN} 4} {I} _ {\ mathrm {SQP}} \ exp \ left( \ frac {\ mid {V} _ {\ mathrm {GS} \ _ \ mathrm {MP} 4} \ mid- \ mid {V} _ {\ mathrm {T} \ mathrm {HP}} \ mid} {mV_ {\ mathrm {T}}} \ right)$$(10)ここで私 SQP はPMOSと V の比電流です THP V です TH のPMOS。

私以来 D_MP4 =K 2 私 D_MN2 、NMOSしきい値電圧の特性、 V THN 、を出力ノードに転送し、PMOSしきい値電圧 V の特性と重ね合わせることができます。 THP 。式から(8)および(10)、 V REF 次のように書くことができます:

$$ {V} _ {\ mathrm {REF}} =\ mid {V} _ {\ mathrm {T} \ mathrm {HP}} \ mid- {V} _ {\ mathrm {T} \ mathrm {HN} } + {mV} _ {\ mathrm {T}} \ ln \ left(\ frac {K_2 {S} _ {\ mathrm {MN} 2} {I} _ {\ mathrm {SQn}}} {S _ {\ mathrm {MP} 4} {I} _ {\ mathrm {SQP}}} \ right)+ {mV} _ {\ mathrm {T}} \ ln \ left(\ frac {K_1 {S} _ {\ mathrm { MN} 2}} {S _ {\ mathrm {MN} 1}} \ right)$$(11)式の最初の2つの項目に示されているように。 (11)、デルタしきい値電圧が実現されます。 V 以降 TH = V TH0 − βT 、ここで V TH0 は0Kおよびβでのしきい値電圧です。 はしきい値電圧のTCであり、生成されたデルタしきい値電圧は絶対温度(CTAT)電圧を補完するものであり、TCは| βVで大幅に縮小されます。 THP |> βV THN 。さらに、2つの追加のPTAT電圧が同時に実現され、式の最後の2つの項目に示されます。 (11)、デルタしきい値電圧の低下したTCをキャンセルするために採用されています。したがって、| V で安定している複雑な構造なしで、コンパクトな温度安定基準電圧が実現されます。 THP0 | − V THN0 。

以前の分析に基づいて、この論文では、コアに3つの分岐しか必要としない低電力MOSFETのみの電圧リファレンスが実現されています。自己バイアス電流源の独自の特性により、1つのダイオード接続PMOSを採用して、収縮したTC、PTAT電圧発生器、および加重和を同時に備えたCTAT電圧を実現します。さらに、提案された構造はMOSFETのみで構成されており、生成された基準電圧はデルタしきい値電圧に比例します。したがって、提案された電圧リファレンスは、ナノスケール技術を使用した低消費電力アプリケーションに適しています。これは、より高度な技術にさらに拡張できます。

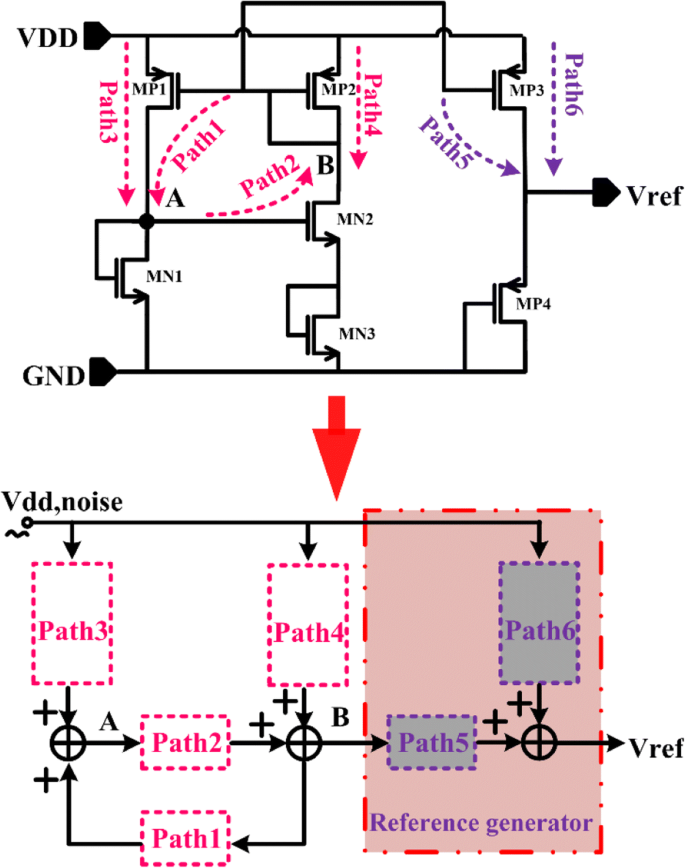

提案された電圧リファレンスのPSRR

PSRRのパフォーマンスを説明するために、電源電圧ノイズから V までのパス REF および対応する同等の機能図を図2に示します。

供給電圧ノイズの経路

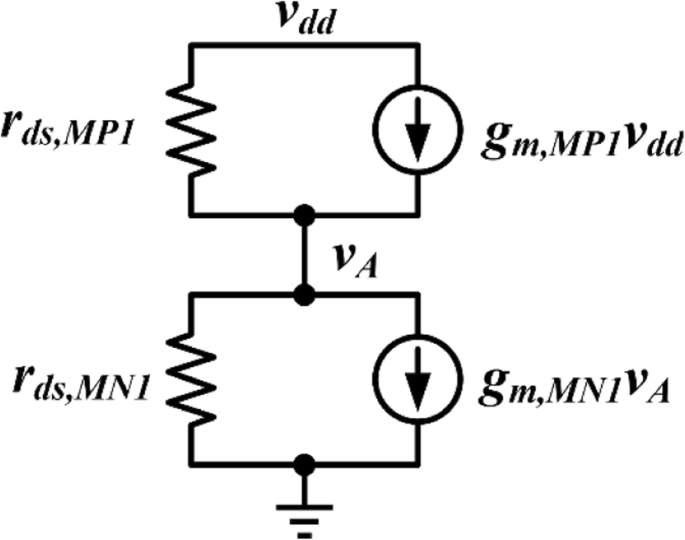

図2に基づいて、パス3の小信号モデルを図3に示します。これにより、次の式が得られます。

$$ \ frac {v _ {\ mathrm {dd}}-{v} _ {\ mathrm {A}}} {r _ {\ mathrm {ds}、\ mathrm {MP} 1}} + {g} _ {\ mathrm {m}、\ mathrm {MP} 1} {v} _ {\ mathrm {dd}} =\ frac {v _ {\ mathrm {A}}} {r _ {\ mathrm {ds}、\ mathrm {MN} 1}} + {g} _ {\ mathrm {m}、\ mathrm {MN} 1} {v} _ {\ mathrm {A}} $$(12)

パス3の小信号モデル

式から(12)、パス3からノードAへの供給ノイズの表現は次のようになります。

$$ {Av} _ {\ mathrm {path} 3} =\ frac {v _ {\ mathrm {A}}} {v _ {\ mathrm {dd}}} =\ frac {r _ {\ mathrm {ds}、\ mathrm {MN} 1} + {g} _ {\ mathrm {m}、\ mathrm {MP} 1} {r} _ {\ mathrm {ds}、\ mathrm {MN} 1} {r} _ {\ mathrm {ds}、\ mathrm {MP} 1}} {r _ {\ mathrm {ds}、\ mathrm {MP} 1} + {r} _ {\ mathrm {ds}、\ mathrm {MN} 1} + {g } _ {\ mathrm {m}、\ mathrm {MN} 1} {r} _ {\ mathrm {ds}、\ mathrm {MN} 1} {r} _ {\ mathrm {ds}、\ mathrm {MP} 1}} $$(13)サブスレッショルド領域で動作するトランジスタの相互コンダクタンスは g です。 m =私 D / mV T 。したがって、 g 間の関係 m、MP1 および g m、MN1 同じ電流で g として与えることができます m、MP1 = g m、MN1 。次に、式。 (13)は次のように簡略化できます:

$$ {Av} _ {\ mathrm {path} 3} \約1 $$(14)ノードBはパス1を介してノードAにも影響を及ぼしますが、その影響はパス3とは逆であり、次のように表すことができます。

$$ {Av} _ {\ mathrm {path} 1} \ approx -1 $$(15)V の場合 A =2 V GS、MN2 、パス2のゲインは次のように与えられます:

$$ {Av} _ {\ mathrm {path} 2} =-\ frac {1} {2} {g} _ {\ mathrm {m}、\ mathrm {MN} 2} \ left(2 {r} _ {\ mathrm {ds}、\ mathrm {MN} 2} \ Big \ Vert \ frac {1} {g _ {\ mathrm {m}、\ mathrm {MP} 2}} \ right)\ approx- \ frac {1 } {2} $$(16)v の効果 dd パス4を介したノードBでは、次のように記述できます。

$$ {Av} _ {\ mathrm {path} 4} =\ frac {2 {r} _ {\ mathrm {ds}、\ mathrm {MN} 2}} {\ left(1 / {g} _ {\ mathrm {m}、\ mathrm {MP} 2} \ right)+2 {r} _ {\ mathrm {ds}、\ mathrm {MN} 2}} =\ frac {2 {g} _ {\ mathrm {m }、\ mathrm {MP} 2} {r} _ {\ mathrm {ds}、\ mathrm {MN} 2}} {1 + 2 {g} _ {\ mathrm {m}、\ mathrm {MP} 2} {r} _ {\ mathrm {ds}、\ mathrm {MN} 2}} $$(17)図2のノードAからノードBまで、次の2つの追加の方程式を取得できます。

$$ {Av} _ {\ mathrm {path} 4} {v} _ {\ mathrm {dd}} + {Av} _ {\ mathrm {path} 2} {V} _ {\ mathrm {A}} ={V} _ {\ mathrm {B}} $$(18)$$ {Av} _ {\ mathrm {path} 3} {v} _ {\ mathrm {dd}} + {Av} _ {\ mathrm {パス} 1} {V} _ {\ mathrm {B}} ={V} _ {\ mathrm {A}} $$(19)式(18)および(19)によると、 V でのノイズ B によって与えることができます:

$$ {V} _ {\ mathrm {B}} =\ frac {2 {g} _ {\ mathrm {m}、\ mathrm {MP} 2} {r} _ {\ mathrm {ds}、\ mathrm { MN} 2} -1} {1 + 2 {g} _ {\ mathrm {m}、\ mathrm {MP} 2} {r} _ {\ mathrm {ds}、\ mathrm {MN} 2}} {v } _ {\ mathrm {dd}} \ approx {v} _ {\ mathrm {dd}} $$(20)提案された自己バイアス電流源の助けを借りて、電流発生器部分の出力ノードBは、供給電圧の小信号変動を追跡できます。これは、電圧リファレンス全体のPSRRの改善に役立ちます。

同様の方法で、パス5とパス6の電源ノイズゲインは次の式で表すことができます。それぞれ(21)と(22):

$$ {Av} _ {\ mathrm {path} 5} ={g} _ {\ mathrm {m}、\ mathrm {MP} 3} \ left({r} _ {\ mathrm {ds}、\ mathrm { MP} 3} \ Big \ Vert \ frac {1} {g _ {\ mathrm {m}、\ mathrm {MP} 4}} \ right)$$(21)$$ {Av} _ {\ mathrm {path} 6} \約1 $$(22)図2に示すリファレンスジェネレータのノイズパス接続関係を考慮して、リファレンス電圧 V での電源ノイズの影響 REF 、パス5とパス6で判別できます:

$$ {v} _ {\ mathrm {REF}} ={Av} _ {\ mathrm {path} 5} {V} _ {\ mathrm {B}} + {Av} _ {\ mathrm {path} 6} {v} _ {\ mathrm {dd}} =\ frac {1} {1+ {g} _ {\ mathrm {m}、\ mathrm {MP} 4} {r} _ {\ mathrm {ds}、\ mathrm {MP} 3}} {v} _ {\ mathrm {dd}} =\ frac {1} {1 + \ frac {\ exp \ left({V} _ {\ mathrm {DS}、\ mathrm {MP } 3} / {V} _ {\ mathrm {T}} \ right)-1} {m}} {v} _ {\ mathrm {dd}} $$(23)V の場合 DS > 4 V T 、式の指数項。 (23)は非常に大きいです。これにより、PSRRのパフォーマンスが V で大幅に向上します。 DS、MP3 増加しています。提案された設計では、最小の V DS、MP3 は200mVを超えています。これは、電源電圧の変化が V にほとんど影響を与えないことを意味します。 REF 。したがって、提案された構造は優れたPSRRパフォーマンスを備えています。

結果と考察

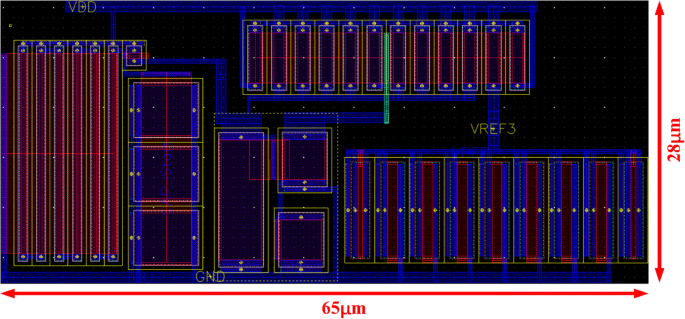

電圧リファレンスは65nm CMOSプロセスで実装されており、そのレイアウトは図4に示され、0.00182 mm 2 を占めています。 アクティブエリア。

提案された回路のレイアウト

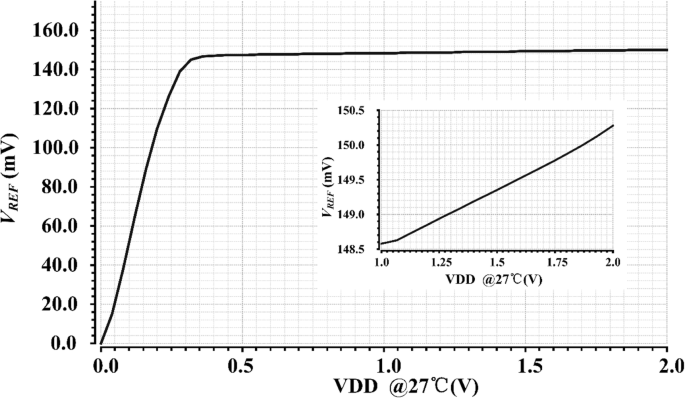

図5は、27°Cでの提案された電圧リファレンスのラインレギュレーションを示しています。図5に示すように、最小供給電圧は350 mVまで低くすることができ、生成された基準電圧は V REF 、約148 mV です。 ライン感度(LS)は1.8 mV / Vです。

V の波形 REF 対供給電圧

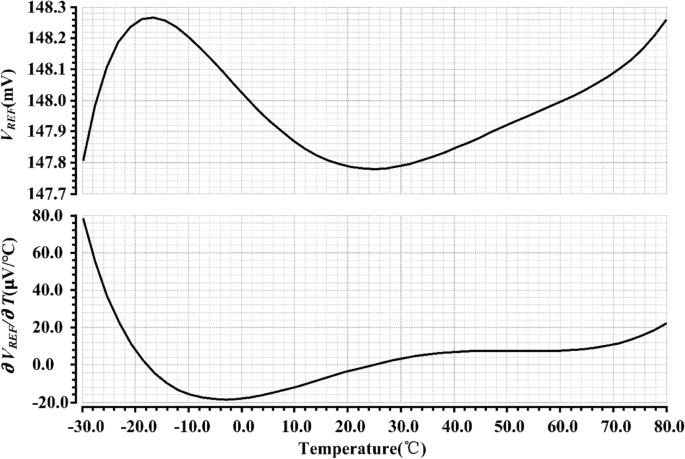

V の温度性能 REF 350mVの供給電圧での場合を図6に示します。 V のTC REF −30から80°Cまで28ppm /°Cです。 V REF は、-15°C未満および25°Cを超える正の温度特性を示し、中温領域では負の温度特性を示します。

V の温度依存性 REF

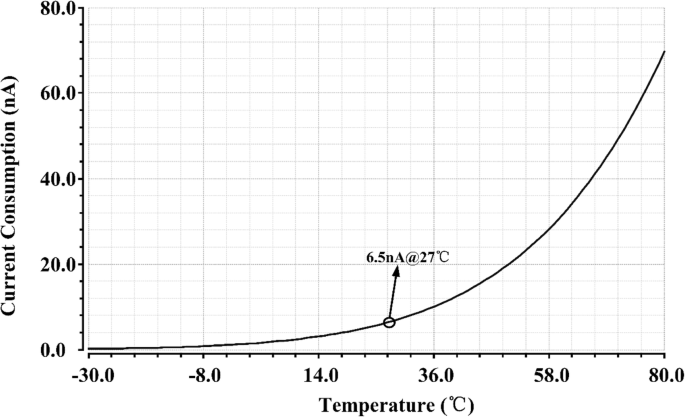

図7は、350mVの供給電圧での消費電流と温度の関係を示しています。電流は正のTCを示しています。室温での消費電力は約2.28nWです。

消費電流対温度

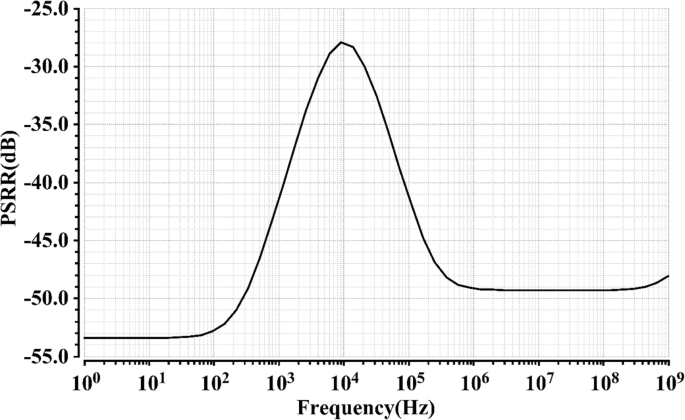

図8は、27°C、350 mVの供給電圧でのPSRRの結果を示しています。ここで、出力フィルタコンデンサなしのPSRRは、53dBを超えて100Hzまでです。上記のように、PSRRのパフォーマンスは、供給電圧を上げることでさらに改善できます。つまり、図8に示すPSRRは、提案された電圧リファレンスの最悪のケースです。

提案された電圧リファレンスのPSRR

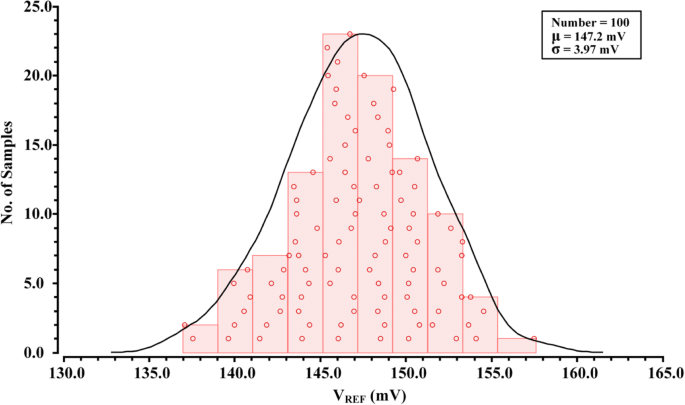

トリミングされていない V の分布 REF 図9に、27°Cで100サンプルを使用した場合の値を示します。 V の平均値と標準偏差 REF はそれぞれ147mVと3.97mVであり、2.7%のスプレッド(σ/μ)になります。

トリミングされていない V の分布 REF

表1は、提案された電圧リファレンスの特性を要約し、以前に報告されたいくつかの電圧リファレンスと比較しています。

<図>結論

この論文では、PSRRが高い抵抗のない低電力電圧リファレンスを紹介します。これは、ナノスケールのアプリケーションに適しており、より高度なプロセスに拡張できます。 MOSFET分圧器に基づく自己バイアス電流源の助けを借りて、必要なCTAT電圧、PTAT電圧、および加重和をコンパクトな構造で同時に実現できます。さらに、CTAT電圧としてデルタしきい値電圧が選択されます。これにより、負のTCが大幅に減少します。これにより、PTAT電圧の必要な値も縮小されます。したがって、供給電圧と消費電流を下げることができます。すべての部品はMOSFETのみで構成されており、SOCなどの電力に敏感な高度に統合されたアプリケーションで優先されます。

略語

- BGR:

-

バンドギャップリファレンス

- CTAT:

-

絶対温度を補完する

- hvt:

-

高しきい値電圧

- LS:

-

ライン感度

- mvt:

-

中程度のしきい値電圧

- PSRR:

-

電源除去率

- PTAT:

-

絶対温度に比例

- TC:

-

温度係数

ナノマテリアル