Tcl を使用したインタラクティブなテストベンチ

対話型テストベンチは、テストベンチの実行中にオペレータが被試験デバイス (DUT) への入力を提供するシミュレータ セットアップです。ほとんどの場合、これはシミュレータ コンソールにコマンドを入力して DUT に刺激を与えることを意味します。

常にセルフチェック テストベンチを作成する必要がありますが、対話型テストベンチは優れた補足になります。セルフチェック テストベンチのコードを変更するよりも、インタラクティブなテストベンチを使用してアドホック テストを実行する方が簡単です。

多くの場合、テストベンチで試してみたい問題がラボで見つかります。インタラクティブなテストベンチを使用すると、観察された入力シーケンスを入力するだけで、シミュレーターで望ましくない動作を再現できます。

VHDL と対話する Tcl

ほとんどの VHDL シミュレータは、コンソール言語として Tcl を使用します。シミュレーターにはベンダー固有のコマンドが多数ありますが、幸いなことに、これらのコマンドは他の Tcl コマンドと同じように扱うことができます。 Tcl を使用して、VHDL テストベンチを管理およびサポートするための複雑で移植性の高いスクリプトを作成できます。

Tcl からの VHDL シグナルの変更

VHDL を操作するには、シグナル値を変更するコマンドを見つける必要があります。 ModelSim では、これは「force」コマンドです。コマンド リファレンス ドキュメントで指定されているように、コマンドの概要は次のとおりです。

force {<object_name> <value> [[@]<time_info>][, <value> [@]<time_info>]...

[-deposit | -drive | -freeze] [-cancel [@]<time_info>] [-repeat [@]<time_info>] 使用するスイッチは「-deposit」フラグです。これにより、VHDL 信号の値が瞬時に変更されますが、別の VHDL または Tcl ドライバーが後で別の値に変更することができます。

使用していないオプションを無視すると、簡略化された概要は次のようになります:

force -deposit <signal_name> <value>

VHDL トリガー

Tcl から VHDL 信号を制御する方法がわかったので、VHDL テストベンチである種のレシーバー プロセスを作成する必要があります。以下のコードは、そのようなテストベンチの最小限の例を示しています。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity interactive is

end interactive;

architecture sim of interactive is

-- Controlled by Tcl

signal trigger : std_logic := '0';

begin

process is

begin

wait until trigger = '1';

report "Triggered!";

end process;

end architecture;

trigger のときにプロセスが起動します。 シグナルが何かから '1' に変わる . 「トリガーされました!」と出力されます。これにより、Tcl から VHDL プロセスを制御する概念をテストできます。

私がやったのは、ModelSim コンソールです。発行されたコマンドと出力は、以下のトランスクリプトで確認できます。

VSIM 1> run 10 ns; VSIM 2> force -deposit /trigger '1' VSIM 3> run 0 ns; # ** Note: Triggered! # Time: 10 ns Iteration: 0 Instance: /interactive VSIM 4> force -deposit /trigger '0' VSIM 5> run 10 ns;

シミュレーション開始後、テストベンチを 10 ナノ秒実行しました。

次に、 trigger を強制しました '1' への合図 .次の行では、0 ナノ秒待ちます。これの目的は、デルタ サイクルを作成することです。プロセスをトリガーしたいのですが、シミュレーション時間が経過したくありません。

最後に、 trigger を強制します '0' に戻る合図 テストベンチを続行する前に。

「run 0 ns」行の後に VHDL プロセスがウェイクアップし、「Triggered!」と出力されていることがわかります。

tcl での VHDL 信号値の読み取り

ModelSim で信号値を読み取るには、「examine」コマンドを使用できます。たとえば、 trigger の値を読み取ることができます ModelSim コンソールで次のコマンドを使用して信号を送ります:

VSIM 6> examine /trigger # 0

スクリプトで「examine」を使用する場合は、値を Tcl 変数に割り当てます。 ModelSim コンソールでこれを試してみましょう:

VSIM 7> set triggerVal [examine /trigger] # 0

次に、たとえば「puts」Tcl コマンドを使用して変数を出力できます。

VSIM 8> puts "triggerVal: $triggerVal" # triggerVal: 0

各テスト後にシミュレーターを停止する

DUT が反応するのに十分な時間テストを実行する最も簡単な方法は、単純にシミュレータを固定時間値で実行することです。たとえば、DUT が 2 クロック サイクル後に反応する必要があり、クロック周期が 10 ナノ秒の場合、Tcl スクリプトでコマンド「20 ns を実行」を使用します。

DUT の反応時間が固定されていない場合は、VHDL アサーションを使用してシミュレーションを停止し、制御を Tcl コールバック関数に渡すことができます。 ModelSim では、これは「when」コマンドを使用して Tcl スクリプトからブレークポイントを設定することを意味します:

when [[-fast] [-id <id#>] [-label <label>] {<when_condition_expression>} {<command>}] また、ブレークポイントに到達したときに実行される「onBreak」コールバック関数を Tcl で定義する必要があります。 「onBreak」関数は、ModelSim コマンド リファレンスで指定されています。

Tcl 駆動型テストの欠点

Tcl スクリプトに大きく依存するテストベンチの使用には欠点があります。最も明らかな問題は、速度と移植性の問題です。

Tcl 駆動のテストベンチは、シミュレーターを複数回起動および停止して VHDL コードとやり取りすることで機能します。シミュレーションの開始と停止の間に Tcl 関数を実行すると、VHDL テストベンチを連続して実行するよりも時間がかかります。 Tcl はインタープリター言語ですが、VHDL はシミュレーターでコンパイルされ、Tcl よりもはるかに高速に実行されます。

Tcl は他のシミュレーターに移植できますが、使用する必要があるシミュレーター固有のコマンドは移植できません。他のシミュレーターで同等のコマンドが見つかった場合でも、動作が異なる場合があります。シミュレーターのベンダーは、サポートするコマンドについて独自のルール セットを作成しています。したがって、Tcl 駆動のテストベンチは、純粋な VHDL テストベンチよりも移植性が低いと見なす必要があります。

新しい VHDL および FPGA コース

* テストベンチを幅広く掘り下げる新しい VHDL および FPGA コースを作成しています。 FPGA デザインをゼロから作成する方法を学習します。コースを修了すると、セルフチェック テストベンチを作成する方法と、コードを再利用して対話型テストベンチを作成する方法がわかります。

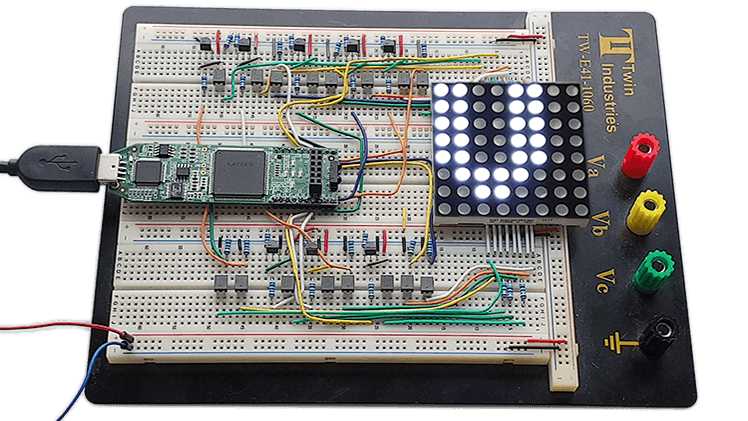

* 2020 年 10 月 12 日に更新: コースを修了しました。詳細については、下の画像をクリックしてください。

今回作成する製品は、ドットマトリクスLEDコントローラーモジュールです。 $49 の Lattice iCEstick 開発ボードを使用します。最後に、ブレッドボードにデザインを実装します。コンピューターのキーボードで入力できるようになり、FPGA によって制御されるドット マトリックス LED スクリーンに文字が表示されます。

ドット マトリックス VHDL および FPGA コースの詳細については、こちらをご覧ください!

開く:

未定 .

VHDL