VHDLとは?

つまり、VHDL はデジタル回路の設計に使用されるコンピューター言語です。

私は「コンピューター言語」という用語を使用して、VHDL を Java や C++ などの他のより一般的なプログラミング言語と区別しています。しかし、VHDL はプログラミング言語ですか?はい、そうです。コンピューター プログラムを作成する際には役に立たないプログラミング言語です!

VHDL は、イベント駆動型の並列プログラミング言語です。コンピュータの CPU で実行できるプログラムの作成には適していませんが、実際の CPU の作成には適しています。これはハードウェア記述言語です。つまり、デジタル ロジックの設計に使用できます。

基本的な VHDL チュートリアル シリーズにアクセスしてください!

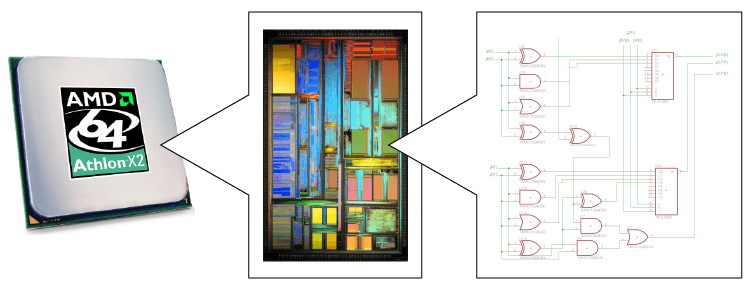

上の図を考えてみましょう。 CPU チップの内部には、ほとんどがデジタルの電子回路がたくさんあります (中央)。これらのデジタル回路は、回路図 (右) を使用して示すことができます。 CPU のような集積回路チップを作成するときは、右側の論理回路図を作成することから始めなければなりません。

このような回路図は、何らかの回路図エディタで作成されていると思われがちですが、実際にはそうではありません。回路は VHDL のようなテキスト言語で記述されます。

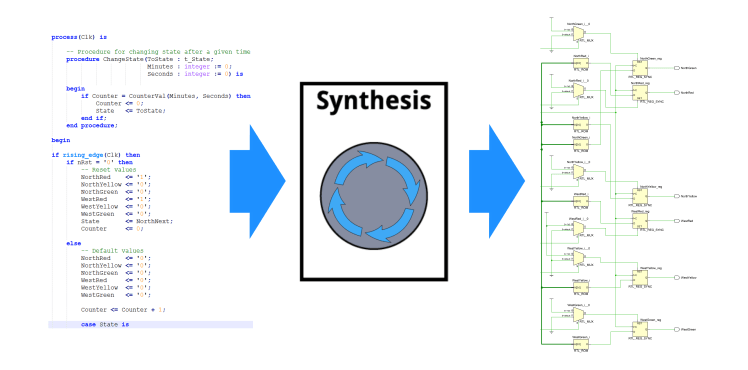

合成

回路図エディタで正確な回路を描く代わりに、VHDL を使用して回路の望ましい動作を記述します。 VHDL コードは、合成と呼ばれるプロセスで正確な回路図に変換できます。 .合成ツールは、VHDL コードを使用して、記述された動作に対する可能な解決策を見つけようとするソフトウェア アプリケーションです。

成功した場合、シンセサイザーからの出力はネットリストになり、回路図エディターで表示できます。

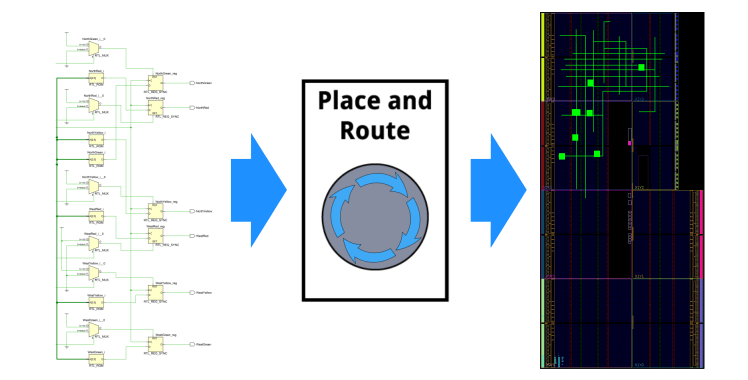

場所とルート

ネットリストは回路の正確な論理的記述を提供しますが、物理的な実装については何も述べていません。物理レイアウトの正確な説明を導き出すために、ネットリストは配置配線と呼ばれるプロセスを経て実行されます 、または略してPAR。ルーターは、ネットリストの要素をターゲット デバイスの物理コンポーネントに割り当てようとします。また、すべてのコンポーネント間でワイヤを配線する必要があります。ルーターが解決しなければならない巨大なパズルです!

成功した場合、PAR からの出力は別の種類のネットリストになります。このネットリストには配置および配線情報が含まれており、ターゲット デバイス タイプに固有です。ターゲット デバイスが FPGA の場合、配線されたネットリストをプログラミング ファイルに変換できます。ターゲット デバイスが ASIC の場合、状況はもう少し複雑になります。

では、VHDL とは何ですか?

これは、集積回路のデジタル ロジックを作成するために使用される一種のプログラミング言語です。

基本的な VHDL チュートリアルはこちら>>

VHDL