チュートリアル - VHDL の紹介

VHDL はひどい頭字語です。 V の略です HSIC H ハードウェア D 説明 L 言語。頭字語の中の頭字語、素晴らしい! VHSIC は V の略です ery H ぐっ S おしっこ 私 総合C イライラする。したがって、展開された VHDL は V です。 ery 高速集積回路 H ハードウェア D 説明 L 言語。 PHEWそれは一口です。 VHDL は、FPGA と ASIC を設計するために教育とビジネスで使用される 2 つの言語のうちの 1 つです。これらの魅力的な回路に慣れていない場合は、FPGA と ASIC の概要から最初に恩恵を受けることができます。 VHDL と Verilog は、デジタル デザイナーが回路を記述するために使用する 2 つの言語であり、C や Java などの従来のソフトウェア言語とは設計が異なります。

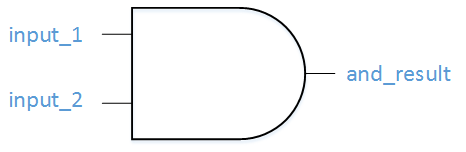

以下の例では、記述する VHDL ファイルを作成します。 アンドゲート。復習として、単純な And ゲートには 2 つの入力と 1 つの出力があります。出力は、両方の入力が 1 に等しい場合にのみ 1 に等しくなります。以下は、VHDL で説明する And ゲートの図です。

アン アンド ゲート

アン アンド ゲート 始めましょう! VHDL の基本単位は シグナル と呼ばれます .ここでは、信号が 0 または 1 のいずれかであると仮定しましょう (実際には他の可能性がありますが、それについて説明します)。基本的な VHDL ロジックは次のとおりです。

signal and_gate : std_logic; and_gate <= input_1 and input_2;

コードの最初の行は、タイプ std_logic の信号を定義し、and_gate と呼ばれます。 Std_logic はシグナルを定義するために最も一般的に使用されるタイプですが、他にも学ぶことがあります。このコードは、1 つの出力 (and_gate) と 2 つの入力 (input_1 および input_2) を持つ AND ゲートを生成します。キーワード「and」は VHDL で予約されています。 <=演算子は代入演算子として知られています。上記のコードを口頭で解析する場合、「シグナル and_gate は input_1 を取得し、input_2 を取得します」と大声で言うことができます。

ここで、input_1 と input_2 がどこから来たのか自問しているかもしれません。それらの名前が示すように、それらはこのファイルへの入力であるため、ツールにそれらについて伝える必要があります。ファイルへの入力と出力は エンティティ で定義されます .エンティティには、ファイルへのすべての入力と出力を定義するポートが含まれています。簡単なエンティティを作成しましょう:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

これはあなたの基本的なエンティティです。 example_and と呼ばれるエンティティと 3 つの信号、2 つの入力と 1 つの出力を定義します。これらはすべて std_logic 型です。これを完成させるには、もう 1 つの VHDL キーワードが必要です。それは アーキテクチャ です。 .アーキテクチャは、特定のエンティティの機能を記述するために使用されます。論文と考えてください。エンティティは目次であり、アーキテクチャはコンテンツです。このエンティティのアーキテクチャを作成しましょう:

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

上記のコードは、エンティティ example_and の rtl と呼ばれるアーキテクチャを定義します。アーキテクチャで使用されるすべてのシグナルは、「is」キーワードと「begin」キーワードの間で定義する必要があります。実際のアーキテクチャ ロジックは、「begin」キーワードと「end」キーワードの間にあります。このファイルはほぼ完了です。最後にツールに伝える必要があるのは、使用するライブラリです。ライブラリは、特定のキーワードがファイル内でどのように動作するかを定義します。今のところ、ファイルの先頭に次の 2 行が必要であることは当然のことと考えてください:

library ieee; use ieee.std_logic_1164.all;

おめでとう!最初の VHDL ファイルが作成されました。ここで完成したファイルを見ることができます:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

愚かなゲートを作成するためだけに多くのコードを書かなければならなかったように見えますか?まず第一に、ゲートは愚かではありません。第二に、あなたは正しいです。 VHDL は非常に冗長な言語です。ソフトウェアでは非常に簡単だったことが、Verilog や VHDL などの HDL では非常に長くかかるという事実に慣れてください。しかし、ソフトウェア担当者に、Conway のライフ ゲームを表示する VGA モニターに画像を生成するように依頼してください。ちなみにあの動画はVHDLとFPGAで作っています。すぐにできるようになります!

VHDL