変数 - VHDL の例

VHDL の変数は、C の変数と同様に機能します。それらの値は、変数が変更されたコード内の正確な位置で有効です。したがって、シグナルが変数 before の値を使用する場合、 割り当て、それは古い変数値を持ちます。シグナルが変数 after の値を使用する場合 新しい変数値を持つ代入。

変数のルール:

- 変数はプロセス内でのみ使用できます

- あるプロセスで作成された変数は、別のプロセスでは使用できません

- キーワード process の後に変数を定義する必要があります ただし、キーワード begin の前

- 変数は := を使用して割り当てられます 割り当て記号

- 割り当てられた変数は、割り当ての値をすぐに取得します

理解しておくべき最も重要なことは、変数は割り当ての値をすぐに取得するということです。 変数を使用する便利な方法の 1 つを示す例を次に示します:一時的に使用するためのデータの保存 . case ステートメントとアンパサンド (&) 連結演算子を使用します。

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

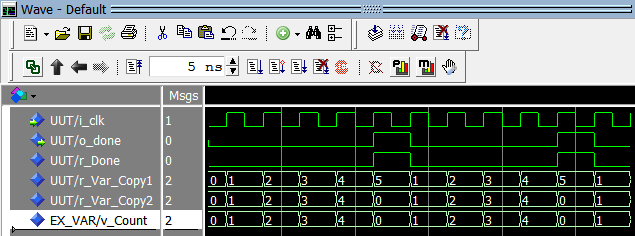

前の例では、case ステートメントで使用できるように 2 つのシグナルを連結しました。変数 v_Choices は、割り当てられるとすぐに使用できるようになりました。別の例を見てみましょう。以下の例はより包括的で、変数が割り当ての値をすぐに取得する方法を示しています。信号 r_Var_Copy1 と r_Var_Copy2 は同じように見えますが、r_Var_Copy2 はリセットされる前に 5 になることはありません。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

デザインをシミュレートするには、テストベンチを作成する必要があります。また、変数はシミュレーションで表示するのが少し難しい場合があります。 Modelsim を使用している場合は、Modelsim の波形ウィンドウで変数を表示する方法について詳しくお読みください。

テストベンチ:

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

変数 サンプル テストベンチ波形

変数 サンプル テストベンチ波形 上記の例は、変数がシグナルとはどのように異なる動作をするかを示しています。信号 r_Var_Copy1 と r_Var_Copy2 は同じように見えますが、r_Var_Copy2 はリセットされる前に 5 になることはありません。

VHDL