プロセッサを信頼できるものにする方法

最新の集積回路(IC)は、膨大な量のデータを処理し、リアルタイムでセーフティクリティカルな決定を下し、機密データを保護するための計算機能とシステム制御機能を提供します。特定用途向け集積回路(ASIC)またはフィールドプログラマブルゲートアレイ(FPGA)システムオンチップ(SoC)をゼロから設計することは、非常に費用と時間がかかります。多くの重要な機能は、サードパーティの知的財産(IP)を使用して実装されます。たとえば、プロセッサコアは専門組織から供給され、ハードウェアとソフトウェア間のインターフェイスを定義する命令セットアーキテクチャ(ISA)を通じて、柔軟でソフトウェアでプログラム可能な機能を提供します。オープンソースのプロセッサアーキテクチャは、流動的な脅威環境にすでに直面しているシステムにおいて、より詳細な調査と厳格なセキュリティ保証の機会を提供します。この記事では、RISC-VオープンソースISAに基づいてIPおよびSoCのセキュリティ保証を提供するためのアプローチについて説明します。

カリフォルニア大学で発明され、非営利のRISC-V Foundationによって管理されている、RISC-Vは、幅広いアプリケーションで真に実行可能な産業上の選択肢となった最初のオープンソースISAです。

RISC-Vは、カリフォルニア大学で発明され、2015年に設立された300人以上のメンバーを持つ非営利組織であるRISC-V Foundationによって管理されているオープンソースISAです。RISC-Vは、幅広いアプリケーションで真に実行可能な産業上の選択。ツール、ソフトウェア、専門知識のエコシステムは堅牢で、着実に成長しています。多くの個人や組織が、RISC-VISAを実装するオープンソースハードウェアIPをすでに寄付しています。たとえば、OpenHW Groupは、大容量チップ向けのオープンソースハードウェア(特にプロセッサコア)の待望の展望を実現することを目指しています。

RISC-Vの台頭には、多くの理由があります。カスタム拡張性を念頭に置いてゼロから構築されたRISC-Vは、特定のワークロードに対して新しいレベルのハードウェア最適化を可能にします。ムーアの法則は減速しており、半導体製造プロセスの技術的進歩ではもはや提供できないレベルのパフォーマンス向上を維持するには、カスタマイズが不可欠です。さらに、RISC-Vアーキテクチャにはライセンス費用や使用料がかからないため、より多くの企業が革新的で手頃な価格の製品を開発できます。たとえば、IoTや人工知能機能を備えたウェアラブルデバイスの分野で多くのことが起こっています。

SoCインテグレータは、多くの場合、オープンソースまたはサードパーティのRISC-VプロセッサIPを使用します。これらの設計とそれに関連するツールチェーンは、カスタム命令で拡張できます。 IPと追加のシステムレベルのテストで提供される高品質の検証環境は、IPに重大なバグがないことをある程度確信させることができます。残念ながら、多くのアプリケーションでは、これだけでは不十分であり、考慮すべき他の重大なリスクがあります。

脆弱性とトロイの木馬

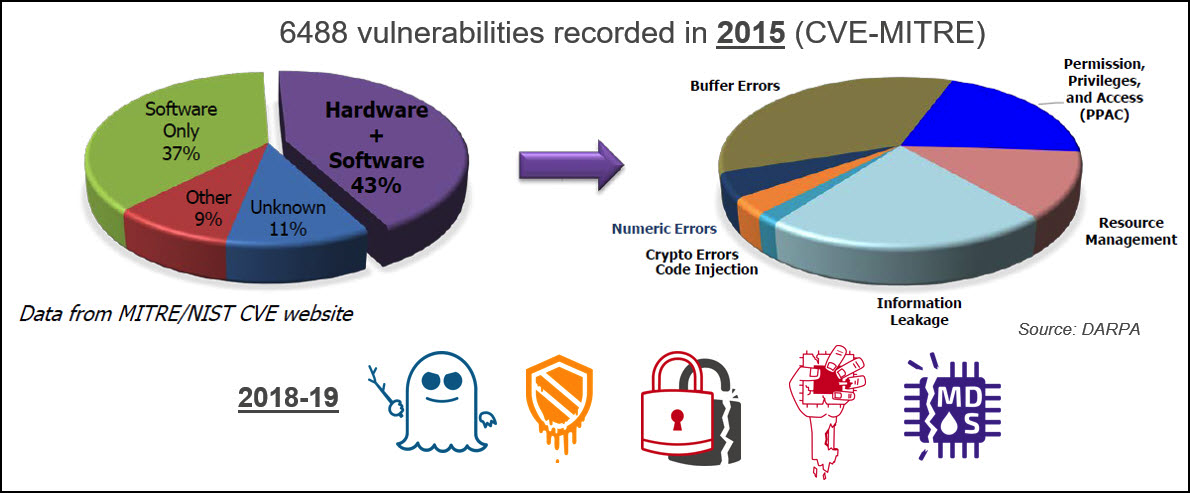

従来、電子システムのセキュリティの脆弱性は、システムレベルおよびソフトウェアの問題に関連付けられてきました。最近では、主にプロセッサであるハードウェアIPも中心的な関心事になっています(図1を参照)。プロセッサの実装では、パイプラインベースのマイクロアーキテクチャが使用され、多くの場合、パフォーマンスと電力の最適化機能が含まれています。複雑さは、機能上のバグだけでなく、セキュリティの脆弱性も見逃すリスクを高めます。 2018年の初めにメルトダウン攻撃とスペクター攻撃を発見したセキュリティ研究者は、プロセッサのパフォーマンス最適化機能が悪意のある目的で意図しない方法で使用される可能性があることを示しました。それ以来、ハイエンドプロセッサとローエンドプロセッサの両方でさらに多くの脆弱性が発見されています。サイドチャネル攻撃と一時的な実行攻撃により、安全なエンクレーブが侵害され、悪意のあるアプリケーションが機密データを漏洩したり、システムの制御を乗っ取ったりする可能性があります。また、ソフトウェアとは異なり、ハードウェアの問題は無線アップデートでは簡単に修復できません。ソフトウェアを介してハードウェアの問題に対処すると、パフォーマンスが大幅に低下することがよくあります。

RISC-Vアーキテクチャには、安全な組み込みシステムの実装をサポートする多くの機能があります。特権仕様では、たとえば、4つの特権モード(マシン、スーパーバイザー、ハイパーバイザー、およびユーザー)が定義されています。暗号化拡張機能など、承認される過程でのカスタム命令とISA拡張機能は、追加のセキュリティ機能を提供します。設計者は、複数の安全なエンクレーブを実装して、アプリケーションを分離し、機密データの漏洩を防ぐことができます。ただし、RTLのマイクロアーキテクチャ機能により、セキュリティの脆弱性が発生する可能性があります。これらのリスクは、ISAレベルで完全に対処することはできません。調査中の新しいアプローチは、拡張ISA(aISA)を使用して、マイクロアーキテクチャレベルで命令実行の側面を定義し、たとえば、ISAレベルでは表示されないバッファまたはレジスタの状態を制御することです。 RTLの機能上のバグは、これらすべてのセキュリティ機能を危険にさらす可能性があります。

リスクは低くなりますが、重大度ははるかに高くなりますが、RISC-Vコアに悪意のあるロジックまたはハードウェアトロイの木馬が存在します。ハードウェアトロイの木馬は、ステルスになるように意図的に設計された論理関数であり、攻撃者だけが知っている非常にまれな状況でアクティブになります。システムがターゲットのユースケースで動作している間は発生しない特定の一連のデータおよび制御イベントがトロイの木馬ロジックをトリガーし、トロイの木馬ロジックが有害なペイロードを配信し、秘密を漏らしたり、システムの動作を著しく破壊したりします。オープンソースまたはサードパーティのRISC-Vコアを使用したSoC統合では、このリスクを無視できなくなりました。

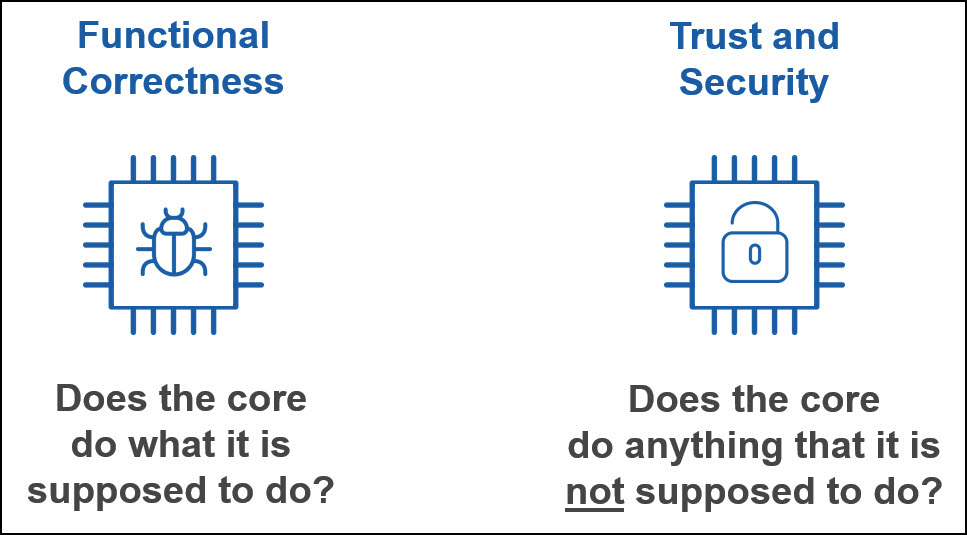

プロセッサが想定されていることを実行することを保証することは困難ですが、プロセッサが実行することを想定されていないことを実行しないことを保証することは、まだほとんど対処されていないさらに困難な作業です。セーフティクリティカルシステムおよびデータプライバシーの保護が最優先されるシステムには、セキュリティの脆弱性とトロイの木馬のリスクに対処する効率的で高品質のソリューションが必要です。

図1:CVE-MITREデータベースは2015年に6488の脆弱性を記録し、その43%はソフトウェア支援のハードウェア脆弱性として分類できます。 2018年と2019年に、研究者はMeltdownとSpectre、Foreshadow、ZombieLoad、RIDLとFalloutなど、プロセッサに多数の脆弱性を発見して報告しました。 (出典:DARPAおよびOneSpin)

スマートハードウェア保証

RISC-V IPの信頼性とセキュリティを確保するには、主にIPの使用目的を対象とした、機能的正当性アプローチを補完する革新的で効率的な技術ソリューションが必要です(図2を参照)。 IPプロバイダーは、最先端の信頼とセキュリティの検証プロセスを適用する責任がありますが、IPインテグレーターは、IP実装の詳細についての深い知識がなくても、迅速に展開できる独立した保証ソリューションにアクセスできる必要があります。

形式手法は、ハードウェア機能を徹底的に分析し、IPまたはSoCがSystemVerilogアサーションでしばしばキャプチャされる予想される動作と正確に一致するという証拠を提供できます。商用モデルチェッカーを使用したハードウェアフォーマル検証は、過去10年間で広く採用されてきました。通常、IPプロバイダーとSoCインテグレーターには、機能的なバグを見逃すリスクを最小限に抑えるために、フォーマル検証の専門家がランクインしています。特定の明確に定義されたフォーマル検証タスクは、アプリを介して自動化できます。 、一般に、アサーションでIPの予想される動作をキャプチャするには、かなりのエンジニアリング作業が必要です。さらに、十分なアサーションが書き込まれたという保証はありません。文書化されていない機能または一連のアサーションの意図しないギャップにより、未検証のIP機能が発生する可能性があります。

RISC-Vのオープンソースの性質により、パッケージ化された独立した保証ソリューションの開発が可能になります。たとえば、OneSpinのRISC-V整合性検証ソリューションは、さまざまなマイクロアーキテクチャに適用できます。これには、拡張可能でカスタム命令に対応できるRISC-VISAおよび特権ISAのモデルが含まれています。このソリューションの重要な側面は、OneSpinのGapFreeVerification™プロセスに基づいていることです。これにより、RISC-V ISAをモデル化する一連のアサーションが完全であり、ギャップがないことを厳密に証明できます。この側面は、ハードウェアトロイの木馬または文書化されていないロジックの検出が重要な目標である場合に最も重要です。このソリューションにより、RISC-VとRTLの実装に関する専門知識が限られているSoCインテグレーターは、IPの品質と信頼性に自信を持てるようになります。 IP開発者はこれを使用して、リリース前にセキュリティの弱点や機能上のバグを検出できます。

図2:機能の正当性の検証により、プロセッサの実装が指定どおりに動作し、エンドユーザーの要件を満たしていることが保証されます。一方、信頼とセキュリティの検証は、プロセッサに文書化されていない機能、予期しないサイドチャネル、ハードウェアトロイの木馬、または悪意のある攻撃者によって悪用される可能性のあるその他の脆弱性がないことを保証します。 (出典:OneSpin)

機能しますか?

前のセクションで説明したRISC-V整合性保証プロセスは、複数のRTL設計に正常に適用されています。たとえば、米国国防総省や商業部門のさまざまな顧客向けにシステムとプロセスのシステムを迅速に最適化、保証、自動化する革新的なソリューションを統合する企業であるEdaptive Computingは、このプロセスをRocketCoreに適用しました。 RocketCoreは、39ビットの仮想メモリシステムを備えた、シリコンで実証済みのオープンソースの64ビットRISC-Vコアです。これには、除算などの長いレイテンシー命令のためのアウトオブオーダー完了を備えた、5段階の単一発行のインオーダーパイプラインがあります。分岐予測と命令再生の高度な機能が含まれています。

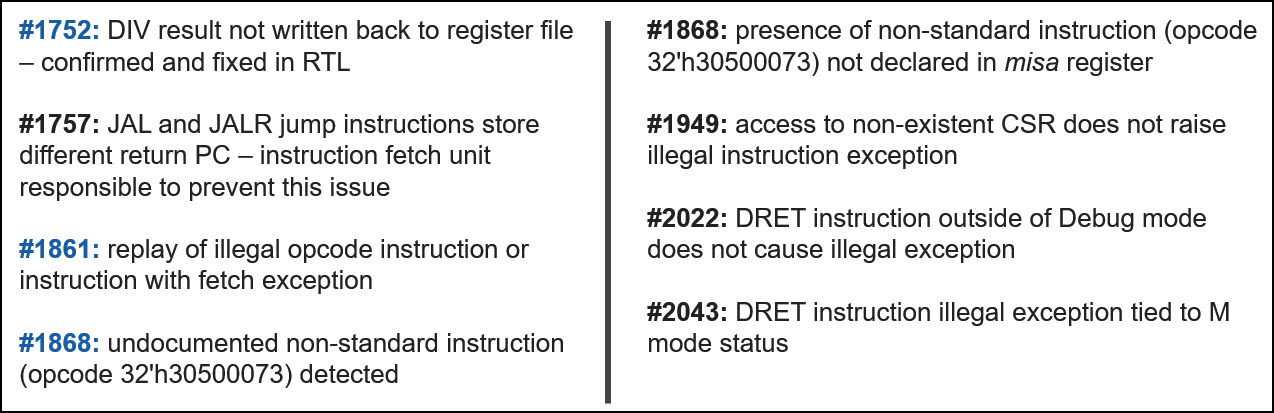

RISC-V整合性検証ソリューションは、すべての命令、特権レベル、割り込み、および例外メカニズムを使用してデザインに適用され、8つの問題が検出されました(図3を参照)。そのうちの3つに関する追加情報を以下に報告します。

分割コーナーケース :除算命令のアウトオブオーダー完了に関連する深いコーナーケースのバグ。この問題により、除算演算を使用するソフトウェアプログラムが誤った結果を計算し、システムの誤動作を引き起こす可能性があります。この問題はまれな状況の組み合わせでのみ発生するため、以前の検証作業では問題が発生していませんでした。

違法な指示の再生 :これはコーナーケースのバグではありません。不正な命令を再生すると処理サイクルが無駄になる可能性がありますが、これがまれな状況でのみ発生する場合、パフォーマンスへの影響はごくわずかです。ただし、考慮すべき他の側面があります。命令の再生により、不要なメモリ要求が発生する可能性があります。これらのリクエストには、サイドチャネル攻撃で利用される可能性のある副作用が含まれる可能性があります。結果として、この振る舞いは排除されるか、明確に理解され、文書化される必要があります。

文書化されていない指示 :コアを停止するCEASEと呼ばれる文書化されていない非標準の命令が検出されました。事実上、RISC-V RocketCoreは、想定外のことを実行できます。文書化されていない隠された機能は、信頼とセキュリティが懸念される場合、最終的なアプリケーションに関連しないと見なされるユースケースに関連している場合でも受け入れられません。

RocketCoreのケーススタディは、GOMACTech2019の論文「トロイの木馬のない信頼できるIC用のRISC-VプロセッサIPの完全なフォーマル検証」に詳細に示されています。 コピーを入手するには、onespin.com / resources / white-papersにアクセスしてください。

図3:OneSpinのRISC-V整合性検証ソリューションによって検出され、GitHubRocketCoreプロジェクトで報告された問題のリスト。 (出典:OneSpin)

次は何ですか?

この記事で紹介するRISC-V保証プロセスは、セキュリティに影響を与える可能性のあるシナリオを検出し、プロセッサの動作に影響を与える文書化されていない機能とハードウェアトロイの木馬を、それらがどれほどまれでステルスであるかに関係なく体系的に明らかにします。ただし、サイドチャネルは体系的に検出されません。すべての潜在的なサイドチャネルを徹底的に検出するには、適切なテクノロジーを備えた専用のソリューションが必要です。この課題に対処するプロトタイプはすでに存在します。詳細については、onespin.com / resources / technical-articlesにアクセスしてEETimesの記事組み込みプロセッサへのサイドチャネル攻撃をお読みください。

プロセッサコアは、組み込みシステム内の重要なIPです。ただし、一般的なSoCは、ハードウェアトロイの木馬を含む可能性のある他の多くのIPを統合します。 RISC-Vコアとは異なり、独立した信頼保証ソリューションはすぐには利用できない場合があります。この場合、すべてのIPに適用できる自動化された手間のかからない信頼性評価プロセスを用意することは価値があります。 IPの信頼できるモデルを含まないプロセスでは、トロイの木馬が存在しないことを保証できません。ただし、異常で疑わしいコードパターンや既知のトロイの木馬のシグネチャ、および後の開発段階で悪用される可能性のある弱点を特定することは可能です。このトピックに関する論文「ハードウェア保証のための自動化されたシリコン前IPの信頼性評価」 は、AEROSPACE CorporationとOneSpinのエンジニアによって作成され、GOMACTech2020カンファレンスで発表されます。

埋め込み