非同期カウンター

前のセクションでは、11から10、01から00までの2ビットのバイナリシーケンスで逆方向にカウントされる1つのJ-Kフリップフロップを使用する回路を見ました。

前方を数えることができる回路を持つことが望ましいので 逆方向だけでなく、順方向のカウントシーケンスをもう一度調べて、そのような回路を構築する方法を示す可能性のあるパターンをさらに探すことは価値があります。

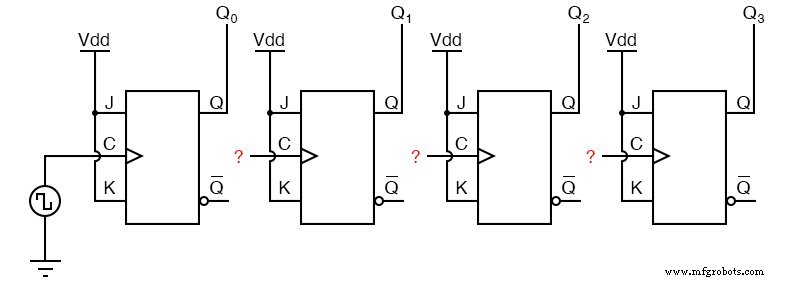

バイナリカウントシーケンスはオクターブ(2倍)の周波数分割のパターンに従い、「トグル」モード用に設定されたJKフリップフロップマルチバイブレータはこのタイプの周波数分割を実行できることがわかっているので、回路を想像できます。いくつかのJKフリップフロップで構成され、カスケード接続されて4ビットの出力を生成します。

私たちが直面している主な問題は、方法を決定することです。 これらのフリップフロップを接続して、適切なタイミングでトグルし、適切なバイナリシーケンスを生成します。

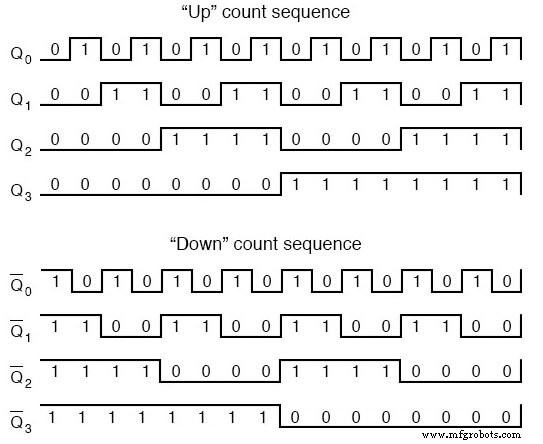

0と1の間のビットの「トグル」に先行するパターンに注意して、次のバイナリカウントシーケンスを調べます。

この4ビットシーケンスの各ビットは、その前のビット(重要度の低いビット、つまり場所の重み)が特定の方向(1から0)に切り替わるときに切り替わることに注意してください。

小さな矢印は、ビットが切り替わるシーケンス内のポイントを示します。矢印の頭は、前のビットを指し、「高」(1)状態から「低」(0)状態に移行します。

常に「トグル」モードになるように接続された4つのJKフリップフロップから始めて、クロック入力を接続して、1から遷移する前のビットが1から遷移するときに後続の各ビットがトグルするようにする方法を決定する必要があります。 0に。

各フリップフロップのQ出力は、最終的な4ビットカウントのそれぞれのバイナリビットとして機能します。

ネガティブエッジトリガー(クロック入力のバブルシンボル)を備えたフリップフロップを使用した場合、各フリップフロップのクロック入力をその前のフリップフロップのQ出力に接続するだけで、前のビットが1から0に変化すると、その信号の「立ち下がりエッジ」が次のフリップフロップを「クロック」して、次のビットを切り替えます。

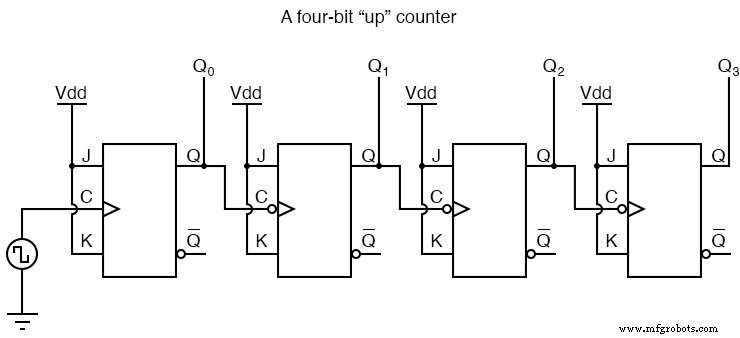

4ビットの「アップ」カウンター

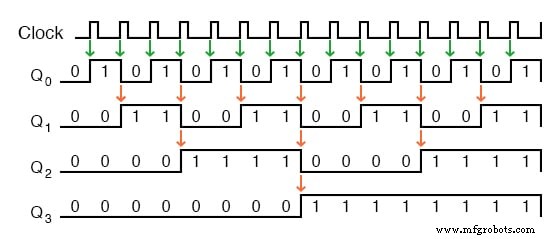

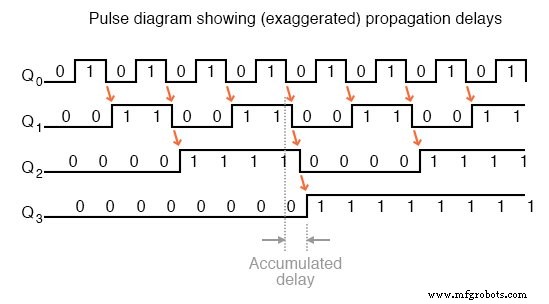

この回路は、発振器からのパルスの繰り返しソースによって「クロック」されると、次の出力波形を生成します。

最初のフリップフロップ(Q 0 のフリップフロップ) 出力)、ポジティブエッジでトリガーされるクロック入力があるため、クロック信号の立ち上がりエッジごとに切り替わります。

この例のクロック信号のデューティサイクルが50%未満であることに注意してください。

4ビットのバイナリシーケンスで信頼性の高い「クリーンな」出力ビットを取得するためにクロック信号を対称にする必要がないことを示す目的で、この方法で信号を示しました。

この章で示した最初のフリップフロップ回路では、クロック信号自体を出力ビットの1つとして使用しました。

ただし、これはカウンタ設計では悪い習慣です。これは、すべてのステップでカウントシーケンスを取得するために、50%のデューティサイクル(「高」時間=「低」時間)の方形波信号を使用する必要があるためです。同じ時間一時停止します。

ただし、出力ビットごとに1つのJ-Kフリップフロップを使用すると、対称的なクロック信号が不要になり、カウントシーケンスをインクリメントするために実質的にあらゆる種類のハイ/ロー波形を使用できるようになります。

パルス図の他のすべての矢印で示されているように、後続の各出力ビットは、「ハイ」(1)から「ロー」(0)に遷移する前のビットのアクションによって切り替えられます。

これは、「アップ」カウントシーケンスを生成するために必要なパターンです。

ポジティブエッジでトリガーされるフリップフロップを使用して「アップ」シーケンスを生成するためのあまり明白でない解決策は、Q出力ではなく前のフリップフロップのQ ’出力を使用して各フリップフロップを「クロック」することです。

Q '出力は常にJKフリップフロップのQ出力とは正反対の状態になるため(このタイプのフリップフロップでは無効な状態はありません)、Q出力のハイからローへの遷移には付随します。 Q '出力のローからハイへの遷移。

言い換えると、フリップフロップのQ出力が1から0に遷移するたびに、同じフリップフロップのQ '出力が0から1に遷移し、正方向のクロックパルスを提供します。適切なタイミングでポジティブエッジトリガーフリップフロップ:

代替の4ビット「アップ」カウンター

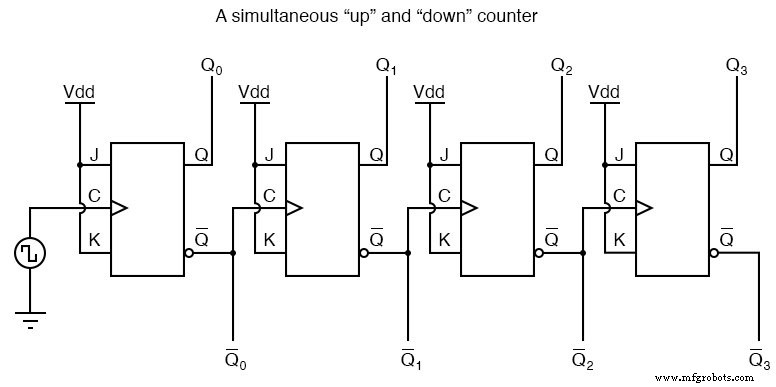

これら2つのカウンタ回路のいずれかの機能を拡張する1つの方法は、Qの出力を4つのバイナリビットの別のセットと見なすことです。

このような回路のパルス図を調べると、Q ’出力がダウンを生成していることがわかります。 -カウントシーケンス、Q出力は up を生成します -カウントシーケンス:

「上」と「下」の同時カウンター

残念ながら、これまでに示したすべてのカウンタ回路には共通の問題があります。リップル 効果。

この効果は、特定のタイプのバイナリ加算器およびデータ変換回路で見られ、カスケードゲート間の累積的な伝搬遅延が原因です。

フリップフロップのQ出力が1から0に遷移すると、次のフリップフロップにトグルするように命令します。

次のフリップフロップのトグルが1から0への遷移である場合、その後のフリップフロップにもトグルするように命令します。

ただし、トグルするコマンド(クロックパルス)と実際のトグル応答(QおよびQ '出力の状態変化)の間には常に少量の伝搬遅延があるため、トグルされる後続のフリップフロップはしばらくの間トグルします後 最初のフリップフロップが切り替わりました。

したがって、バイナリカウントシーケンスで複数のビットが切り替わる場合、それらすべてがまったく同時に切り替わるわけではありません。

非同期カウンター回路のデメリット:伝搬遅延

ご覧のとおり、特定のクロックパルスで切り替わるビットが多いほど、LSBからMSBまでの累積遅延時間が厳しくなります。

このような遷移点でクロックパルスが発生すると(たとえば、0111から1000への遷移時に)、後続の各ビットがトグルし、次のビットにもトグルするように命令するため、出力ビットはLSBからMSBに順番に「リップル」します。 、各ビットトグル間の伝播遅延がわずかです。

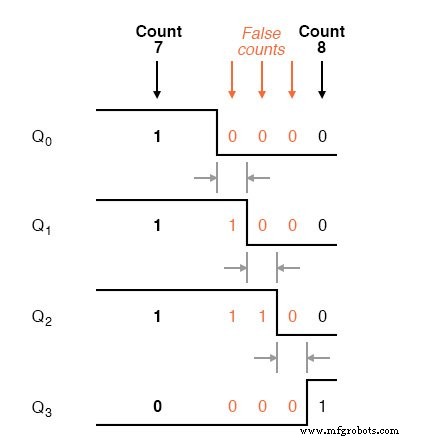

0111から1000への移行中にこの効果をクローズアップすると、 false が発生することがわかります。 「リップル」効果が発生する短い期間に生成された出力カウント:

「0111」出力から「1000」出力にきれいに遷移する代わりに、カウンタ回路は0111から0110、0100、0000、1000、または7から 6 に非常にすばやくリップルします。 〜 4 0 へ この動作により、カウンター回路にリップルカウンターという名前が付けられます。 、または非同期カウンター 。

ストロボ信号カウンタ回路

多くのアプリケーションでは、リップルが非常に迅速に発生するため、この影響は許容できます(影響を理解するために、ここでは遅延の幅を誇張しています)。

たとえば、カウンタの出力で発光ダイオード(LED)のセットを駆動するだけの場合、この短いリップルはまったく重要ではありません。

ただし、このカウンタを使用してマルチプレクサの「選択」入力を駆動したり、マイクロプロセッサ(コンピュータ)回路のメモリポインタにインデックスを付けたり、誤った出力が誤ったエラーを引き起こす可能性があるその他のタスクを実行したりする場合は、受け入れられません。 。

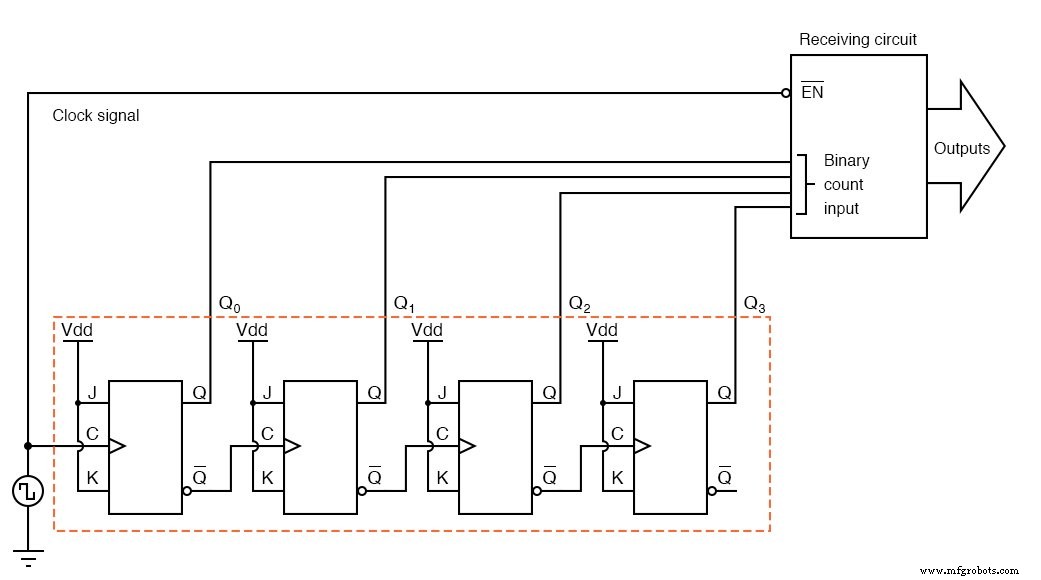

誤ったリップル生成出力に敏感なアプリケーションでこのタイプのカウンタ回路を使用する方法があり、これにはストロービングとして知られる原理が含まれます。 。

ほとんどのデコーダおよびマルチプレクサ回路には、「イネーブル」と呼ばれる入力が少なくとも1つ装備されています。

このような回路の出力は、イネーブル入力がアクティブになった場合にのみアクティブになります。

このイネーブル入力を使用して、ストロボに入力できます。 リップルカウンタの出力を受信する回路。これにより、カウンタ出力が波打つ可能性のある短い期間は無効になり(したがって、カウンタ出力に応答しなくなり)、最後のクロックパルスから十分な時間が経過した場合にのみ有効になります。すべての波打つことが止まるでしょう。

ほとんどの場合、ストローブ信号は、カウンタ回路を駆動するのと同じクロックパルスにすることができます。

アクティブローイネーブル入力を使用すると、受信回路は、クロック信号が「ロー」の場合にのみ、4ビットカウンタ回路のバイナリカウントに応答します。

クロックパルスが「ハイ」になるとすぐに、受信回路はカウンタ回路の出力に応答しなくなります。

カウンター回路はポジティブエッジでトリガーされるため(最初の フリップフロップクロック入力)、すべてのカウント動作はクロック信号のローからハイへの遷移で行われます。つまり、カウンタ回路の4つの出力ビットでトグルが発生する直前に受信回路が無効になります。

>受信回路は、クロック信号がロー状態に戻るまで有効になりません。ロー状態は、後に十分な時間が必要です。 新しいカウントが受信回路に影響を与えることができるように、すべての波打つことは「安全」ではなくなりました。

ここで重要なパラメータは、クロック信号の「ハイ」時間です。少なくとも、カウンタ回路の予想される最大リップル周期と同じ長さである必要があります。

そうでない場合、クロック信号は受信回路を早期に有効にしますが、波打つことはまだ発生しています。

非同期カウンター回路の欠点:制限された速度

非同期またはリップルのカウンター回路のもう1つの欠点は、速度が制限されることです。

すべてのゲート回路は最大信号周波数に関して制限されていますが、非同期カウンター回路の設計は、伝搬遅延を追加することによってこの問題を悪化させます。

したがって、受信回路でストローブが使用されている場合でも、非同期カウンタ回路は、次のパルスのかなり前に最大の累積伝搬遅延が経過することを可能にする周波数よりも高い周波数でクロックを供給することはできません。

この問題の解決策は、リップルを完全に回避するカウンタ回路です。

このようなカウンター回路は、カウンター出力を入力として使用するデジタル回路に「ストロービング」機能を設計する必要をなくし、非同期の同等のものよりもはるかに高速な動作速度を享受します。

このカウンタ回路の設計は、次のセクションの主題です。

レビュー:

- 「アップ」カウンタは、ポジティブエッジでトリガーされたJ-Kフリップフロップのクロック入力を先行するフリップフロップのQ ’出力に接続することで作成できます。もう1つの方法は、ネガティブエッジでトリガーされるフリップフロップを使用して、クロック入力を先行するフリップフロップのQ出力に接続することです。いずれの場合も、すべてのフリップフロップのJおよびK入力はV cc に接続されます。 またはV dd 常に「高く」なるように。

- カスケード接続されたJ-Kフリップフロップで作られたカウンター回路では、各クロック入力が前のフリップフロップの出力からパルスを受信し、常にリップル効果を示します。 、カウントシーケンスのいくつかのステップの間に誤った出力カウントが生成されます。これらのタイプのカウンター回路は、非同期カウンターと呼ばれます。 、またはリップルカウンター 。

- ストロービング は、非同期(リップル)カウンタの出力を受信する回路に適用される手法であるため、リップル時間中に生成された誤ったカウントが悪影響を与えることはありません。基本的に、有効 このような回路の入力は、カウンタ出力が変化していないときにのみ有効になり、リップルが発生するカウンタ出力が変化している間は無効になるように、カウンタのクロックパルスに接続されます。

関連するワークシート:

- リップルカウンターワークシート

産業技術