TTLNANDおよびANDゲート

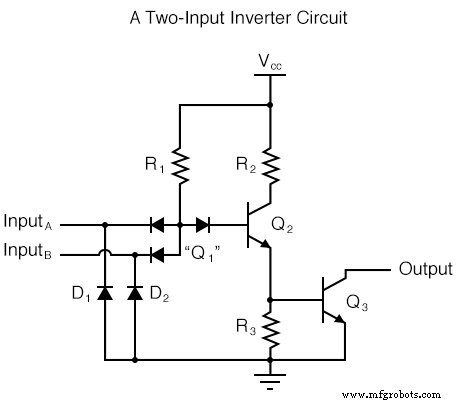

基本的なオープンコレクターインバーター回路を変更し、最初の入力端子と同じように2番目の入力端子を追加したとします。

この回路図は実際の回路を示していますが、「2入力インバータ」とは呼ばれていません。分析を通じて、この回路の論理関数が何であるか、それに対応してそれが何として指定されるべきかを発見します。

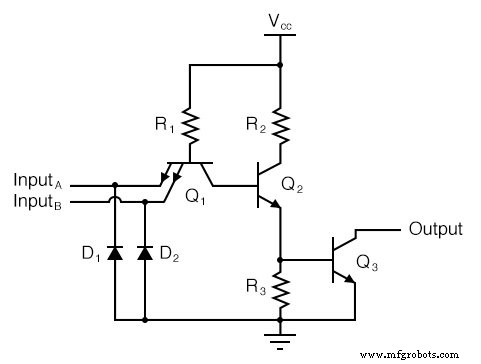

インバーターとバッファーの場合と同様に、「Q1」とマークされた「ステアリング」ダイオードクラスターは、増幅能力で使用されていなくても、実際にはトランジスタのように形成されます。残念ながら、単純なNPNトランジスタ構造では、 3つをシミュレートするには不十分です。 このダイオードネットワークにはPN接合が必要なので、別のトランジスタ(および記号)が必要です。

このトランジスタには、コレクタが1つ、ベースが1つ、 2つあります。 エミッター、そして回路では、次のようになります:

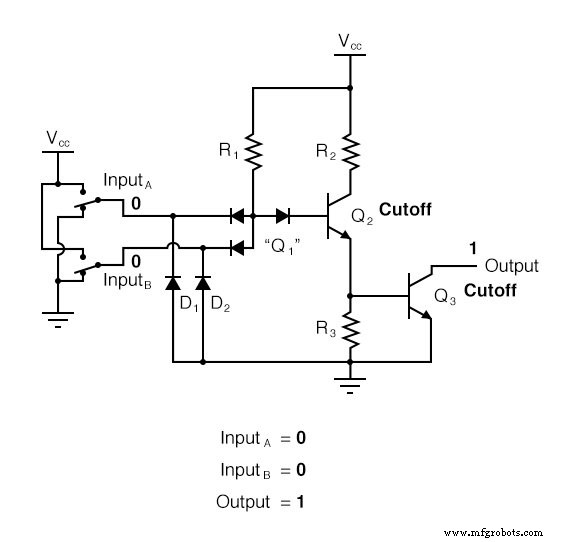

単一入力(インバータ)回路では、入力を接地すると、「ハイ」(1)状態を想定した出力が得られました。オープンコレクタ出力構成の場合、この「高」状態は単に「フローティング」でした。

入力をフロートさせる(またはVccに接続する)と、出力が接地され、「ロー」または0状態になります。したがって、1の結果は0の結果になり、その逆も同様です。

入力状態の回路図

この回路は単純なインバータ回路に非常に似ているため、トランジスタQ2のベースに同じ方法で接続された2番目の入力端子だけが異なり、各入力は出力に同じ影響を与えると言えます。

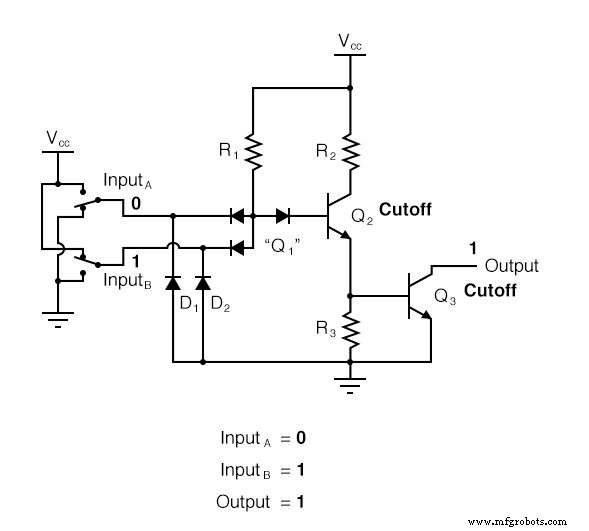

つまり、入力のいずれかが接地されている場合、トランジスタQ2は強制的にカットオフ状態になり、Q3がオフになり、出力がフローティングになります(出力は「ハイ」になります)。次の一連の図は、3つの入力状態(00、01、および10)についてこれを示しています。

いずれの場合も、接地された(「低」)入力がある場合、出力はフローティング(「高」)であることが保証されます。逆に、出力が「ロー」になるのは、トランジスタQ3がオンになった場合のみです。つまり、トランジスタQ2をオン(飽和)にする必要があります。つまり、どちらの入力もR1電流をQ2のベースからそらすことはできません。

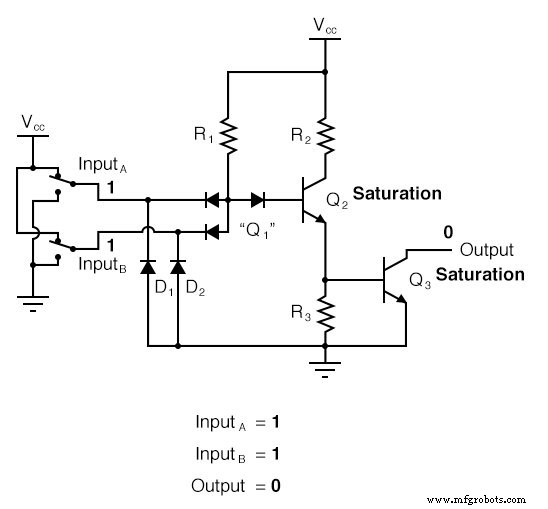

>この要件を満たす唯一の条件は、両方の入力が「高」の場合です(1):

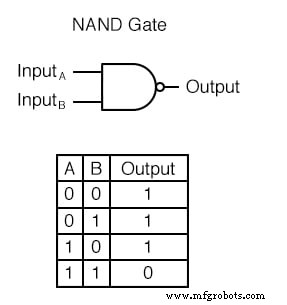

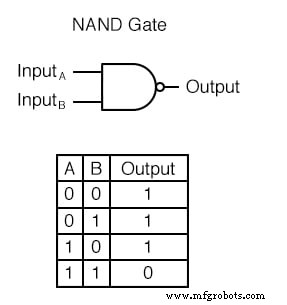

NANDゲート

これらの結果を収集して真理値表にまとめると、パターンがNANDゲートのパターンと一致していることがわかります。

NANDゲートに関する前のセクションで、このタイプのゲートは、ANDゲートを使用し、出力にインバーター(NOTゲート)を追加することで複雑さを増すことによって作成されました。ただし、この回路を調べると、NAND機能が実際にはこのTTL設計の最も単純で最も自然な動作モードであることがわかります。

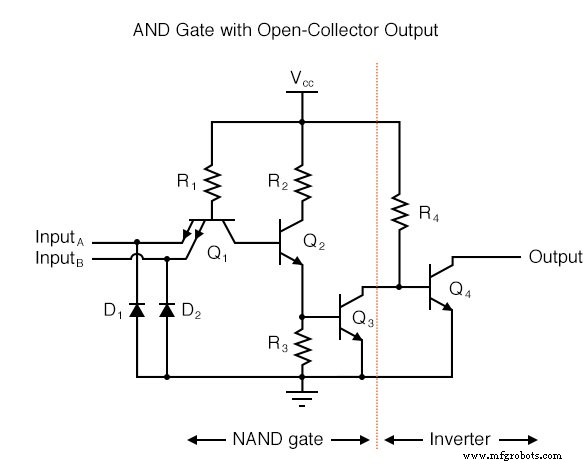

TTL回路を使用してAND関数を作成するには、増やす必要があります。 TTLインバータ回路にトランジスタステージを追加してバッファに変換する必要があるのと同じように、出力にインバータステージを追加することによるこの回路の複雑さ:

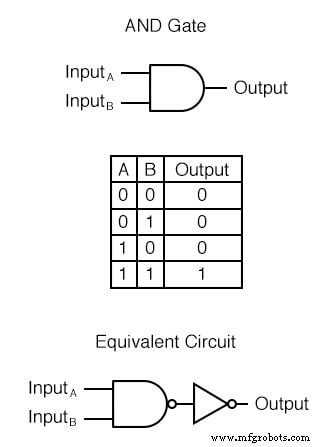

ANDゲート

真理値表と等価ゲート回路(逆出力NANDゲート)を次に示します。

もちろん、NANDとANDの両方のゲート回路は、オープンコレクタではなくトーテムポール出力段を使用して設計できます。わかりやすくするために、オープンコレクターバージョンを表示することにしました。

レビュー:

- TTL NANDゲートは、TTLインバータ回路を使用して別の入力を追加することで作成できます。

- ANDゲートは、NANDゲート回路の出力にインバータステージを追加することで作成できます。

関連ワークシート:

-

TTLロジックゲートワークシート

産業技術