トラッキングADC

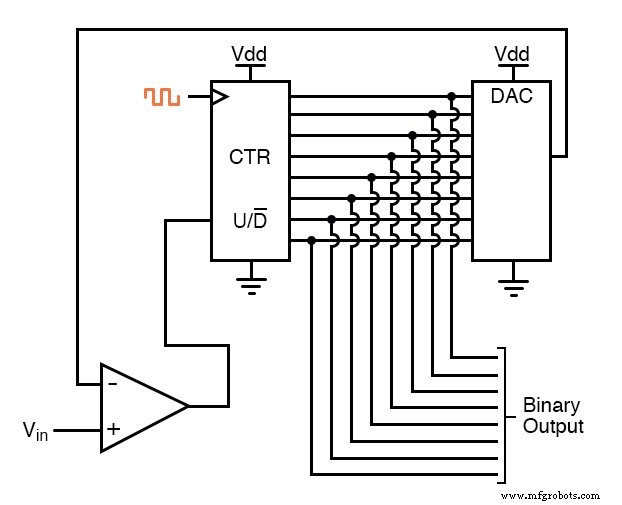

カウンターDACベースのコンバーターテーマの3番目のバリエーションは、私の推定では、最もエレガントです。 DACを駆動する通常の「アップ」カウンターの代わりに、この回路はアップ/ダウンカウンターを使用します。

カウンタは連続的にクロックされ、アップ/ダウン制御ラインはコンパレータの出力によって駆動されます。したがって、アナログ入力信号がDAC出力を超えると、カウンタは「カウントアップ」モードになります。

DAC出力がアナログ入力を超えると、カウンタは「カウントダウン」モードに切り替わります。いずれにせよ、DAC出力は常に追跡するための適切な方向にカウントされます 入力信号。

サイクルの終わりにバイナリカウントをバッファリングするためにシフトレジスタが必要ないことに注意してください。カウンタの出力は(入力を満たすためにカウントしてからゼロにリセットするのではなく)継続的に入力を追跡するため、バイナリ出力はクロックパルスごとに合法的に更新されます。

このコンバータ回路の利点は、カウンタをリセットする必要がないため、速度です。この回路の動作に注意してください:

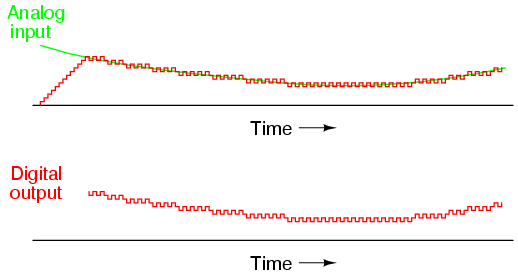

他の「カウント」ADC回路よりもはるかに速い更新時間に注意してください。また、カウンターがアナログ信号に「追いつく」必要があったプロットの最初の部分で、出力の変化率が最初のカウントADCの変化率と同じであったことにも注意してください。

また、この回路にシフトレジスタがない場合、バイナリ出力は、カウンタおよび逐次比較ADC回路の場合のように、ゼロから正確なカウントにジャンプするのではなく、実際にランプアップします。

おそらく、このADC設計の最大の欠点は、バイナリ出力が決して安定しないという事実です。完全に安定したアナログ入力信号であっても、クロックパルスごとに常にカウントを切り替えます。この現象は、非公式にビットボブルとして知られています。 、および一部のデジタルシステムでは問題になる可能性があります。

ただし、この傾向は、シフトレジスタを創造的に使用することで克服できます。たとえば、カウンタの出力は、出力が2ステップ以上変化した場合にのみ、パラレルイン/パラレルアウトシフトレジスタを介してラッチされる場合があります。同じ方向で2つ以上の連続したカウントを検出する回路を構築するには、少し工夫が必要ですが、努力する価値があります。

関連ワークシート:

- アナログ-デジタル変換ワークシート

産業技術