逐次比較型ADC

デジタルランプADCの欠点に対処する1つの方法は、いわゆる連続近似です。 ADC。この設計の唯一の変更点は、逐次比較レジスタとして知られる非常に特殊なカウンタ回路です。 。

このレジスタは、バイナリシーケンスでカウントアップする代わりに、最上位ビットで始まり最下位ビットで終わるビットのすべての値を試行することによってカウントします。カウントプロセス全体を通じて、レジスタはコンパレータの出力を監視して、バイナリカウントがアナログ信号入力よりも小さいか大きいかを確認し、それに応じてビット値を調整します。

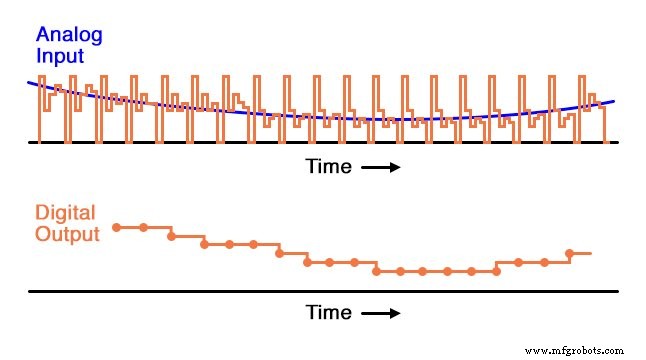

レジスタのカウント方法は、10進数から2進数への変換の「トライアルアンドフィット」方式と同じです。これにより、MSBからLSBまでさまざまなビット値が試行され、元の10進数と等しい2進数が取得されます。このカウント戦略の利点は、結果がはるかに速いことです。DAC出力は、通常のカウンターの0からフルカウントシーケンスよりもはるかに大きなステップでアナログ信号入力に収束します。

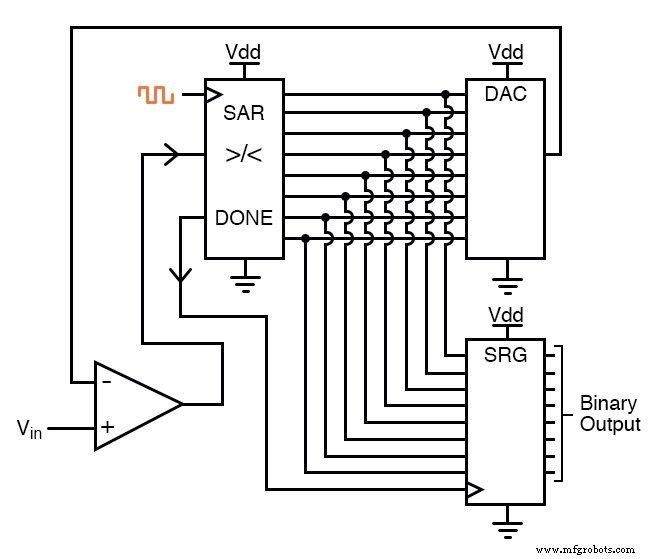

逐次比較レジスタ(SAR)の内部動作を示さない場合、回路は次のようになります。

SARは通常、2進数をシリアルで出力できることに注意してください。 (一度に1ビット)フォーマット。これにより、シフトレジスタが不要になります。時間の経過とともにプロットすると、逐次比較型ADCの動作は次のようになります。

デジタルランプADC回路とは異なり、このADCの更新が定期的に行われることに注意してください。

関連ワークシート:

- 逐次比較ADCワークシート

産業技術