スロープ(統合)ADC

これまでのところ、ADC回路の一部としてDACを使用することによってのみ、フラッシュコンバーターの膨大な量のコンポーネントから逃れることができました。ただし、これが唯一の選択肢ではありません。アナログランプ回路とデジタルカウンタを正確なタイミングで置き換えると、DACの使用を回避できます。

これは、いわゆるシングルスロープの背後にある基本的な考え方です。 、または統合 ADC。ランプ出力のDACを使用する代わりに、積分器と呼ばれるオペアンプ回路を使用します。 のこぎり波を生成し、コンパレータによってアナログ入力と比較されます。

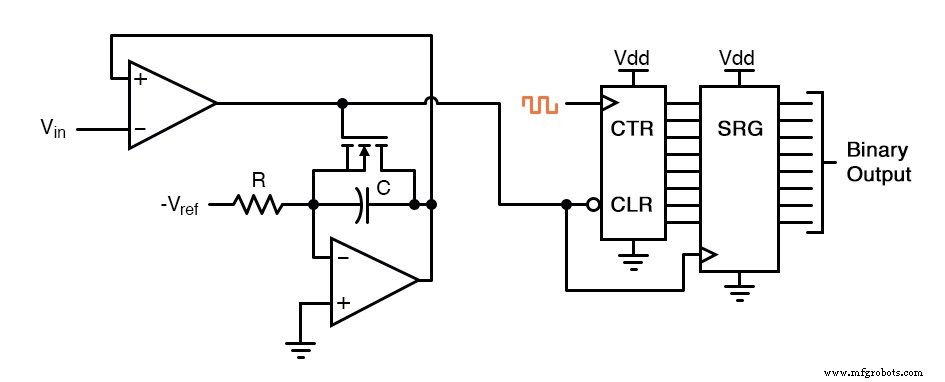

鋸歯状波形が入力信号電圧レベルを超えるのにかかる時間は、正確な周波数の方形波(通常は水晶発振器から)でクロックされるデジタルカウンターによって測定されます。基本的な概略図を次に示します:

ここに示されているIGFETコンデンサ-放電トランジスタ方式は、少し単純化されています。実際には、コンパレータの出力がハイになったときにコンデンサを完全に放電するために、クロック信号のタイミングでラッチ回路をIGFETゲートに接続する必要があります。

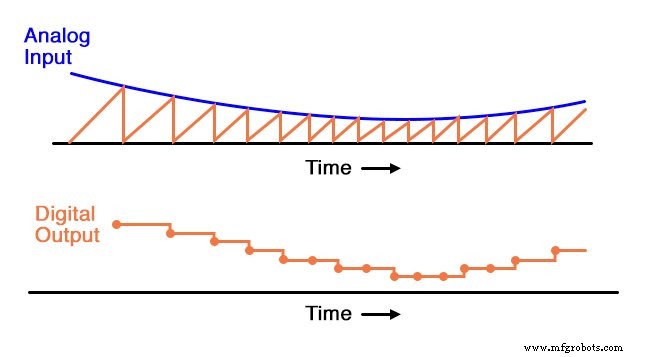

ただし、基本的な考え方はこの図から明らかです。コンパレータの出力が低い場合(入力電圧が積分器の出力よりも大きい場合)、積分器はコンデンサを線形に充電することができます。その間、カウンターは高精度クロック周波数で固定された速度でカウントアップしています。

コンデンサが入力と同じ電圧レベルまで充電されるのにかかる時間は、入力信号レベルと-V ref の組み合わせによって異なります。 、R、およびC。コンデンサがその電圧レベルに達すると、コンパレータ出力がハイになり、カウンタの出力をシフトレジスタにロードして最終出力にします。

IGFETは、コンパレータの高出力によって「オン」にトリガーされ、コンデンサをゼロボルトに放電します。積分器の出力電圧がゼロに低下すると、コンパレータの出力がロー状態に戻り、カウンタがクリアされ、積分器が電圧を再び上昇できるようになります。

このADC回路は、コンパレータの基準電圧が「階段」ではなく滑らかなのこぎり波であることを除けば、デジタルランプADCと非常によく似ています。

シングルスロープADCには、デジタルランプADCのすべての欠点があり、キャリブレーションドリフトの欠点もあります。 。このADCの出力とその入力の正確な対応は、カウンタのカウントレート(クロック周波数)に一致する積分器の電圧スロープに依存します。

デジタルランプADCでは、クロック周波数は変換精度に影響を与えず、更新時間にのみ影響を与えました。この回路では、積分率とカウント率が互いに独立しているため、経年変化によるばらつきが避けられず、精度が低下します。

この回路について言える唯一の良い点は、DACの使用を回避し、回路の複雑さを軽減することです。

デュアルスロープコンバーター

このキャリブレーションドリフトのジレンマに対する答えは、デュアルスロープと呼ばれる設計バリエーションにあります。 コンバータ。デュアルスロープコンバータでは、積分回路は、各サイクルの終わりに0ボルトにリセットされるのではなく、交互のサイクルで正と負に駆動されてランプダウンしてからアップします。

ランピングの一方向では、積分器は正のアナログ入力信号によって駆動されます(負の可変レートの出力電圧変化、または出力スロープ )高精度周波数時計付きのカウンターで測定された一定時間。次に、反対方向に、同じカウンターで測定された時間とともに、固定の基準電圧(出力電圧の変化の固定レートを生成)を使用します。

積分器の出力がサイクルの固定時間部分を開始したときと同じ電圧に達すると、カウンタはカウントを停止します。積分器のコンデンサが放電して元の出力電圧に戻るまでにかかる時間は、カウンタによって発生する大きさで測定され、ADC回路のデジタル出力になります。

デュアルスロープ法は、機械式時計機構で使用されるような回転ばねの観点からも同様に考えることができます。シャフトの回転速度を測定するメカニズムを構築していると想像してみてください。

したがって、シャフト速度は、このデバイスによって測定される「入力信号」です。測定サイクルは、ばねがリラックスした状態から始まります。

次に、スプリングは回転シャフト(入力信号)によって一定時間回転または「巻き上げ」られます。これにより、ばねはシャフト速度に比例した一定の張力になります。シャフト速度が大きいほど、巻き上げ速度が速くなり、その期間に蓄積されるばね張力が大きくなります。

その後、スプリングはシャフトから切り離され、一定の速度で巻き戻されます。これは、タイマーデバイスによって測定されたリラックス状態に戻るまでの時間です。 時間 その固定速度でばねがほどけるのにかかる時間は、速度に正比例します。 サイクルの固定時間部分で巻かれた場所(入力信号の大きさ)。

アナログからデジタルへの変換のこの技術は、積分器の積分係数(または「ゲイン」)とカウンターの速度の両方が「巻き取り」と「巻き戻し」全体で有効であるため、シングルスロープADCのキャリブレーションドリフトの問題を回避します。 」サイクル部分。カウンターのクロック速度が突然上昇した場合、これは積分器が「巻き上げ」られる固定期間を短縮します(その結果、積分器によって蓄積される電圧が少なくなります)が、それはまた、インテグレータが固定速度で「巻き戻し」を許可された時間。

カウンタがより速くカウントしている割合は、クロック速度が変更される前から積分器の累積電圧が減少するのと同じ割合になります。したがって、クロック速度エラーは自動的にキャンセルされ、デジタル出力は正確に本来あるべき状態になります。

この方法のもう1つの重要な利点は、サイクルの固定時間部分で積分器を駆動するときに入力信号が平均化されることです。その期間中のアナログ信号の変化は、そのサイクルの終わりにデジタル出力に累積的な影響を及ぼします。

他のADC戦略は、サイクルごとに1つの時点でアナログ信号レベルを「キャプチャ」するだけです。アナログ信号に「ノイズが多い」(かなりのレベルのスプリアス電圧スパイク/ディップが含まれている)場合、他のADCコンバータテクノロジーの1つは、単一の時点で信号を繰り返しキャプチャするため、スパイクまたはディップを変換することがあります。

>一方、デュアルスロープADCは、積分期間内のすべてのスパイクとディップを平均化するため、より優れたノイズ耐性を備えた出力を提供します。デュアルスロープADCは、高精度が要求されるアプリケーションで使用されます。

関連ワークシート:

- アナログ-デジタル変換ワークシート

産業技術