VHDL で信号ベクトルを作成する方法:std_logic_vector

std_logic_vector タイプは、VHDL で信号バスを作成するために使用できます。 std_logic は VHDL で最も一般的に使用される型であり、std_logic_vector はその配列バージョンです。

std_logic は、1 本のワイヤで運べる値をモデル化するのに最適ですが、コンポーネントに出入りするワイヤのコレクションを実装するのはあまり実用的ではありません。 std_logic_vector 複合型です。つまり、サブ要素のコレクションです。 std_logic_vector のシグナルまたは変数 type には任意の数の std_logic を含めることができます

このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。

std_logic_vector を宣言する構文 信号は:signal <name> : std_logic_vector(<lsb> to <msb>) := <initial_value>;

またはsignal <name> : std_logic_vector(<msb> downto <lsb>) := <initial_value>;

ここで <name> <initial_value> はシグナルの任意の名前です オプションの初期値です。 <lsb> は最下位ビットのインデックスで、<msb> 最上位ビットのインデックスです。

to または downto バスの範囲の方向、基本的にそのエンディアンを指定します。どちらも同様にうまく機能しますが、VHDL 設計者が downto を使用してベクトルを宣言するのが最も一般的です。 .したがって、常に downto を使用することをお勧めします 混乱を避けるためにビットベクトルを宣言するとき。

バイトを保持できるベクトル信号を宣言するための VHDL コード:signal MySlv : std_logic_vector(7 downto 0);

1 ビットを保持できるベクトル信号を宣言するための VHDL コード:signal MySlv : std_logic_vector(0 downto 0);

ゼロ ビット (空の範囲) を保持できるベクトル信号を宣言するための VHDL コード ):signal MySlv : std_logic_vector(-1 downto 0);

エクササイズ

このビデオ チュートリアルでは、std_logic_vector を宣言する方法を学びます。 シグナルを送信し、それらに初期値を与えます。また、For-Loop を使用してベクトル内のビットを反復処理し、シフト レジスタを作成する方法も学びます。 :

このチュートリアルで作成した最終的なコード:

library ieee;

use ieee.std_logic_1164.all;

entity T11_StdLogicVectorTb is

end entity;

architecture sim of T11_StdLogicVectorTb is

signal Slv1 : std_logic_vector(7 downto 0);

signal Slv2 : std_logic_vector(7 downto 0) := (others => '0');

signal Slv3 : std_logic_vector(7 downto 0) := (others => '1');

signal Slv4 : std_logic_vector(7 downto 0) := x"AA";

signal Slv5 : std_logic_vector(0 to 7) := "10101010";

signal Slv6 : std_logic_vector(7 downto 0) := "00000001";

begin

-- Shift register

process is

begin

wait for 10 ns;

for i in Slv6'left downto Slv6'right + 1 loop

Slv6(i) <= Slv6(i-1);

end loop;

Slv6(Slv6'right) <= Slv6(Slv6'left);

end process;

end architecture;

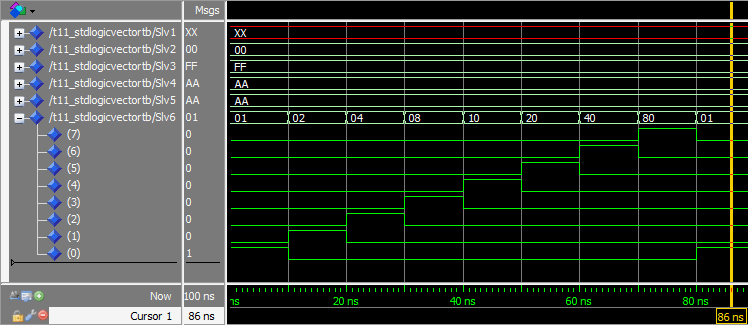

[実行] を押してタイムラインを拡大した後の ModelSim の波形ウィンドウ:

分析

この演習では、6 つの std_logic_vector を宣言しました バス、それぞれ 8 ビット長 (1 バイト)。

シグナル Slv1 初期値なしで宣言されました。波形のスクリーンショットでは、値が XX のバスが表示されます。これは、バスに表示される値が 16 進数であり、XX が非 16 進数であることを示しているためです。しかし、波形のバスを拡大すると、個々のビットが実際に U であることがわかりました。

信号 Slv2 すべて 0 の初期値を使用して宣言されました。各ビットの正確な値を指定する代わりに、(other => '0') を使用しました 初期値の代わりに。これは集計と呼ばれます 割り当て。重要な部分は、ベクター内のすべてのビットを、指定した長さに関係なく設定することです。

信号 Slv3 すべてのビットに 1 の初期値を与えるために集約代入を使用して宣言されました。波形でこの信号に FF が表示されていることがわかります。これは 8 つの 1 の 16 進数です。

信号 Slv4 16 進数 AA で指定された初期値で宣言されました。各 16 進数は 4 ビット長であるため、8 ビット長のベクトルに 2 桁 (AA) を指定する必要があります。

信号 Slv5 Slv4 とまったく同じ初期値を宣言します でしたが、ここではバイナリ値 10101010 として指定しました。波形から、両方の信号が 16 進値 AA を持っていることがわかります。

シグナル Slv6 '1' だった右端のビットを除いて、すべてゼロの初期値で宣言されました . シフト レジスタを作成するプロセスを使用しました この信号から。シフト レジスタは、名前が示すように、ベクトルの内容を 10 ナノ秒ごとに 1 桁左にシフトします。

このプロセスは 10 ns ごとにウェイクアップし、For ループはベクトル内のすべてのビットを 1 桁左にシフトします。最終ビットは Slv6(Slv6'right) <= Slv6(Slv6'left); によって最初のインデックスに戻されます 声明。波形では '1' を確認できます ベクトルを波及します。

これは、'1' がどのように機能するかを視覚化したものです。 シフト レジスタを介して伝播します。

'left' を使用して と 'right 属性、コードをより一般的なものにしました。 Sig6 の幅を変更すると 、プロセスは引き続き機能します。値をハードコーディングする代わりに、可能な場合は属性を使用することをお勧めします。

使用できる属性が他にもあるのではないかと思うかもしれません。これらは高度な VHDL 機能であると考えているため、このチュートリアル シリーズでは詳しく説明しません。

テイクアウト

- N ビットのベクトルは、

std_logic_vector(N-1 downto 0)を使用して宣言する必要があります - ベクトルは全体として割り当てることも、ベクトル内のビットに個別にアクセスすることもできます

- 集約割り当て

(others => '0')を使用して、ベクトル内のすべてのビットをゼロにすることができます 'leftのような属性を使用して、コードをより汎用的にすることができます と'right

基本的な VHDL クイズに答える – パート 2 »

または

次のチュートリアルに進む »

VHDL