最も一般的な VHDL タイプ std_logic の使用方法

VHDL で使用される最も一般的な型は std_logic です .このタイプは、1 本の物理的なワイヤで伝送されるデジタル情報である 1 ビットと考えてください。 std_logic integer よりも、デザインのリソースをよりきめ細かく制御できます。 これまでのチュートリアルで使用してきたタイプです。

通常、デジタル インターフェイスのワイヤには '1' のいずれかの値が必要です。 または '0' .これらの 2 つの値は、ビット (2 進数) が持つことができる唯一の値です。しかし実際には、物理的なデジタル信号はさまざまな状態になる可能性があり、std_logic type はエミュレートするのに適しています。したがって、VHDL で最も頻繁に使用されるタイプです。

このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。

std_logic type には次の値を指定できます:

| '1' | ロジック 1 |

| 「0」 | ロジック 0 |

| 「Z」 | 高インピーダンス |

| 「W」 | 信号が弱く、0 か 1 かわかりません |

| 「L」 | 弱い 0、プルダウン |

| 「H」 | ウィーク 1、プルアップ |

| '-' | どうでもいい |

| 「う」 | 未初期化 |

| 「X」 | 不明、複数のドライバー |

これは、単一のバイナリ値をモデル化することになっている型のさまざまな状態のように見えるかもしれません。このチュートリアル シリーズでは、これらすべての型を使用するわけではありません。 '1' を使用します と '0' もちろん。また、'U' も表示されます。 および 'X' これは、設計のエラーを見つけるのに役立ちます。その他の値は高度な VHDL 機能で、たとえば I

2

との通信のモデリングなどに使用できます。 C デバイス、またはトライステート バスの作成用。

複数のプロセスがシグナルに異なる値を書き込もうとしている場合、複数のドライバーがあると言います。 . std_logic の場合 signal には複数のドライバーがありますが、少なくともシミュレーターでは、コンパイル エラーや実行時エラーにはなりません。それは std_logic のためです 解決された型です 、つまり、その値は解決関数によって決定されます。

std_logic の値 2 つのドライバを持つ信号は、この解像度テーブルに基づいて決定されます:

| U | X | 0 | 1 | Z | W | L | H | – | |

|---|---|---|---|---|---|---|---|---|---|

| U | X | X | 1 | 1 | 1 | 1 | 1 | X | 1 |

| U | X | 0 | X | 0 | 0 | 0 | 0 | X | 0 |

| U | U | U | U | U | U | U | U | U | U |

| U | X | X | X | X | X | X | X | X | X |

| U | X | 0 | 1 | Z | W | L | H | X | Z |

| U | X | 0 | 1 | W | W | W | W | X | W |

| U | X | 0 | 1 | L | W | L | W | X | L |

| U | X | 0 | 1 | H | W | W | H | X | H |

| U | X | X | X | X | X | X | X | X | – |

エクササイズ

このビデオ チュートリアルでは、declare と show std_logic の使用方法を学習します。 波形のシグナル:

このチュートリアルで作成した最終的なコード:

library ieee;

use ieee.std_logic_1164.all;

entity T10_StdLogicTb is

end entity;

architecture sim of T10_StdLogicTb is

signal Signal1 : std_logic := '0';

signal Signal2 : std_logic;

signal Signal3 : std_logic;

begin

process is

begin

wait for 10 ns;

Signal1 <= not Signal1;

end process;

-- Driver A

process is

begin

Signal2 <= 'Z';

Signal3 <= '0';

wait;

end process;

-- Driver B

process(Signal1) is

begin

if Signal1 = '0' then

Signal2 <= 'Z';

Signal3 <= 'Z';

else

Signal2 <= '1';

Signal3 <= '1';

end if;

end process;

end architecture;

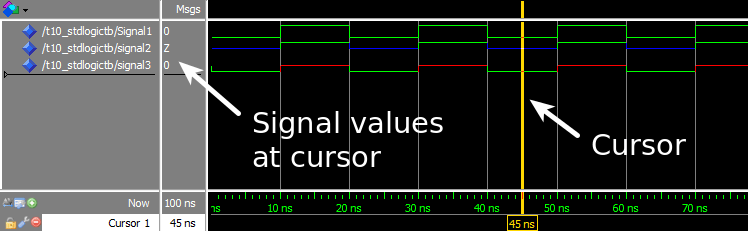

[実行] を押してタイムラインを拡大した後の ModelSim の波形ウィンドウ:

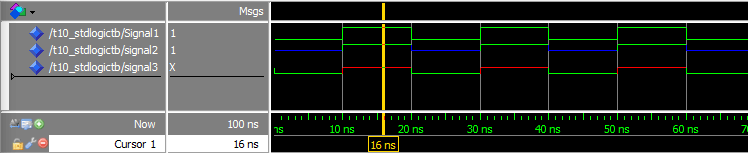

繰り返し信号サイクルの他の部分にカーソルを置いた波形:

分析

この演習では、VHDL の解決機能が std_logic でどのように機能するかを示しました。 タイプ。デジタル ロジックを使用する場合、多くの場合、波形でタイムラインを調べる方が実用的です。 プリントアウトを使用するのではなく。したがって、この演習では ModelSim 波形を使用して信号値を確認しました。

最初のプロセスと Signal1 3 番目のプロセスが Signal2 で駆動している値を変更するためにのみ使用されます そして Signal3 .

2 番目のプロセスである Driver A は、'Z' を駆動しようとします。 Signal2 に 、および '0' Signal3 に

3 番目のプロセスであるドライバー B は、'1' を交互に駆動します。 と 'Z' Signal2 の両方に と Signal3 .

Signal1 という波形のスクリーンショットが表示されます '0' の間で変化しています と '1' これは、このシグナルを駆動しようとしているプロセスが 1 つしかないためです。また、VHDL コードのコメントに掲載されている解決表に従って、複数のドライバー信号が解決されていることもわかります。

| シグナル | ドライバーA | ドライバーB | 結果 |

|---|---|---|---|

| シグナル2 | 「Z」 | 「Z」 | 「Z」 |

| シグナル2 | 「Z」 | 「1」 | 「1」 |

| シグナル3 | 「0」 | 「Z」 | 「0」 |

| シグナル3 | 「0」 | 「1」 | 「X」 |

テイクアウト

std_logicVHDL で単一ビット値を保持するために使用される最も一般的な型ですstd_logicを考えてみてください デジタル設計の物理的なワイヤーとしての信号- 複数のプロセスが

std_logicを駆動しようとした場合 信号、その値は解決テーブルによって決定されます

次のチュートリアルに進む »

VHDL