非同期リセットの同期と配布–ASICとFPGA

非同期リセットと同期ロジッククロック間の調整が不足していると、電源投入時に断続的に障害が発生します。この一連の記事では、非同期リセットの要件と課題について説明し、ASICとFPGAの設計の高度なソリューションを探ります。

非同期リセットは、電源投入後に同期回路を既知の状態にするために、VLSI設計で従来から採用されています。非同期リセットリリース操作は、リセットとクロック間の競合の可能性による同期の失敗を排除するために、同期ロジッククロック信号と調整する必要があります。このような調整が不足していると、電源投入時に断続的に障害が発生します。大規模なマルチクロックドメイン設計を検討すると、問題が悪化します。同期の問題に加えて、数百万のフリップフロップへの非同期リセットの配布は困難であり、CTS(Clock Tree Synthesis)と同様の技術が必要であり、同様のエリアとルーティングリソースが必要です。

非同期リセットの要件と課題を、同期と配布の問題に焦点を当てて確認します。リセット同期(リセットツリーソース同期)および配布(リセットツリー合成)の従来のソリューションの欠点について説明します。より高速で単純なタイミングコンバージェンスとより信頼性の高いリセット同期および分散のための高度なソリューションが提示されます。 ASIC設計とFPGA設計のさまざまなアプローチについて詳しく説明します。

パート1では、非同期リセットを取り巻く問題について説明し、それらの問題を解決するためのアプローチの概要を説明します。パート2(この記事)では、ASICおよびFPGAでの正しい非同期リセットの追加ソリューションについて説明します。いくつかの有用な特殊なケースについては、パート3で説明します。

2。非同期リセットタイミングコンバージェンス手法

パート1で説明した主な問題の1つは、特に短いクロックサイクルが採用されている場合の、大規模な設計(高遅延のリセット配布ネットワークを使用)のリセットリリースの複雑さでした。標準のSTA最適化に基づくタイミング収束は、高価な設計につながり、場合によっては不可能ですらあります。ここでは、このタイミングの問題を軽減する2つの手法について説明します。どちらの手法もASICとFPGAの設計に適用できます。

2.1。非同期リセットパイプライン

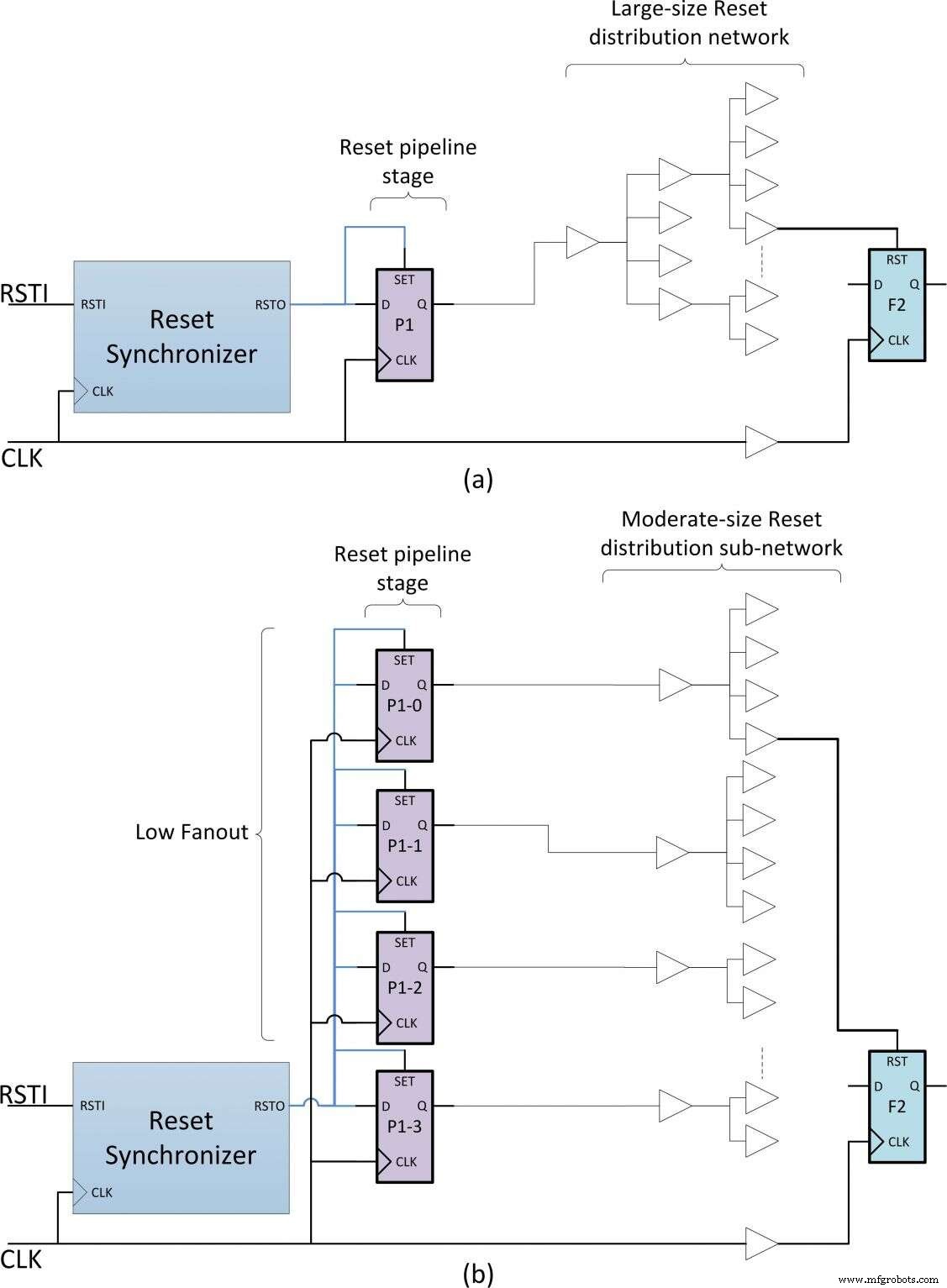

非同期リセットリリースのタイミングの問題に対処する1つの方法は、リセットリリースの待ち時間をよりリラックスしたタイミングとトレードオフすることです。これは、次の方法でリセットツリーをパイプライン化することで実現できます。各シンクロナイザーの後に、追加の非同期セットフリップフロップステージP1がリセットラインに含まれます(図6a)。フリップフロップのSET入力とD入力の両方が、リセットシンクロナイザーからのアクティブハイリセットRSTOに接続されています。 RSTOリリースでは、通常の同期パスとして制約されているため、P1DおよびSET入力のセットアップおよびホールド条件が満たされます。

クリックして大きな画像を表示

図6:パイプラインを使用した非同期リセット(出典:vSync Circuits)

新しいスキームの機能的な動作は、リセットリリースでの追加のシングルサイクルレイテンシを除いて、パート1(図3d)で説明されている通常のスキームと同様です。この手法で発生するリセットレイテンシは、電源投入ごとに1回だけ発生するため、通常、ほとんどのアプリケーションで許容されます。

この手法の補足部分は、設計上の制約をカバーしています。パート1で説明したように、再収束パスの問題を防ぐために、シンクロナイザーフリップフロップは重複に対して制約を受ける必要がありますが、パイプラインステージP1はMAX_FANOUT制約の対象となります。最大ファンアウト制約の例を図6bに示します。 P1フリップフロップは自動的に 合成ツールによって複製され、リセット配布用の4つのサブネットワークが作成されます。各サブネットワークの遅延は元のネットワークよりも低く、リセットリリースのタイミング要件を満たしています。さらに、リセットシンクロナイザーの出力は8つのファンアウトに簡単に適合します。

この非同期リセットパイプライン技術は、任意の設計サイズに拡張可能であり、設計が変更されても変更する必要はありません。合成ツールは自動的にP1ステージを複製し、中程度の遅延のリセットサブネットを制限します。シンクロナイザー出力用に複製されたP1ステージのファンアウトは通常小さく、タイミング違反を引き起こしません。ただし、単一のパイプラインステージでタイミングが収束しない場合は、追加のパイプラインステージP2 – PNを含めて、さまざまなMAX_FANOUT制約で制約することができます。

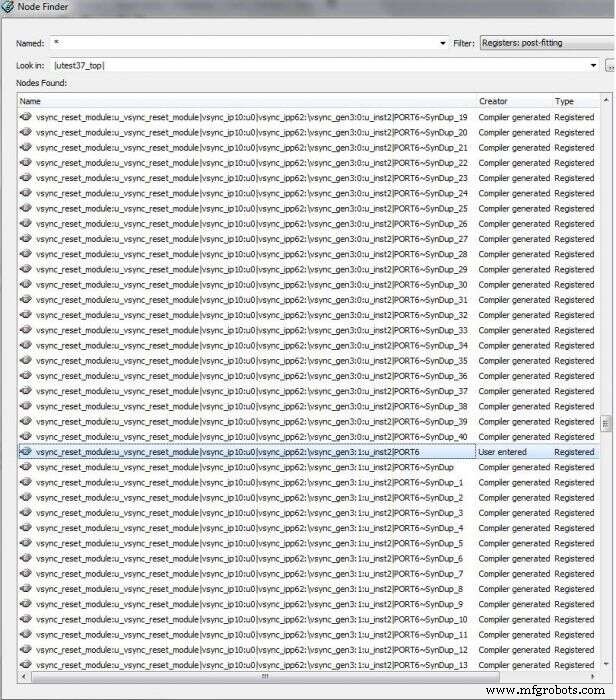

実際のデザインに適用されるこの手法の例を図7に示します。PORT6という名前のP1ステージレジスタは、MAX_FANOUT制約を満たすために、合成ツール[6]によって約40回自動的に複製されました。 40のサブネットのそれぞれが、ローカルファンアウトのタイミングを満たしていました。

クリックして大きな画像を表示

図7:非同期リセットパイプラインの例(出典:vSync Circuits)

埋め込み

- C ++の構造とクラス

- メールボックス:紹介と基本的なサービス

- セマフォ:紹介と基本的なサービス

- Anvo-SystemsとMouserが販売契約に署名

- MouserとInventekSystemsがグローバル販売契約を発表

- RutronikとAPMemoryがグローバル販売契約に署名

- アルビスプラスチックスは流通および調合事業を分離しました

- 流通サイト選択の芸術と科学

- 倉庫保管と流通における排出量を削減する6つの方法

- RG Groupは、AutoGuideMobileRobotsとの流通および統合パートナーシップに同意します

- 20製造ブログすべての製造、サプライチェーン、流通、およびロジスティクスの専門家が読む必要があります