Ta2O5 / TaOx二層構造による導電性ブリッジランダムアクセスメモリのフィラメント過成長の抑制

要約

導電性ブリッジランダムアクセスメモリ(CBRAM)の信頼性を向上させるために、2層構造が広く採用されています。この作業では、Ta 2 を実現するための便利で経済的なソリューションを提案しました。 O 5 / TaO x 低温焼鈍法による二層構造。 TaO x の追加 層は、セットプログラミング中のオーバーフロー電流を抑制する外部抵抗として機能し、自己コンプライアンススイッチングを実現しました。その結果、オーバーセット現象の抑制により、高抵抗状態と低抵抗状態の分布が改善されます。さらに、スイッチング膜の欠陥が回復するため、CBRAMのLRS保持が明らかに向上します。この作業は、CBRAMの信頼性を向上させるための簡単で経済的な方法を提供します。

はじめに

導電性ブリッジ抵抗スイッチングメモリ(CBRAM)は画期的な技術であり、その高いスケーラビリティ、シンプルな構造、3D統合の容易さ、および高速動作により、次世代の不揮発性メモリ(NVM)と見なされています[1,2、 3]。実際のアプリケーションでは、データの保持や耐久性などの信頼性の問題が、これらのメモリデバイスのメモリ市場への確実な導入を妨げています。構造工学は、CBRAMの信頼性を向上させるための最も一般的なアプローチです[4、5、6、7]。趙らナノポアグラフェン層によるCBRAM性能を強化するための閉じ込められた陽イオン注入[8]。デバイスの信頼性は大幅に向上していますが、材料制御にコストがかかり、標準のCMOSプロセスでは使用できません。この問題に対処するために、Gong etal。低抵抗状態(LRS)の保持を改善するためにCu電極にCuSiN界面層を形成するためのCMOS互換で自己整合の方法を提案しました[9]。 Cao etal。ナノフィラメントの過成長現象と負のSET動作を排除することにより、CBRAMデバイスのデバイスの信頼性を向上させるTiNバリア層を提案しました[10]。上記の方法は、CBRAMの信頼性を効果的に最適化するために2層構造を利用しました。ただし、複雑なプロセスフローやプログラミング速度のコストがかかります。

この作業では、単純な低温アニーリングプロセスによって2層デバイスを形成するCMOS互換の方法を提案します。 Ta 2 の2層デバイス O 5 / TaO x 構造は自発的に形成され、アニールされていないデバイスと比較してより優れた信頼性特性を示しています。アニールされたデバイスの信頼性の向上は、プログラミング中に粒界に沿って形成されたフィラメントの集中によって説明できます。さらに、二層アニーリングデバイスの場合、TaO x が存在するため 、TaO x により、自己コンプライアンス動作が実現されます。 層は、Ta 2 と直列の抵抗として機能します O 5 -抵抗層。この結果は、2層デバイスを形成し、CBRAMの信頼性を向上させるための単純なCMOS互換の方法を提供します。

メソッド

CMP後の直径1μmのWプラグが下部電極(BE)として機能します。 DCマグネトロンスパッタリングにより5nmのTa層を堆積させた後、Ta 2 O 5 プラズマO 2 中で、350°C未満の熱酸化プロセスによって形成されました。 プラズマ化学気相成長法(PECVD)による300秒間。次に、40 nmのCu上部電極(TE)がスパッタされ、リソグラフィによってパターン化されます。メモリセルは、SF 6 の混合ガスを使用したエッチングプロセスによってパターン化されます。 およびC 3 F 8 TEをハードマスクとして使用します。その後、BEはAlパッドによって抽出されます。最後に、デバイスは、400°Cで30分間のCMOS互換の低温アニーリングプロセスで完成します。デバイスのサイズは、1μm 2 である下部電極の面積によって定義されます。 。参考までに、アニーリングプロセスのないデバイスも用意されています。電気的DC測定は、Keithley4200-SCS半導体パラメータアナライザを使用して実行されます。すべての測定で、電圧はWBEが接地された状態でCuTEに印加されます。

結果と考察

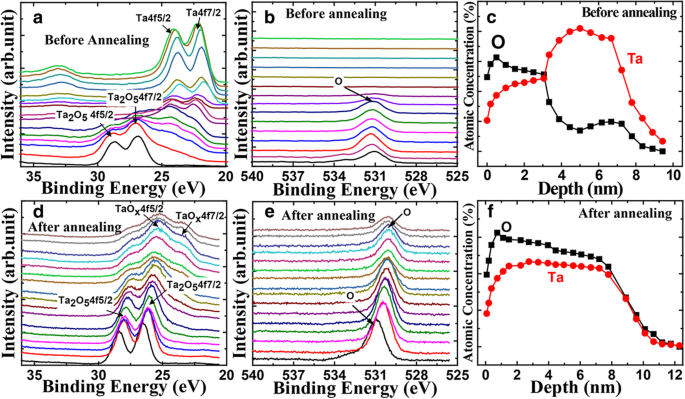

アニーリングプロセス、Ta 2 の組成と化学結合状態についての深い洞察を得るには、 O 5 アニーリングプロセスの前後のフィルムは、X線光電子分光法(XPS)によって分析されます。サンプルのエッチング速度は0.5nm /ポイントです。図1aでは、Ta 2 のピーク O 5 26.70 eVのピーク結合エネルギーを持つ4fダブレット(Ta 2 O 5 4f 7/2 )および28.60 eV(Ta 2 O 5 4f 5/2 )1.9eVのピーク分離が表面で観察されます[11、12、13]。このケースは、Ta 2 の存在を示しています O 5 レイヤー。

XPSは、前のTaの深度プロファイルを示しています( a )およびその後( d )アニーリング。 b 、 e それぞれアニーリング前後のOの深さプロファイル。 c、f アニーリング前後の深さのあるOとTaの原子濃度プロファイル

深さが増すにつれて、Ta 2 のピーク O 5 4fダブレットが消え、22.33 eV、23.96eVにピークがあります。これはTa4f 7/2 に対応します。 、Ta 4f 5/2 現れる。図1bは、Ta 4f 7/2 と同じ深さにO信号がないことを確認しています。 およびTa4f 5/2 存在。つまり、Ta 2 の表面に金属のTaがあります。 O 5 アニールされていないデバイスの場合。 Ta 2 の深さ O 5 図1cから分析されたTaとTaは、それぞれ4nmと2.5nmです。また、深さ7nmにO原子濃度のピークがあり、吸収された酸素の存在を示しています。図1dとeは、Ta 2 からのXPSスペクトルの深度プロファイルを示しています。 O 5 アニーリングプロセス後のフィルム。 Ta4fダブレットとTa 2 のピーク O 5 4fダブレットは特定の深さで一緒に存在します。 Ta 5+ の強度 酸化状態は、深さが増すにつれて徐々に弱まります。フィルムの深さに沿った全方位の酸素信号と組み合わせて、TaO x Ta 2 の表面に存在します O 5 [11、14]。図1fから計算すると、Ta 2 の厚さ O 5 は4nmでTaO x 3.5nmです。したがって、TaO x は、アニーリングプロセスで吸着酸素を格子酸素に変化させることによって形成されます。酸素の再分配は、アニーリングプロセス後に飽和した飽和点に達します。 TaOxの厚さおよび成形電圧は、アニーリング時間が増加しても増加せず、このアニーリングプロセスの大きなプロセスマージンを証明します。

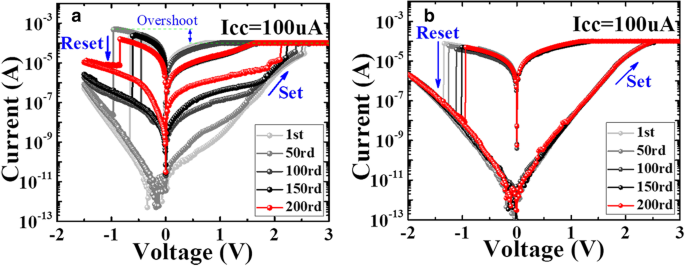

図2aとbは、Cu / Ta 2 の抵抗スイッチング特性です。 O 5 DCスイープモードでのアニーリング前後の/ W。初期抵抗( R 初期 )2つのデバイスのうち、両方とも高抵抗状態(HRS)で、値は〜10 9 です。 Ωおよび10 10 それぞれΩ。より高い R 初期 アニールされたデバイスの特性は、熱処理下で形成されたより厚い酸化膜によるものです。特に、このデバイスは、実際のアプリケーションで非常に期待される成形プロセスを必要としません。アニールされていないデバイスの場合、正の電圧掃引中に印加電圧が臨界値に達すると、突然LRSに切り替わります。設定プロセス中に超低LRSが発生しました。このような場合のRESET電流は、事前設定されたコンプライアンス電流よりもはるかに高く、このデバイスでオーバーシュート現象が発生したことを示しています。図3bは、アニールされていないデバイスの200サイクル以内の不安定なLRSとHRSを示しています。サイクルごとの大きな変動により、メモリウィンドウは20まで小さくなります。図2bは、アニーリングされたデバイスのスイッチング動作を示しています。セルを流れる電流は徐々に増加し、コンプライアンス電流に達します。明らかなスイッチングポイントは観察されず、アニールされていないデバイスで発生したオーバーシュート現象を回避します。最大10 4 のメモリウィンドウ HRSとLRSが均一に分布しているため、スイッチングサイクル中に達成されました。

アニーリング前のCu / TaOx / Wデバイスの典型的なI-V曲線( a )およびアニーリング後( b )200サイクル

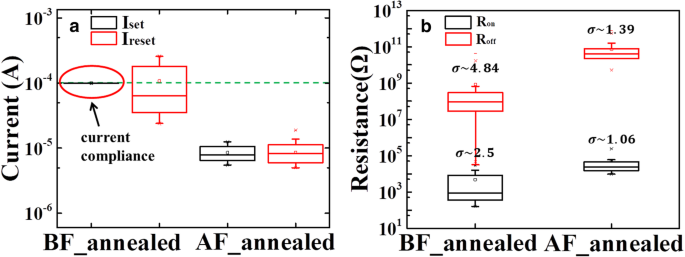

a アニーリング前後の電流分布をそれぞれ設定およびリセットします。 b アニーリング前後のHRSとLRSの抵抗分布

アニーリングされたデバイスのオーバーセット現象の抑制は、RESET電流の分布の改善によっても確認できます( I リセット )および電流を設定します( I セット )図3aに示すように、アニールされたデバイス内。 私 セット アニールされていないデバイスの一部が I でスタックしている CC しかし私 リセット 広く配布します。対照的に、アニールされたデバイスの場合、 I リセット I に似ています セット 。デバイス間の均一性は、 R を分析することによって評価されます。 on および R オフ DCモードの20の異なるデバイスで。図3(b)に示すように、 R on V で抽出 読む アニールされていないデバイスの0.1Vは、10 2 から分配されます。 Ωから10 5 Ω、 R on アニールされたデバイスの分布は10 4 Ωから10 5 Ω。比較的高い R on アニールされたデバイスの抵抗は、TaO x の直列抵抗に起因します。 層。さらに、アニールされたデバイスのHRS分布も大幅に改善されます。図3bに示すように、 R の標準偏差(SD) オフ 4.84から1.39に削減されます。

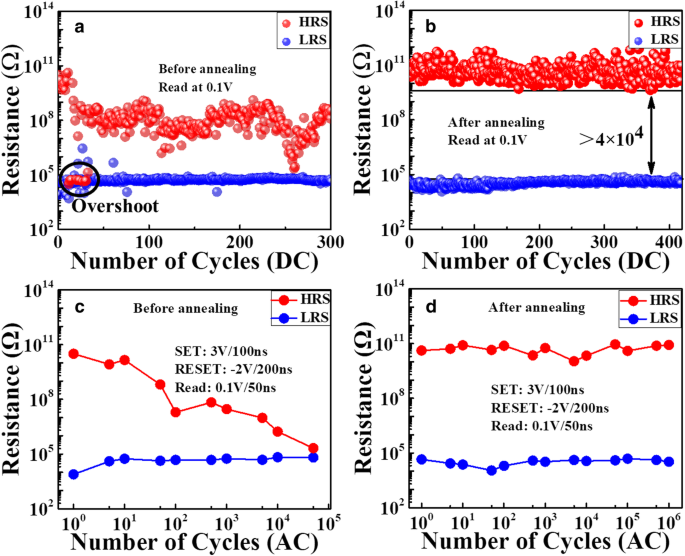

DCスイープでのサイクリング結果を図4aおよびbに示します。アニールされていないデバイスの場合、HRS / LRS比は約10 5 です。 最初は徐々に減少し、最後にLRSに固執します。サイクリング中に、HRS(赤い点)とLRS(青い点)がときどき前後に実行されるという形で、いくつかのソフトエラーが観察される可能性があることに注意してください。アニーリングされたデバイスの場合、HRS / LRS比は安定したままです(〜10 4 )劣化することなく。パルス測定中、適切なパルスプログラミング条件は、セット動作の場合は3 V / 100 ns、リセット動作の場合は− 2 V / 200 ns、読み取り動作の場合は0.1 V / 50nsとして最適化されます。セット/リセット/リード動作の検出時間は、それぞれ15 ns / 12 ns / 25nsです。図4cからわかるように、アニールされていないデバイスの耐久性は通常5×10 4 未満です。 スイッチングサイクル。ただし、図4dから、10 6 を超えても、アニールされたデバイスが障害なく正常に動作することは驚くべきことです。 スイッチングサイクル。私たちの以前の研究[15]に基づくと、CBRAMの耐久性の失敗は、対極へのフィラメントの過成長に起因する不安定なRESET動作に関連しています。一方では、生い茂ったフィラメントは破裂するためにより多くのエネルギーを必要とし、不完全なRESETとより低いHRSを引き起こす傾向があります。一方、対極へのフィラメントの過成長は、対極に残留Cuイオンをもたらし、これが金属イオンの貯蔵所として機能し、予期しない負のSETを引き起こす可能性があります。アニールされたデバイスの場合、フィラメントの過成長は、TaO x を組み込むことによって十分に抑制されます。 レイヤーを作成し、より安定したRESET操作を実現します。その結果、メモリウィンドウが適切に維持され、サイクリング特性が大幅に向上します。

a のサイクリング結果 300DCサイクルおよび b でのアニーリングなしのデバイス 400DCサイクル未満のアニーリングを備えたデバイス。 c、d 最適化された動作構成でのACモードでの耐久特性:3 V / 100nsに設定。リセット− 2 V / 200ns。最大10 6 アニーリング後のデバイスのサイクルが得られました

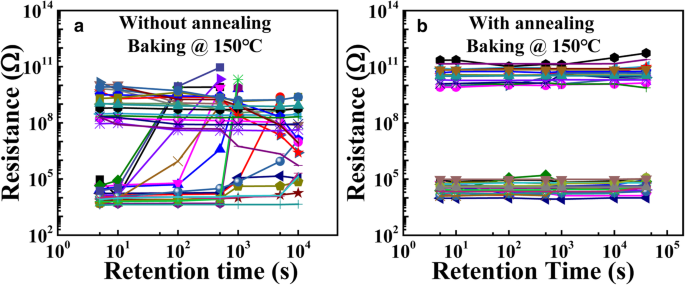

保持特性を考慮することは、CBRAMの実用化に重要な役割を果たします[16]。保持特性は、真空オーブンを使用して150°Cで測定されます。各セルの抵抗は、10年ごとに室温まで冷却した後にチェックされます。図5aおよびbは、R HRS の依存関係を示しています。 / R LRS それぞれ、アニーリングなしとアニーリングありのデバイスのベーキング時間について。アニールされていないデバイス(図5a)の場合、時間が長くなるにつれて、デバイスは10 4 以内に徐々に故障しました。 s。ただし、アニーリングされたデバイス(図5b)の場合、記録された20個のデバイスのうち、ベーキング時間が長くなっても、LRSとHRSの抵抗は低下しません。つまり、デバイスの保持は、アニーリングプロセスによって大幅に改善されます。 85°Cでのアニーリングされたデバイスの寿命は、アレニウスプロットによって10年と抽出できます。これは、報告されているCBRAM [17、18]とよく一致しています。アニーリングされたデバイスの保持特性が向上するのは、アニーリングプロセスによってスイッチング膜の欠陥が回復し、Cu種の拡散が遅くなるためです。

a のHRS / LRSの保持特性 アニールされていないデバイスと b 150°Cでアニールされたデバイス

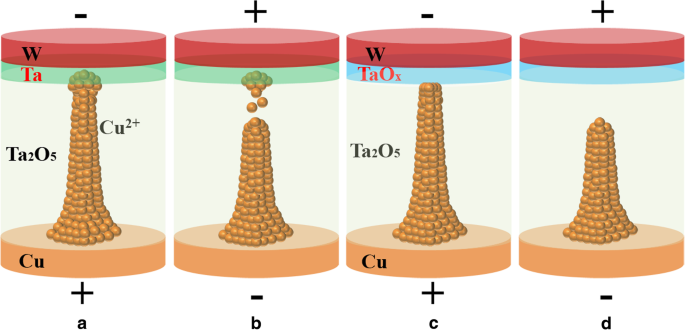

上記の結果に基づいて、アニールされたデバイスとアニールされていないデバイスのスイッチング動作の物理モデルを図6a〜dに示します。 CBRAMでのフィラメントの成長は、電解質の格子内でのCuイオンの輸送に関連しています[19]。アニールされていないデバイスで発生したオーバーシュート現象により、フィラメントが対極に過成長します。 RESET動作中、対極に蓄積された残留Cuイオンは、フィラメント先端と対極の間のトンネルギャップにドリフトし、残留Cu + になります。 RESET操作の終了時およびHRSの重大な変動。 TaO x におけるCuの拡散係数として (4.9×10 − 20 cm 2 / s)はTaよりもはるかに小さい(1.0×10 − 6 cm 2 / s)、CuはTaO x に拡散します Cu / Ta 2 のサンプルでは、集合動作中の電界下でははるかに困難です。 O 5 / TaO x / W [20、21]。したがって、オーバーセット動作とフィラメントの過成長を十分に抑制でき、RESET操作がより安定します。

アニールされたデバイスとアニールされていないデバイスのスイッチング動作の物理モデリング。 a 設定して b Cu / Ta 2 の構造を持つアニールされていないデバイスのRESETプロセス O 5 / Ta / W。 c 設定して d Cu / Ta 2 の構造を持つアニールされたデバイスのRESETプロセス O 5 / TaO x / W。フィラメントの異常成長は、TaO x によって抑制されます。 アニーリングプロセス中に形成された層

結論

この手紙では、TaO x のスイッチング特性を調査しました。 ベースのCBRAMデバイス。 Ta 2 O 5 / TaO x 二層スタックは、熱アニーリング後処理後に形成されました。 TaO x 層は、セット動作中のオーバーフロー電流を抑制する外部抵抗として機能する可能性があります。オーバーセット現象の抑制により、HRSとLRSの両方の分布が大幅に改善されます。さらに、熱アニーリング中にスイッチング膜の欠陥が回復するため、CBRAMのデータ保持が強化されます。この作業は、2層構造を実現し、CBRAMの信頼性を向上させるための最も便利で経済的なソリューションを提供します。

略語

- CBRAM:

-

導電性ブリッジランダムアクセスメモリ

- HRS:

-

高抵抗状態

- LRS:

-

低抵抗状態

- NVM:

-

不揮発性メモリ

- PECVD:

-

プラズマ化学気相成長法

- TE:

-

上部電極

ナノマテリアル

- 防衛グレードのFPGAが早期アクセスでデビュー

- Nano書記素、シリコンベースの柔軟な透明メモリ

- スタックカップカーボンナノファイバーの原子および電子構造を明らかにする

- 遷移金属をドープしたカオリナイトナノクレイの構造と電子特性

- 中空構造LiNb3O8光触媒の調製と光触媒性能

- 抵抗変化型メモリのモデリングとシミュレーションに関する集合的研究

- InSeナノリボンの電子構造とI-V特性

- 周期的ポテンシャルの下でのシリセンのスピンおよび谷に依存する電子構造

- 確率的空孔モデルによる接触抵抗変化型メモリの変動性の研究

- チタニアナノチューブの熱伝導率に及ぼす形態と結晶構造の影響

- セキュリティに関するリモートアクセスデバイスの調達に関する考慮事項