基本的なゲート機能

部品と材料

- 4011クワッドNANDゲート(Radio Shackカタログ番号276-2411)

- 8ポジションDIPスイッチ(Radio Shackカタログ番号275-1301)

- 10セグメント棒グラフLED(Radio Shackカタログ番号276-081)

- 6ボルトのバッテリー1個

- 2つの10kΩ抵抗器

- 3つの470Ω抵抗器

注意! 4011 ICはCMOSであるため、静電気に敏感です!

参考資料

電気回路の教訓 、第4巻、第3章:「論理ゲート」

学習目標

- 「プルダウン」抵抗の目的

- ゲートの真理値表を実験的に決定する方法

- 論理ゲートを相互に接続する方法

- NANDゲートを使用してさまざまな論理関数を作成する方法

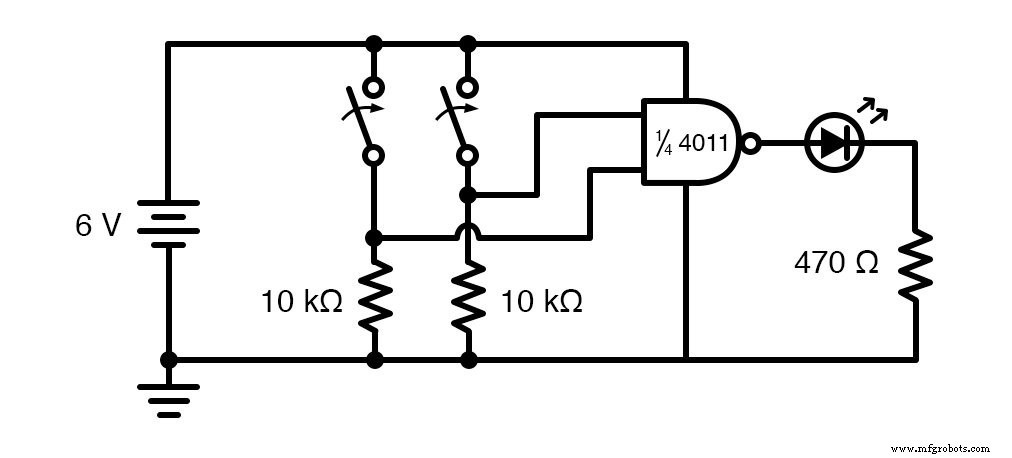

基本的なゲート関数の概略図

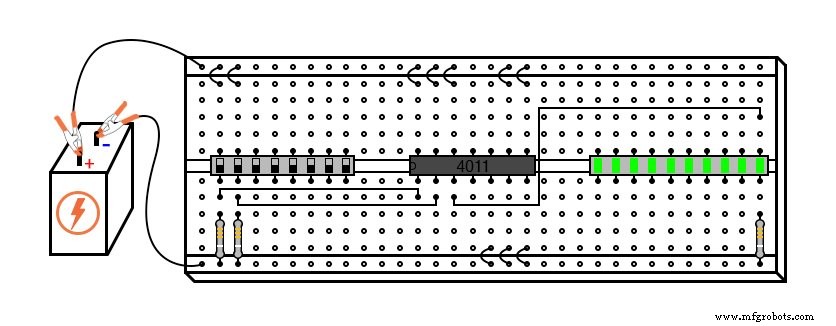

基本的なゲート機能の図

実験手順

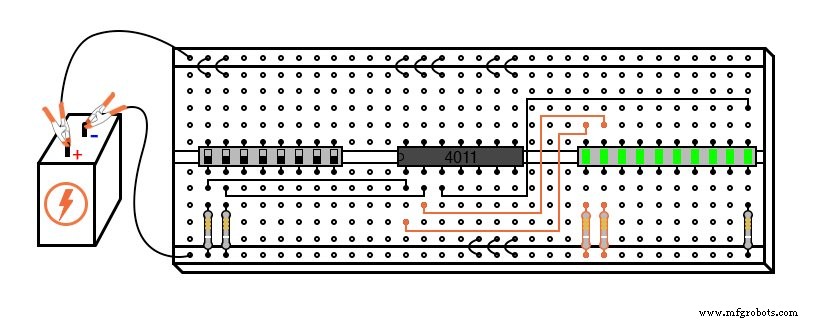

まず、図のように、1つのNANDゲートを2つの入力スイッチと1つのLEDに接続します。最初は、1つのNANDゲートの動作を示すために2つのスイッチと1つのLEDしか必要ないため、8ポジションスイッチと10セグメントLED棒グラフの使用は過剰に思えるかもしれません。ただし、これらの追加のスイッチとLEDが存在するため、回路を拡張するのに非常に便利であり、回路レイアウトをクリーンでコンパクトにするのに役立ちます。

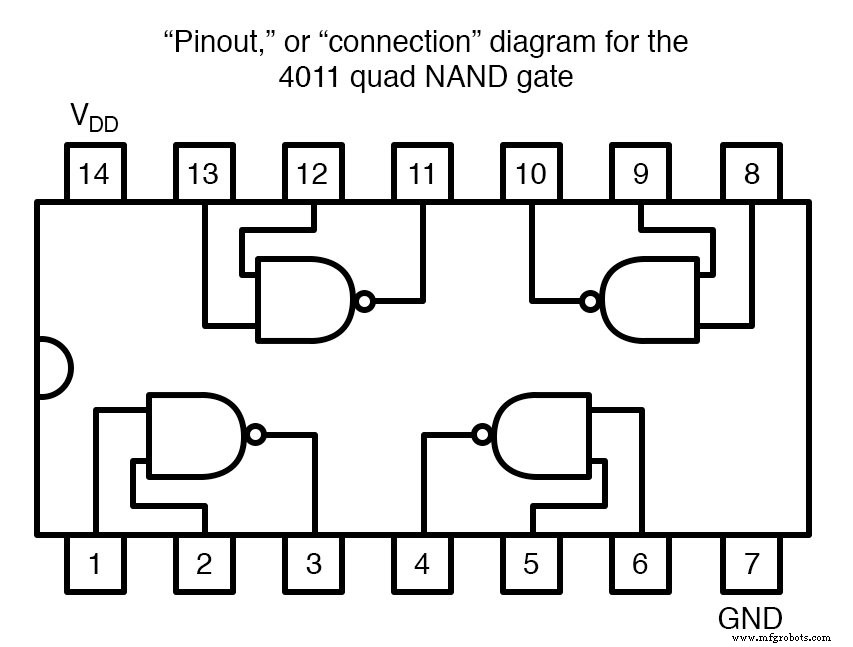

4011 のデータシートを用意することを強くお勧めします。 回路を構築するときに利用できるチップ。上に示した図に従うだけではいけません。 IC端子を他の回路素子に接続する場合は、データシート、特に「ピン配置」図を読むスキルを身に付けることが重要です。データシートの接続図は、持っておくべき重要な情報です。ここに示されているのは、 4011 の私自身の表現です。 データシートは次のことを示しています:

ブレッドボードの図では、左下のNANDゲートを使用して構築された回路を示しています。ピン番号1と2が入力で、ピン番号3が出力です。ピン番号の14と7は、ICチップ内の4つのゲート回路すべてにDC電力を伝導します。「V DD 」は電源のプラス側(+ V)を表し、「Gnd」は電源のマイナス側(-V)またはグランドを表します。負の電源端子には「V SS 」というラベルが付いている場合があります データシートの「Gnd」ではなく「」ですが、同じ意味です。

デジタルロジック回路は、オペアンプのように分割電源を使用しません。ただし、オペアンプ回路と同様に、グラウンドはすべての電圧測定の暗黙の基準点です。チップの特定のピンに「ハイ」信号が存在するということを言えば、そのピンと電源のマイナス側(グランド)の間に完全な電圧があったことを意味します。

4011 内の未使用のゲートのすべての入力に注意してください チップはV DD のいずれかに接続されています または地面。これは間違いではなく、意図的な設計の行為です。 4011 以降 はCMOS集積回路であり、CMOS回路入力は未接続のままです(フローティング )は、近くの物体からの静電荷を遮断するだけで任意の電圧レベルを想定できます。入力をフローティングのままにしておくと、未使用のゲートが「高」信号と「低」信号のランダムな組み合わせを受け取る可能性があります。

これらのゲートを使用していないのに、なぜこれが望ましくないのですか?私たちが彼らの出力で何もしていない場合、誰が彼らが受け取る信号を気にしますか?問題は、静的電圧信号が完全に「ハイ」または完全に「ロー」ではないゲート入力に現れる場合、ゲートの内部トランジスタが過剰な電流を引き込むような方法でオンになり始める可能性があることです。最悪の場合、これはチップの損傷につながる可能性があります。

せいぜい、それは過度の電力消費を意味します。これらの未使用のゲート入力を「ハイ」(V DD )に接続することを選択した場合、ほとんど問題になりません。 )または「低」(地面)、これら2つの場所のいずれかに接続している限り。ブレッドボードの図では、V DD に接続されているすべての上位入力を示しています。 、および(未使用のゲートの)すべての下部入力はグランドに接続されています。これは、電源レールの穴が近く、長いジャンパー線を必要としなかったという理由だけで行われました。

未使用のゲート出力はないことに注意してください V DD に接続されています または地面、そして正当な理由で!そうすると、ゲートが達成しようとしているのとは逆の出力状態になるように強制される可能性があります。これは、短絡が発生したと言う複雑な言い方です。 「高」論理レベルを出力することになっているゲートを想像してみてください(NANDゲートの場合、これは、その入力のいずれかが「低」である場合に当てはまります)。

このようなゲートの出力端子が直接グランドに接続されている場合、「ハイ」状態に達することはありません(ジャンパー線接続を介してグランドと電気的に共通になります)。代わりに、その上部(Pチャネル)出力トランジスタが無駄にオンになり、存在しない負荷に最大電流を供給します。これはゲートを損傷する可能性が非常に高いです!ゲート出力端子は、その性質上、独自の論理レベルを生成し、CMOSゲート入力と同じように「フロート」することはありません。

2つの10kΩ抵抗は、使用されるゲートでのフローティング入力条件を回避するために回路に配置されます。スイッチを閉じると、それぞれの入力がV DD に直接接続されます。 したがって、「高く」なります。スイッチを開いた状態で、10kΩの「プルダウン 」抵抗はグランドへの抵抗接続を提供し、ゲートの入力端子で安全な「ロー」状態を保証します。このようにして、入力は漂遊静電圧の影響を受けにくくなります。

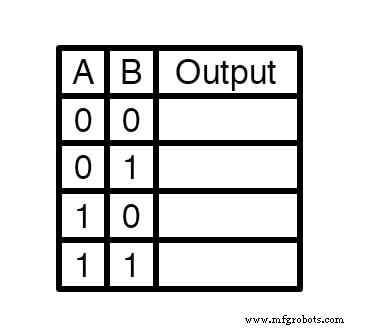

図のように2つのスイッチと1つのLEDにNANDゲートを接続すると、NANDゲートの「真理値表」を作成する準備が整います。 NANDゲートの真理値表がどのように見えるかをすでに知っている場合でも、これは実験の良い演習です。誘導によって回路の動作原理を発見します。このように一枚の紙に真理値表を描きます:

「A」 および「B」 列はそれぞれ2つの入力スイッチを表します。スイッチがオンの場合、その状態は「ハイ」または1です。スイッチがオフの場合、その状態は「ロー」または0であり、プルダウン抵抗によって保証されます。もちろん、ゲートの出力はLEDで表されます。つまり、ゲートが点灯しているか(1)、消灯しているか(0)です。スイッチを可能なすべての状態の組み合わせに配置し、LEDのステータスを記録した後、結果の真理値表をNANDゲートの真理値表と比較します。

ご想像のとおり、このブレッドボード回路はNANDゲートのテストに限定されていません。どのゲートタイプでも、2つのスイッチ、2つのプルダウン抵抗、および出力ステータスを示すLEDを使用してテストできます。 4011 の代わりにピンごとに置き換える前に、チップの「ピン配置」図を再確認してください。 。すべての「クワッド」ゲートチップに同じピン割り当てがあるわけではありません!

追加の改善

この回路に加えたい改善点は、出力を示すために割り当てられた1つのLEDに加えて、入力ステータスを示すために2つのLEDを割り当てることです。これにより、操作を観察するのが少し面白くなり、 true を表示することで、スイッチが閉じない(または開く)ことができないかどうかを示すというさらなる利点があります。 スイッチの位置から入力ステータスを推測するのではなく、ゲートに信号を入力します。

関連ワークシート:

-

基本的な論理ゲートワークシート

産業技術