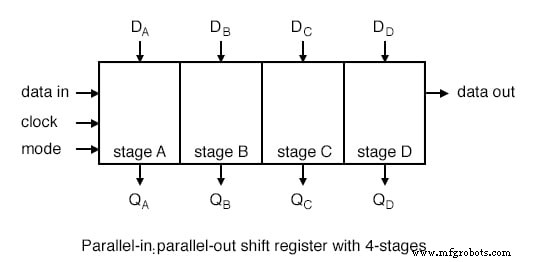

ユニバーサルシフトレジスタ:パラレル入力、パラレル出力

パラレルイン/パラレルアウトシフトレジスタの目的は、パラレルデータを取り込み、シフトしてから、以下のように出力することです。

ユニバーサルシフトレジスタは、パラレルイン/パラレルアウト機能に加えて、すべてを実行するデバイスです。

上記では、4ビットのデータを D A のパラレル入力/パラレル出力シフトレジスタに適用します。 D B D C D D 。複数の入力である可能性のあるモード制御は、並列ロードとシフトを制御します。

モード制御は、一部の実際のデバイスでシフトの方向を制御する場合もあります。データは、クロックパルスごとに1ビット位置にシフトされます。

シフトされたデータは、出力 Q A で利用できます。 Q B Q C Q D 。 「データ入力」と「データ出力」は、複数のステージをカスケードするために提供されています。

ただし、上記では、右シフトのデータのみをカスケードできます。上記の「データ入力」と「データ出力」のペアの左向き信号を追加することで、左シフトデータのカスケードに対応できます。

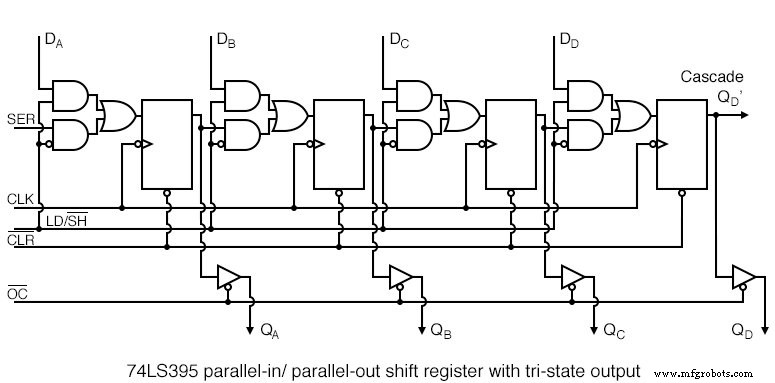

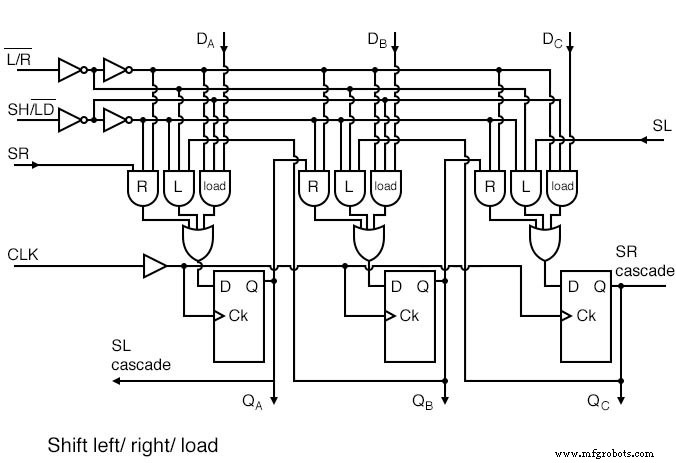

右シフトパラレルイン/パラレルアウトシフトレジスタの内部詳細を以下に示します。

トライステートバッファは、パラレルイン/パラレルアウトシフトレジスタに厳密に必要なわけではありませんが、以下に示す実際のデバイスの一部です。

74LS395は、仮想の右シフトパラレルイン/パラレルアウトシフトレジスタの概念と非常によく一致しているため、上記のデータシートの詳細の過度に簡略化されたバージョンを使用します。

詳細については、この章で後述する完全なデータシートへのリンクを参照してください。

LD / SH ’ FFへのデータ入力でAND-ORマルチプレクサを制御します。 LD / SH ’=1 の場合 、上位4つのANDゲートが有効になり、並列入力の適用が可能になります D A D B D C D D 4つのFFデータ入力に。

4つのFFのクロック入力でのインバーターバブルに注意してください。これは、74LS395が、ハイからローへの遷移である負方向のクロックでデータをクロックしていることを示しています。

4ビットのデータは D A から並列にクロックされます D B D C D D Q A へ Q B Q C Q D 次の負の時計で。この「実際の部分」では、 OC ’ 内部FFだけではなく、実際の出力ピンでデータを利用できるようにする必要がある場合は、ローにする必要があります。

LD / SH ’=0 の場合、以前にロードされたデータは1ビット位置だけ右にシフトされる可能性があります 後続の負方向のクロックエッジ用。

4クロックは、データを4ビットシフトレジスタから完全にシフトアウトします。デバイスが Q D からカスケードされない限り、データは失われます ’ SER へ 別のデバイスの。

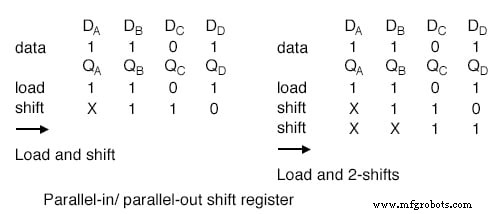

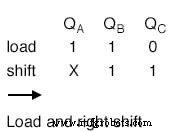

上記では、データパターンが入力 D A に表示されています D B D C D D 。パターンは Q A にロードされます Q B Q C Q D 。次に、1ビット右にシフトします。

受信データは X で示されます 、つまり、それが何であるかはわかりません。入力の場合( SER )は根拠があります。たとえば、どのデータ( 0 )がわかります。 )シフトインされました。

また、2つの位置で右シフトし、2つのクロックが必要です。

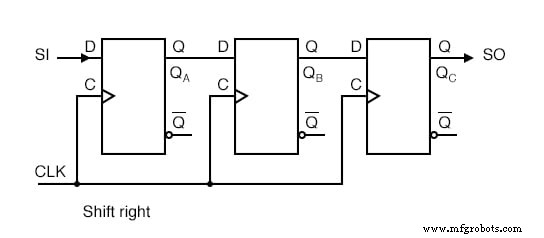

上の図は、データの右シフトに関係するハードウェアのリファレンスとして機能します。

従うべきより複雑な図との比較を除いて、この図を気にするのは簡単すぎます。

データの右シフトは、前の右シフターを参照するために上記で提供されています。

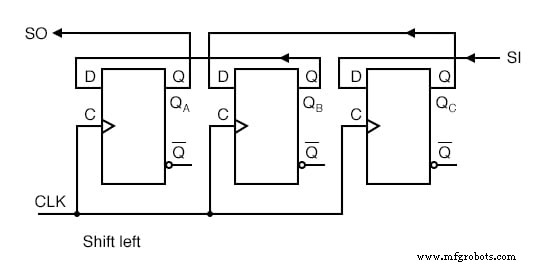

左にシフトする必要がある場合は、FFを再配線する必要があります。前の右シフターと比較してください。また、 SI および SO 逆転しました。 SI Q C に移行します 。 Q C Q B にシフトします 。 Q B Q A に移行します 。 Q A SO の葉 別のシフター SI にカスケードできる接続 。この左シフトシーケンスは、右シフトシーケンスから逆方向です。

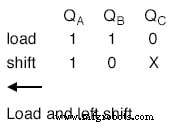

上記では、同じデータパターンを1ビット左にシフトしています。

上記の「左シフト」の図には1つの問題があります。そのための市場はありません。左シフト部品を製造している人は誰もいません。

一方向にシフトする「実際のデバイス」は、他の方向にシフトするために外部に配線することができます。または、一方向にのみシフトするデバイスのコンテキストでは、左または右は存在しないと言えます。

しかし、制御線によるコマンドで左または右にシフトするデバイスの市場があります。もちろん、その文脈では左と右が有効です。

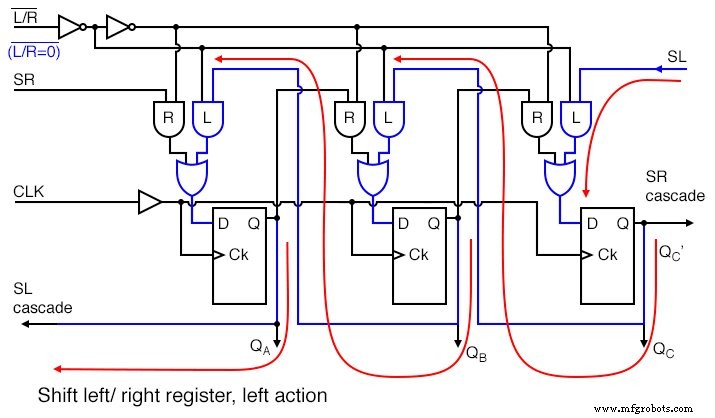

上記にあるのは、 L ’/ R の制御下でどちらの方向にもシフトできる架空のシフトレジスタです。 。

L ’/ R =1 で設定されています 法線方向を右にシフトします。 L ’/ R =1 R というラベルの付いたマルチプレクサANDゲートを有効にします 。

これにより、クロックが適用されたときに、データが矢印で示されているパスをたどることができます。接続パスは、上の「単純すぎる」「右シフト」の図と同じです。

データは SR にシフトインします 、 Q A へ 、 Q B へ 、 Q C へ 、 SRカスケードで出発します 。このピンは SR を駆動できます 右側にある別のデバイスの。

L ’/ R を変更するとどうなりますか L ’/ R =0 ?

L ’/ R =0 の場合 、 L というラベルの付いたマルチプレクサANDゲート が有効になり、上記の「左シフト」の図と同じように、矢印で示されているパスが生成されます。

データは SL にシフトインします 、 Q C へ 、 Q B へ 、 Q A へ 、 SLカスケードで出発します 。このピンは SL を駆動できます 左側にある別のデバイスの。

「左/右シフトレジスタ」を示す上記の2つの図の最大の利点は、単純さです。

左右のコントロールの操作 L ’/ R =0 従うのは簡単です。商用部品には、セクションタイトルで示されるパラレルデータロードが必要です。これは下の図に表示されています。

これで、 L ’/ R を介して左右両方にシフトできるようになりました 、 SH / LD ’を追加しましょう 、shift / load、および「load」というラベルの付いたANDゲートは、入力 D A からのデータの並列ロードを提供します。 D B D C 。

SH / LD ’=0 の場合 、ANDゲート R および L が無効になり、ANDゲートの「ロード」が有効になってデータを渡すことができる D A D B D C FFデータ入力に。次のクロック CLK データを Q A にクロックします Q B Q C 。

同じデータが存在する限り、後続のクロックで再ロードされます。ただし、1クロックのみ存在するデータは、データ入力に存在しなくなると出力から失われます。

1つの解決策は、1つのクロックでデータをロードしてから、次の4つのクロックでシフトに進むことです。この問題は、74ALS299で、マルチプレクサに別のANDゲートを追加することで解決されています。

SH / LD ’の場合 SH / LD ’=1 に変更されます 、「load」というラベルの付いたANDゲートが無効になり、左右の制御が可能になります L ’/ R L のシフト方向を設定します または R ANDゲート。シフトは前の図と同じです。

実行可能な統合デバイスを作成するために必要なのは、74ALS299で示唆されているように、マルチプレクサに4番目のANDゲートを追加することだけです。

これは、その部分の次のセクションで示されています。

パラレルイン/パラレルアウトおよびユニバーサルデバイス

Texas Instrumentsの厚意により、集積回路として利用可能なシリアル入力/パラレル出力シフトレジスタを詳しく見てみましょう。

完全なデバイスデータシートについては、リンクをたどってください。

-

SN74LS395Aパラレル入力/パラレル出力4ビットシフトレジスタ

-

SN74ALS299パラレル入力/パラレル出力8ビットユニバーサルシフトレジスタ

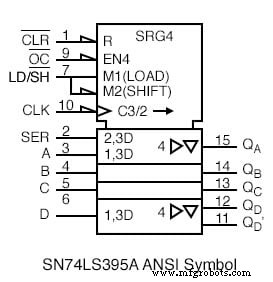

SN74LS395Aの内部の詳細についてはすでに説明しました。上の図、トライステート出力を備えた74LS395パラレル入力/パラレル出力シフトレジスタを参照してください。

真上には、74LS395のANSI記号があります。

SRG4 で示されているように、なぜ4ビットしかないのか その上?制御ピンと電源ピンに加えて、並列入力と並列出力の両方があると、16ピンDIP(デュアルインラインパッケージ)でこれ以上I / O(入力/出力)ビットを使用できなくなります。

R シフトレジスタステージが入力 CLR ’によってリセットされることを示します シンボルの上部にあるコントロールセクションの(入力でアクティブな低反転半矢印)。 OC ’ 、低い場合、(矢印を再び反転)は有効になります( EN4 )4つのトライステート出力バッファ( Q A Q B Q C Q D )データセクションで。

ロード/シフト」( LD / SH ’ )ピン(7)は内部 M1 に対応します (ロード)および M2 (シフト)。 1 のプレフィックスを探します および 2 シンボルの残りの部分で、これらによって何が制御されているかを確認します。

ネガティブエッジセンシティブクロック(ピン10の反転矢印で示されます) C3 / 2 2つの機能があります。

まず、 3 C3 / 2 の プレフィックスが 3 の入力に影響します 、 2,3D と言います または 1,3D データセクションで。

これは、 A、B、C、D での並列負荷になります M1 に起因 および C3 1,3D の場合 。次に、 2 C3 / 2 の -右矢印は、 2 のデータクロッキングを示します プレフィックスに表示されます( 2,3D ピン2で)。

したがって、 SER でデータのクロッキングがあります Q A に モード 2 。 C3 / 2 の後の右矢印 内部シフトレジスタステージでのシフトを考慮します Q A Q B Q C Q D 。

右向きの三角形はバッファリングを示します。逆三角形は、 EN4 によって制御されるトライステートを示します 。

すべての 4 に注意してください s EN に関連付けられた記号 しばしば省略されます。ステージ Q B Q C Q D と同じ属性を持つと理解されています 。 Q D ’ 次のパッケージの SER にカスケードします 右に。

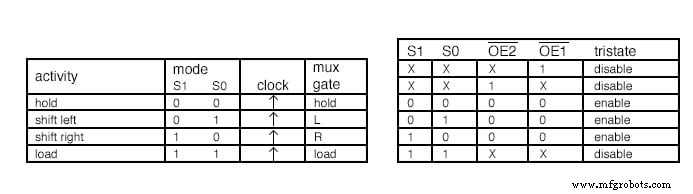

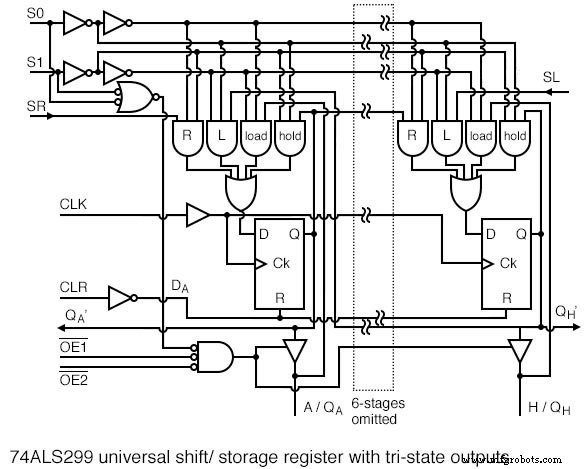

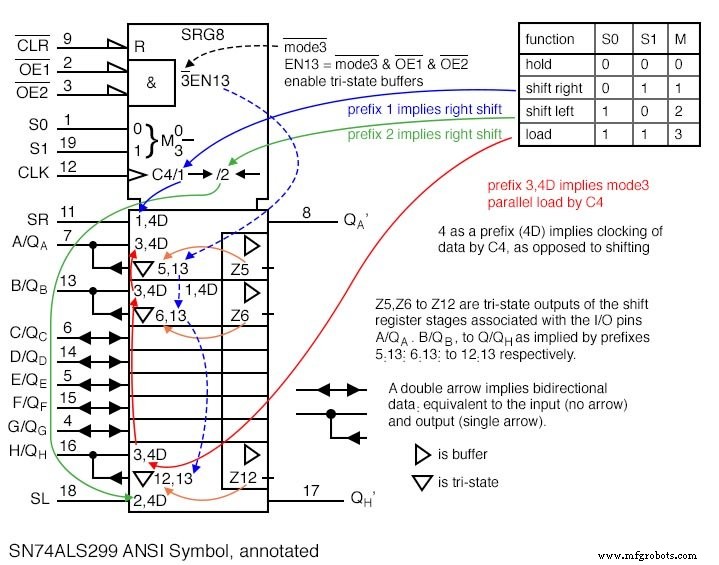

上記の表は、データ ‘299データシートから要約されたもので、74ALS299ユニバーサルシフト/ストレージレジスタの動作をまとめたものです。

詳細については、上記の「299」リンクをたどってください。マルチプレクサゲート R 、 L 、ロード 前の「左/右シフトレジスタ」の図と同じように動作します。

違いは、モードが S1 を入力することです。 および S0 [左にシフト]、[右にシフト]を選択し、モードを S1 S0 =に設定してロードします。 01 へ 、 10 、および 11 それぞれ表に示されているように、マルチプレクサゲートを有効にします L 、 R 、およびロード それぞれ。

表を参照してください。わずかな違いは、トライステート出力からの並列ロードパスです。実際には、トライステートバッファは S1 S0 =11 によって無効にされます(無効にする必要があります)。 I / Oバスをフロートさせる 入力として使用します。

バスは同様の信号の集まりです。入力は A に適用されます 、 B H を介して ( Q A と同じピン 、 Q B 、 Q H を介して )そしてロードにルーティングされます マルチプレクサのゲート、および D FFの入力。データはクロックパルスの並列負荷です。

新しいマルチプレクサゲートの1つは、 hold というラベルの付いたANDゲートです。 、 S1 S0 =00 によって有効化 。 保留 ゲートは Q からのパスを有効にします FFの出力をホールドに戻します ゲート、同じFFのD入力へ。結果は、モード S1 S0 =00 の場合です。 、出力は、新しいクロックパルスごとに継続的に再ロードされます。したがって、データが保持されます。これは表にまとめられています。

出力からデータを読み取るには Q A 、 Q B 、 Q H を介して 、トライステートバッファは OE2 ’、OE1’ =00 で有効にする必要があります およびモード= S1 S0 =00、01、または10 。

つまり、モードはロード以外のものです。 。 2番目の表を参照してください。

データをパッケージから左に右シフトし、 SR にシフトインします 入力。データはステージQ H から右にシフトアウトされました Q H を介して右にカスケードします ’。

この出力は、トライステートバッファの影響を受けません。 S1 S0 =10 の右シフトシーケンス は:

SR> Q A > Q B > Q C > Q D > Q E > Q F > Q G > Q H (Q H ’)

パッケージから右にシフトするデータは、 SL にシフトインします 入力。ステージQ A から左にシフトアウトされたデータ Q A を介して左にカスケードします ’、トライステートバッファの影響も受けません。 S1 S0 =01 の左シフトシーケンス は:

(Q A ’)Q A B

C

D

E

F

G

H (Q SL ’)

シフトは、 OE2 ’のいずれかによってトライステートバッファが無効にされた状態で発生する可能性があります または OE1 ’=1 。ただし、レジスタの内容の出力にはアクセスできません。表を参照してください。

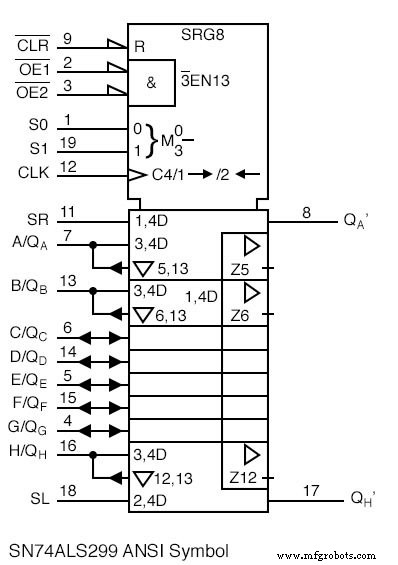

トライステート出力を備えたSN74ALS299パラレル入力/パラレル出力8ビットユニバーサルシフトレジスタの「クリーンな」ANSIシンボルは、上記の参照用に示されています。

注釈付きバージョンのANSIシンボルは、そこに含まれる用語を明確にするために示されています。

ANSIモード(S0 S1)は、前の表で使用された順序(S1 S0)と逆になっていることに注意してください。

これにより、10進数のモード番号(1と2)が逆になります。いずれにせよ、私たちは公式のデータシートに完全に同意し、この矛盾をコピーします。

実用的なアプリケーション

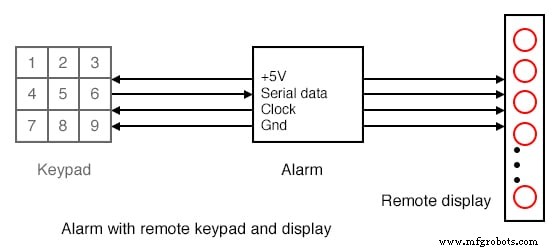

リモートキーパッド付きアラームのブロック図を以下に繰り返します。以前は、キーパッドリーダーとリモートディスプレイを別々のユニットとして構築していました。

次に、ユニバーサルシフトレジスタを使用して、キーパッドとディスプレイの両方を1つのユニットに結合します。

図では分離されていますが、キーパッドとディスプレイは両方とも同じリモートエンクロージャー内に含まれています。

キーボードデータを単一のクロックパルスでシフトレジスタにパラレルロードしてから、メインのアラームボックスにシフトアウトします。

同時に、LEDデータをメインアラームからリモートシフトレジスタにシフトして、LEDを点灯させます。

キーボードデータとLEDデータを同時にシフトレジスタにシフトします。

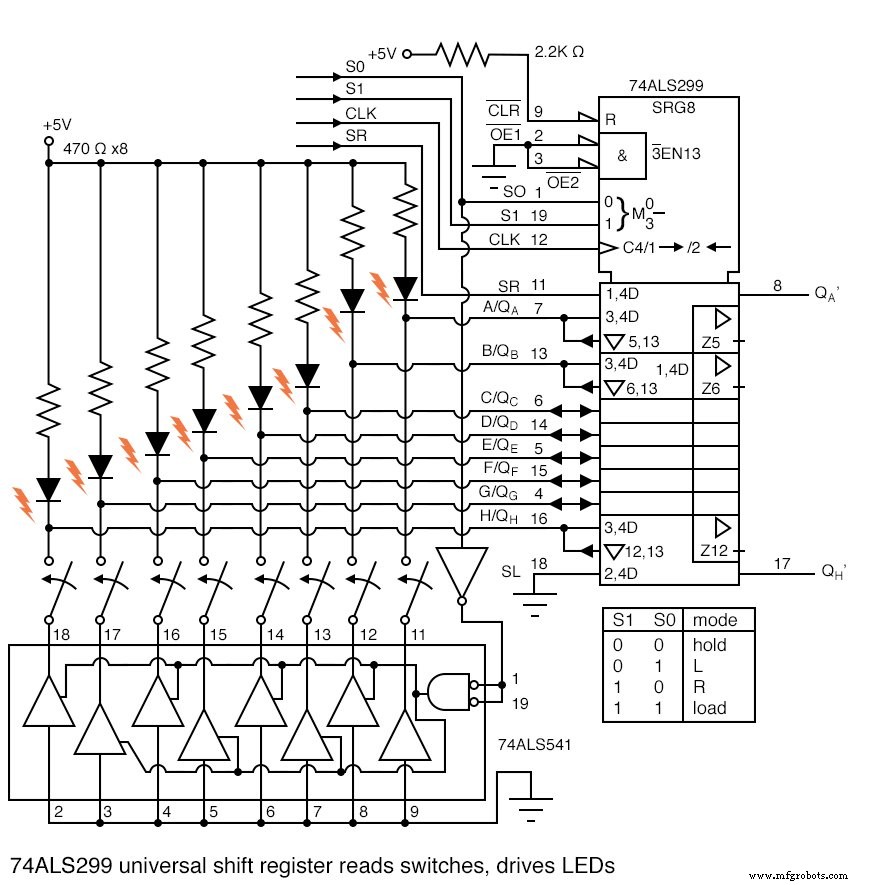

7つのLEDと電流制限抵抗が74ALS299ユニバーサルシフトレジスタの8つのI / Oピンに接続されています。

LEDは、 S1 =0 S0 =0 のモード3でのみ駆動できます。 。 OE1 ’ および OE2 ’ トライステートイネーブルは、モード 0、1、2 の間にトライステート出力を永続的に有効にするために接地されています 。

これにより、シフト中にLEDが点灯(点滅)します。これが問題だった場合は、 EN1 ’および EN2’ 接地されておらず、 S1 と並列化されている可能性があります および S0 それぞれ、トライステートバッファのみを有効にし、ホールド中にLEDを点灯するモード 3 。この例では単純にしましょう。

並列ロード中、 S0 =1 0に反転すると、8進数のトライステートバッファがスイッチワイパーを接地できるようになります。

上部の開いたスイッチ接点は、8つの入力での抵抗器とLEDの組み合わせによってロジックハイに引き上げられます。

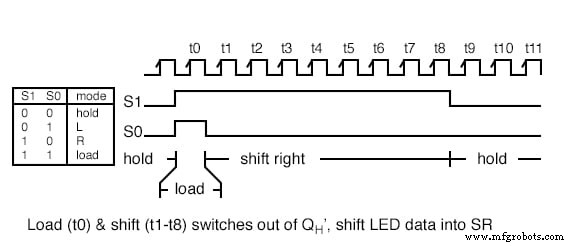

スイッチを閉じると、入力がローに短絡します。スイッチデータを ‘299 にパラレルロードします 時計で t0 両方の S0 および S1 高いです。以下の波形を参照してください。

一度 S0 ローになり、8クロック( t0 to t8 )スイッチの閉鎖データを ‘299 からシフトします Q h 経由 ’ ピン。

同時に、新しいLEDデータは SR にシフトインされます 299 の 同じ8つの時計で。シフトが進むにつれて、LEDデータがスイッチクロージャデータに置き換わります。

8番目のシフトクロックの後、 t8 、 S1 ローになってホールドモードを生成します( S1 S0 =00 )。 T9 のように、より多くのクロックがある場合でも、シフトレジスタのデータは同じままです。 、 t10 、など。

波形はどこから来ていますか?クロックレートが100kHzを超えていない場合、マイクロプロセッサによって生成される可能性があります。その場合、 t8 以降にクロックを生成するのは不便です。 。

時計がメガヘルツの範囲にある場合、時計は継続的に動作します。時計、 S1 および S0 ここには示されていませんが、デジタルロジックによって生成されます。

関連するワークシート:

- シフトレジスタワークシート

産業技術