デジタルランプADC

階段ランプとも呼ばれます 、または単にカウンター A / Dコンバーター、これもかなり理解しやすいですが、残念ながらいくつかの制限があります。

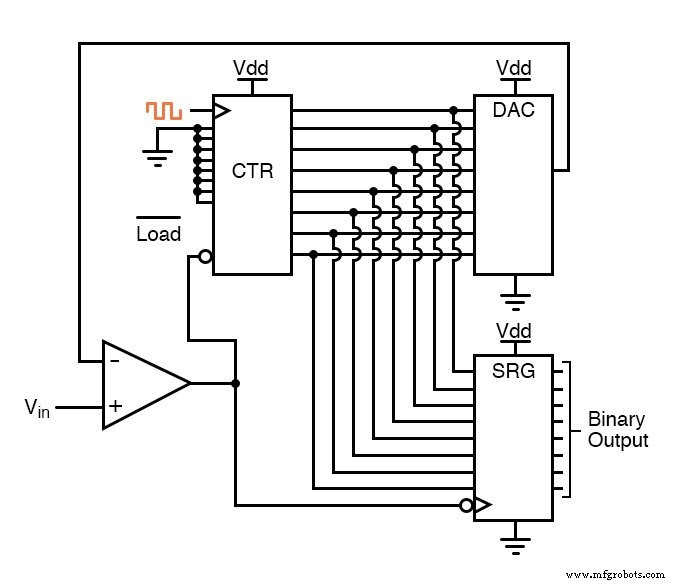

基本的な考え方は、自走バイナリカウンタの出力をDACの入力に接続し、DACのアナログ出力をデジタル化するアナログ入力信号と比較し、コンパレータの出力を使用してカウンタに停止するタイミングを指示することです。カウントしてリセットします。次の概略図は、基本的な考え方を示しています。

カウンタが各クロックパルスでカウントアップすると、DACはわずかに高い(より正の)電圧を出力します。この電圧は、コンパレータによって入力電圧と比較されます。

入力電圧がDAC出力よりも大きい場合、コンパレータの出力は高くなり、カウンタは通常どおりカウントを続けます。ただし、最終的には、DAC出力が入力電圧を超え、コンパレータの出力が低くなります。

これにより、2つのことが起こります。1つは、コンパレータの出力のハイからローへの遷移により、シフトレジスタがカウンタによって出力されているバイナリカウントを「ロード」し、ADC回路の出力を更新することです。次に、カウンタはアクティブローのLOAD入力でロー信号を受信し、次のクロックパルスで00000000にリセットされます。

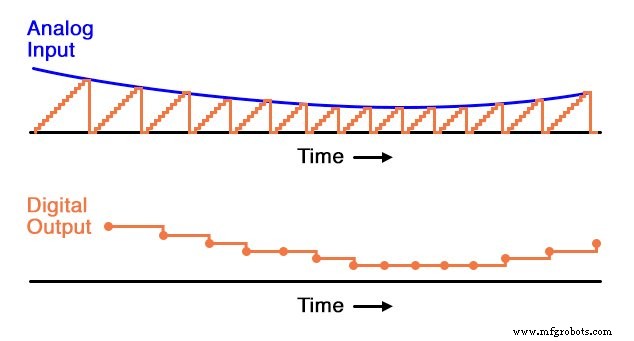

この回路の効果は、アナログ入力信号のレベルに応じてランプアップするDAC出力を生成し、そのレベルに対応する2進数を出力して、最初からやり直すことです。時間の経過とともにプロットすると、次のようになります:

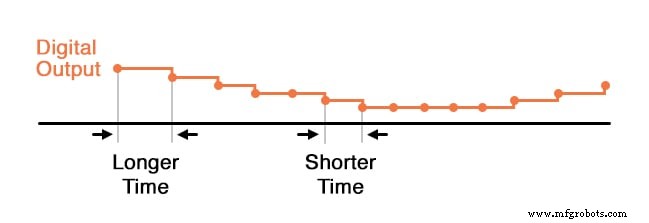

入力電圧の高さに応じて、更新(新しいデジタル出力値)間の時間がどのように変化するかに注意してください。信号レベルが低い場合、更新はかなり狭い間隔で行われます。より高い信号レベルの場合、それらは時間的にさらに離れて配置されます:

多くのADCアプリケーションでは、この更新周波数(サンプル時間)の変動は許容できません。これと、各カウントサイクルの開始時に回路が0からずっとカウントする必要があるという事実により、アナログ信号のサンプリングが比較的遅くなり、デジタルランプADCが他のカウンタ戦略に不利になります。

>産業技術