フラッシュADC

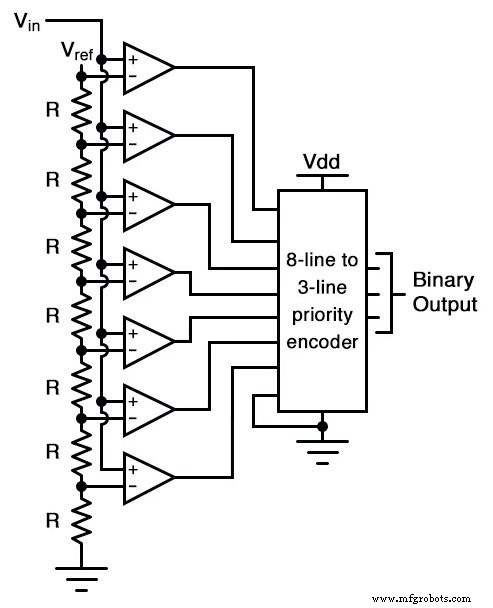

パラレルとも呼ばれます A / Dコンバータ、この回路は最も理解しやすい回路です。これは一連のコンパレータで構成されており、各コンパレータが入力信号を固有の基準電圧と比較します。コンパレータ出力はプライオリティエンコーダ回路の入力に接続され、プライオリティエンコーダ回路はバイナリ出力を生成します。次の図は、3ビットフラッシュADC回路を示しています。

V ref は、回路図には示されていない、コンバータ回路の一部として高精度電圧レギュレータによって提供される安定した基準電圧です。アナログ入力電圧が各コンパレータのリファレンス電圧を超えると、コンパレータ出力は順次ハイ状態に飽和します。プライオリティエンコーダは、他のすべてのアクティブな入力を無視して、最上位のアクティブな入力に基づいて2進数を生成します。

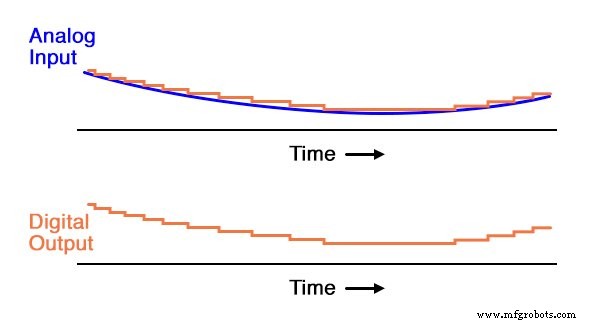

フラッシュADCを動作させると、次のような出力が生成されます。

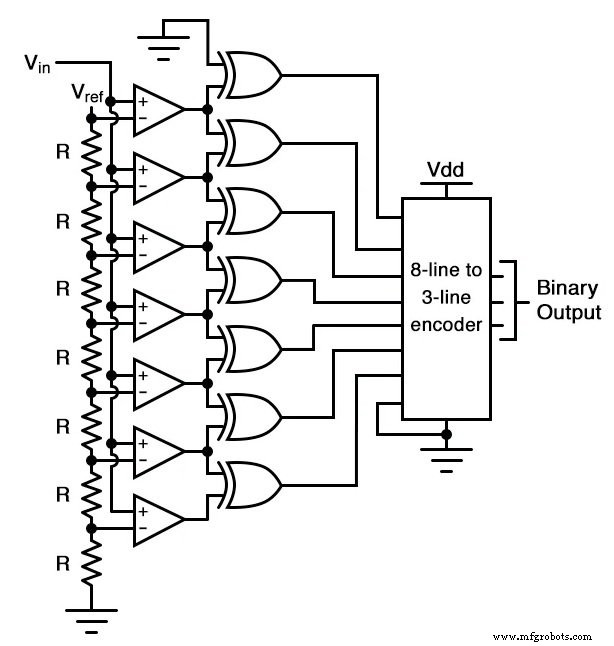

この特定のアプリケーションでは、固有の複雑さをすべて備えた通常のプライオリティエンコーダは必要ありません。シーケンシャルコンパレータの出力状態の性質により(各コンパレータは最低から最高まで順番に「高」に飽和します)、同じ「最高次入力選択」効果が排他的論理和ゲートのセットを通じて実現される場合があります。よりシンプルで優先度の低いエンコーダーの使用:

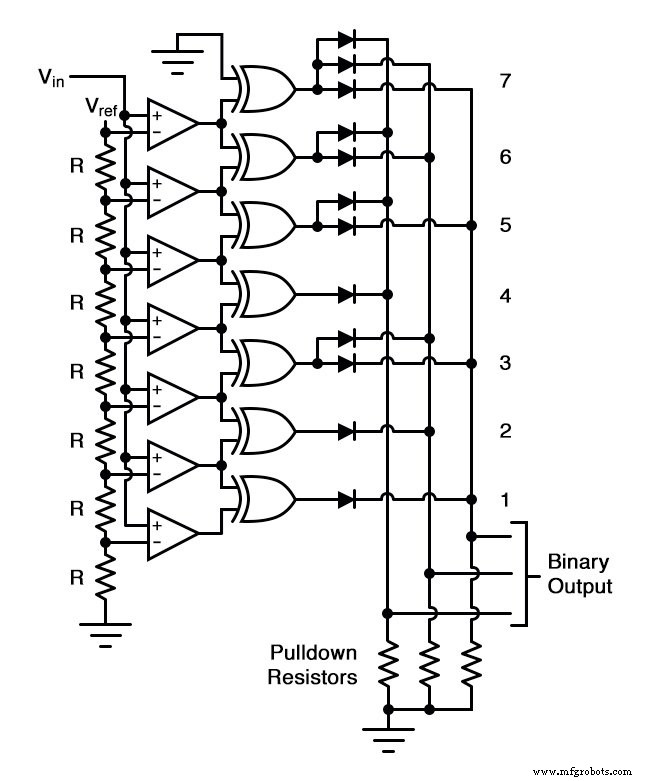

そしてもちろん、エンコーダ回路自体はダイオードのマトリックスから作成することができ、このコンバータの設計がいかに簡単に構築できるかを示しています。

フラッシュコンバータは、動作理論の点で最も単純であるだけでなく、速度の点でもADCテクノロジの中で最も効率的であり、コンパレータとゲートの伝搬遅延のみに制限されます。残念ながら、これは任意の数の出力ビットに対して最もコンポーネントを集中的に使用します。

この3ビットフラッシュADCには、7つのコンパレータが必要です。 4ビットバージョンには15個のコンパレータが必要です。出力ビットが追加されるたびに、必要なコンパレータの数は2倍になります。

8ビットが実際のADCに必要な最小値であると一般に考えられていることを考えると(255個のコンパレータが必要です!)、フラッシュの方法論はすぐにその弱点を示します。フラッシュコンバーターの追加の利点は、見過ごされがちですが、非線形出力を生成できることです。

基準分圧器ネットワークに等しい値の抵抗を使用すると、連続する各バイナリカウントは同じ量のアナログ信号の増加を表し、比例応答を提供します。ただし、特殊なアプリケーションでは、分周器ネットワークの抵抗値が等しくない場合があります。

これにより、ADCはアナログ入力信号に対するカスタムの非線形応答を得ることができます。他のADC設計では、わずかなコンポーネント値の変更でこの信号調整動作を許可することはできません。

関連ワークシート:

- アナログ-デジタル変換ワークシート

産業技術