JTAGコネクタとインターフェイス

JTAGの実装に使用されるインターフェースとコネクタについて学びます。

以前の記事では、元のJTAG標準であるIEEE1149.1について見てきました。これには、ユーザーがステートマシンを操作してデバイス内部にアクセスし、バウンダリスキャンテストを実行できるようにするJTAGテストアクセスポート(TAP)が含まれていました。

ただし、この情報はJTAGを理解するために不可欠ですが、コネクタやピン配置、市場で入手可能な市販のJTAGインターフェイスなどの物理的な側面も理解する必要があります。この記事では、JTAG全体に対して理論的ではないアプローチを取りながら、状況を改善します。

JTAGコネクタ

JTAG用の標準コネクタはありません。多くの場合、「JTAGコネクタ」は、0.1インチヘッダーやより細かいピッチのヘッダーなどの標準のオスヘッダーです。これまで見てきたように、JTAG TAPを操作するために必要なピンは4つ(または5つ)だけです。ただし、TAPとの「通信」に使用されるデバイス( JTAGインターフェイスと呼ばれる) また、電源とアースの接続も必要です。設計者は、必要に応じてJTAGヘッダーに他の接続を含めることができます。

では、ボードを考えると、設計者はどのようにJTAGアクセスを提供する必要がありますか?そして、新しいボードがあれば、JTAGコネクタをどこで見つける必要がありますか?

JTAGインターフェイスの標準ヘッダーは1つではありませんが、いくつかのヘッダータイプがメーカー間で多かれ少なかれ標準化されています。これらには、ARM JTAG 20、ARM JTAG 14、TI JTAG 14、STMicroelectronicsのSTDC14、InfineonのOCDS 16ピンヘッダー[pdf]、CoreSight 10、CoreSight 20、MIPI 34、およびMictor38が含まれます。 。Seggerは、J-LinkおよびJ-TraceコネクタをARM JTAG20とほぼ同じであると定義しています。

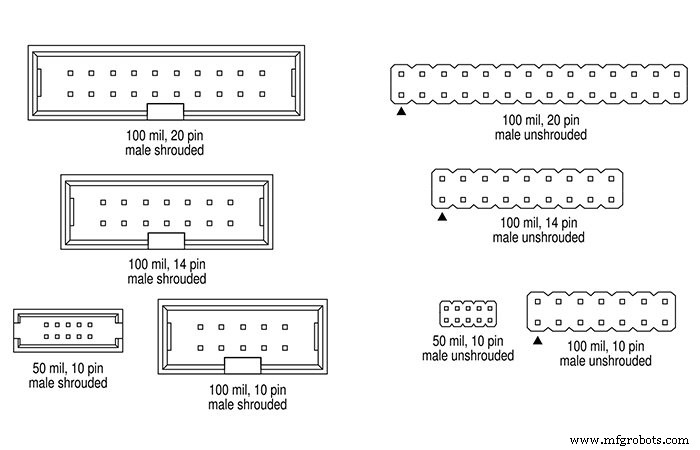

ほとんどのヘッダーは、10、14、または20ピン、0.1インチまたは0.05インチのピンピッチのシュラウド付きまたはシュラウドなしのオスヘッダーです。例を図1に示します。

図1。 JTAGインターフェイスへの接続に使用される共通ヘッダー。

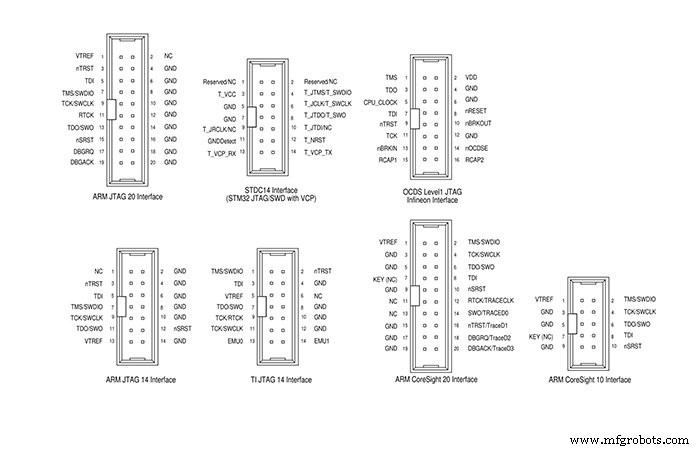

さまざまなJTAGインターフェイス(上記のリンク)のピン配置を図2に示します。ここには、JTAGの標準ピン(TDI、TDO、TCK、TMS、nTRST)と、シリアルワイヤデバッグ(SWDIO、SWCLK、SWO)があります。 )、およびコアトレースなどのデバッグ用の追加機能。

図2。 さまざまなJTAGインターフェースのピン配列。この場合、0.1インチのシュラウド付きオスヘッダーに表示されます。

追加されたピンの中で特に注目すべきは、ターゲットを完全にリセットするnSRST(フルシステムリセット)と、JTAGインターフェイスハードウェアレベルシフト用のターゲット電源レールに接続されたVTREF(電圧ターゲットリファレンス)です。

JTAGインターフェース

いくつかのJTAGインターフェイス(JTAGデバッグプローブとも呼ばれます)が市販されています。オープンソースハードウェアの分野では、1BitSquaredとBlack SphereTechnologiesによって開発されたBlackMagic ProbeまたはBMPがあり、ARM JTAGインターフェイスとして使用され、それをサポートする大規模で活発なコミュニティがあります。 Black Magic Probeは、ファームウェアがBlack MagicProbeファームウェアに置き換えられたJTAGインターフェイスを参照することもできます。

Seggerの市販の広く使用されているデバッグプローブには、J-Link(図3に示す)と、産業用アプリケーションに適したかなり高度で高性能なデバッグプローブであるJ-Traceがあります。 J-Linkが教育ライセンスの下で100ドル未満、または商用アプリケーションの場合は400ドルから1,000ドルの間で見つかる場合、J-Traceのコストは1,700ドルから2,500ドルの間です。

図3。 Segger J-LinkPROデバッグプローブとJTAGインターフェイス

特定のベンダーは、自社製品のJTAGインターフェイスも販売します。 STMicroelectronicsはSTM8およびSTM32製品用のSTLINKシリーズ(STLINK / V2およびSTLINK-V3SETを含む)を提供し、Atmel(現在のMicrochip)はAtmel-ICEを提供し、NXPはS32デバッグプローブを提供します。リストは続きます。

FPGAもJTAGを使用してビットストリームをデバイス/メモリにダウンロードしますが、これらのインターフェイスはダウンロードケーブルと呼ばれることがよくあります。例としては、ザイリンクスのプラットフォームケーブルIIやアルテラのFPGAダウンロードケーブル(以前はUSB-Blaster IIと呼ばれていましたが、現在はIntelFPGAダウンロードケーブルIIとしてブランド名が変更されています。

)があります。では、これらのデバイスで何が起こっているので、非常に高価になっているのでしょうか。それらはどのような機能をサポートし、設計者はそれらをどのように使用しますか?一般に、ローエンドのデバッグプローブの内部を見ると、次のことがわかります。

- メインのJTAGコントローラーとしてのマイクロコントローラー

- USBインターフェース。マイクロコントローラーに組み込まれている場合もあれば、FTDIチップなどに個別に組み込まれている場合もあります。

- ロジック互換性のためのレベルシフト回路

- さまざまなパス、プルアップなどを有効または無効にするためのスイッチング回路

そして、それについてです。例として、Githubで入手可能なBlack MagicProbeハードウェアファイルを見てください。作業(およびコスト)の多くはソフトウェア側で行われ、開発者がArm CoreSightアーキテクチャを最大限に活用できるようにする強力な(場合によってはリアルタイムの)デバッグツールを提供します。

結論

これまで、テストアクセスポート(TAP)とそのステートマシンを含むJTAG標準について説明してきました。この記事では、JTAGの物理的な側面を見て、オープンソースから商用ハイエンドまでの設計者が利用できるコネクタとインターフェイスを調査しました。

ここからは、Arm CoreSightアーキテクチャとそのデバッグインターフェイス(ADI)を詳しく見ていきます。これには、ますます一般的になっているシリアルワイヤデバッグ(SWD)JTAGの代替手段が含まれます。

産業機器