eFPGAカスタムブロックスーパーチャージデータアクセラレーションシステム

私は長い間、Achronixから出てくるテクノロジーに興味を持っていました。彼らは、2004/2005年頃に非同期FPGAファブリックで最初に私の興味を引きました。最終的に、これは2 GHzでクロックされる同期FPGAと同等の速度に達することができました(そのような獣がいた場合)が、限られた数のアルゴリズムおよびデータフローアプリケーションにのみ適用可能でした。

2013年、AchronixはSpeedsterと呼ばれる高性能で高密度のスタンドアロンFPGAファミリを発売しました。これらは、対象となるアプリケーションに重点を置いています。 Achronix製品ポートフォリオは、高性能の組み込みFPGA(eFPGA)であるSpeedcoreによって2016年に拡張されました。

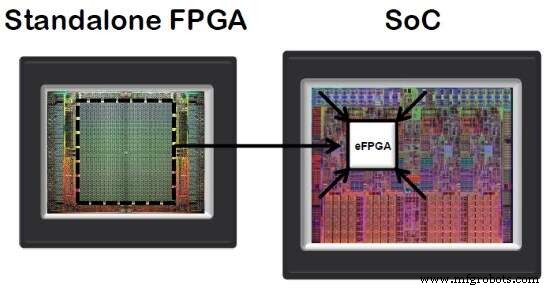

FPGAは、データ集約型の人工知能(AI)/機械学習(ML)、5Gワイヤレス、自動車用ADAS、データセンター、およびネットワーキングアプリケーションを加速するのに理想的です。 1つの解決策は、SpeedsterなどのスタンドアロンFPGAを、スタンドアロンプロセッサまたはシステムオンチップ(SoC)と組み合わせて使用することです。ただし、コアFPGAファブリック(eFPGA)をSoC自体に埋め込むことで、はるかに高いパフォーマンスと大幅に低い消費電力を実現できます。

(出典:Achronix)

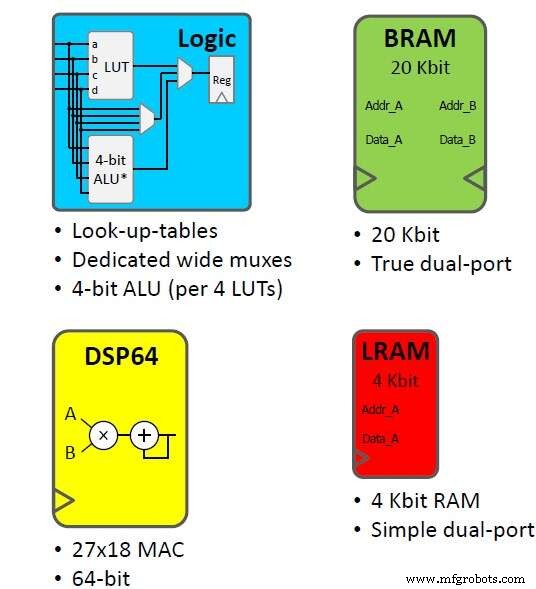

Speedcoreの場合、SoC開発者は、Logic、DSP、BRAM、およびLRAM用の事前定義されたブロックのライブラリにアクセスできます。

Speedcoreブロック(出典:Achronix)

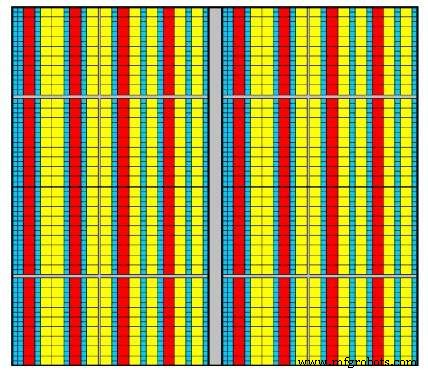

これらのブロックは列に表示されます。さらに、開発者は、必要な「高さ」(列のブロック数)、「幅」(列の数)、および「混合」(列のタイプ)を指定できます。たとえば、ロジックを増やしてDSPを減らすことでメリットが得られるプロジェクトもあれば、DSPとメモリを増やす必要があるプロジェクトもあります。

開発者はSpeedcoreファブリックの「ミックス」を指定できます(出典:Achronix)

現在、世界のソフトウェア側に住む人々は、コードをプロファイリングしてボトルネック機能を特定し、それを微調整して可能な限り最高のパフォーマンスを実現することに慣れています。さて、Achronixは現在、フェンスのハードウェア側にたむろしている私たちと同じ機能を提供しています。

可能な限り最高のパフォーマンスを要求する開発者のために、AchronixはSpeedcoreカスタムブロックを作成する機能を提供するようになりました。これらのカスタムブロックは、アクセラレーションワークロードの詳細なアーキテクチャ分析を通じて、Achronixとその顧客が共同で定義します。パフォーマンスやエリアのボトルネックである繰り返し機能は、Speedcoreカスタムブロックに強化する理想的な候補を提供します。

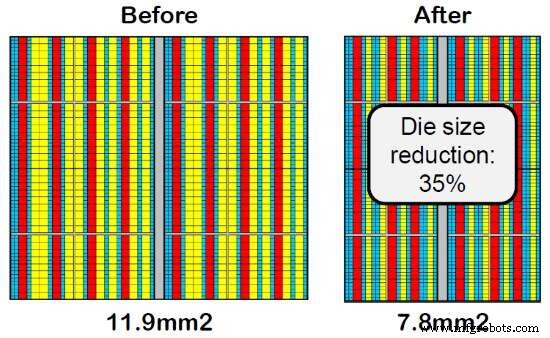

一例として、高度なリアルタイムの物体検出および識別システムで使用されるYOLO(「一度だけ見る」)物体認識機能について考えてみます。この場合、行列乗算用にDSPとメモリブロックを最適化するSpeedcoreカスタムブロックを作成して展開すると、ダイサイズが大幅に削減されました。

AI畳み込みネットワークのダイサイズの縮小(出典:Achronix)

Achronix ACEデザインツールは、メモリやDSPブロックと同じように、デザインキャプチャからビットストリーム生成、システムデバッグまでのSpeedcoreカスタムブロックを完全にサポートします。 Achronixは、すべての構成ルールを管理するSpeedcoreカスタムブロックごとに一意のGUIを作成します。 ACEには、Speedcoreカスタムブロックのすべての構成の完全なタイミングの詳細が含まれているため、デザインのタイミングベースの配置配線を完了できます。最後になりましたが、開発者はACEの強力なSnapShot組み込みロジックアナライザーを使用して、複雑なトリガーを作成し、Speedcoreデバイス内でランタイム信号を表示することもできます。

Speedster、Speedcore、およびSpeedcoreカスタムブロックの詳細については、AchronixのWebサイトにアクセスしてください。

埋め込み