Renodeを使用して共同設計されたSoCの設計サイクルの長さを短縮する

この記事では、AntmicroのRenodeのようなオープンソースの機能シミュレーターの使用がハードウェアとソフトウェアの共同設計の取り組みの不可欠な部分になる方法について説明します。 。

この記事では、AntmicroのRenodeのようなオープンソースの機能シミュレーターの使用が、ハードウェアとソフトウェアの共同設計の取り組みの不可欠な部分となる方法について説明します。

Semico Researchによると、市場が組み込みシステムにさらに多くのことを要求するにつれて、次世代SoCはより複雑になり、設計サイクルが長くなり、コストが上昇することになります。

デバイスメーカーにとって苛立たしい現実は、顧客が求めている新しい革新的な機能、より優れたセキュリティ、およびより優れたパフォーマンスを提供する唯一の方法は、「スタック全体」の共同設計、進化するハードウェア、ファームウェア、ランタイムに従事することです。 (OS)、および連携した開発ツールチェーン。そうすることで、ハードウェアチームとソフトウェアチームは、機能と最適化を実装するために、スタック内のどこにあるかという複雑なトレードオフに対処できます。

残念ながら、適切なシミュレーションツールが配置されていない場合、共同設計は設計サイクルを長くする主な要因であり、したがってコストがかかることがよくあります。

この記事では、AntmicroのRenodeのようなオープンソースの機能シミュレーターの使用が、ハードウェアとソフトウェアの共同設計の取り組みに不可欠な部分となる方法について説明します。さらに、Renodeユーザーがツールを活用して設計サイクルの長さを大幅に短縮し、顧客がソリューションを評価するためのシンプルで効果的な手段を提供し、ソフトウェア資料の適応を並行して開始する方法の例を示します。ハードウェア統合の取り組みを伴う。

ソフトウェアシミュレータが不足する可能性がある場所

適切なシミュレーションツールを選択することの重要性は、ドーバーマイクロシステムズの場合に最もよく示されています。

DoverのCoreGuard®テクノロジーは、ソフトウェアの脆弱性の悪用を防ぎ、プロセッサがネットワークベースの攻撃から身を守ることを可能にする唯一のソリューションです。 Doverは、8年間の研究開発を通じてこれを達成することができました。最初は、DARPAクラッシュプログラムで最大のパフォーマーとして、次にDraper Labsで、組み込みシステム向けの独自のハードウェア/ソフトウェアハイブリッドソリューションを生み出しました。

このハイブリッドソリューションでは、ハードウェアコンポーネントとソフトウェアコンポーネントの両方を緊密に統合する必要があります。 CoreGuardシリコンIPは、ボディーガードとして機能し、組み込みシステムをサイバー攻撃から保護する歩哨プロセッサです。ホストプロセッサによって実行されるすべての命令を監視して、CoreGuardのソフトウェアコンポーネントであるマイクロポリシーと呼ばれる、定義された一連のセキュリティ、安全性、およびプライバシーのルールに準拠していることを確認します。命令が既存のルールに違反している場合、CoreGuardは、損傷が発生する前にその命令の実行を停止します。

これを実現するには、CoreGuardがホストプロセッサの実行に対応する必要があります。つまり、平均して、保護されているホストプロセッサと同じレートで命令をリタイア(マイクロポリシーを介して承認)できる必要があります。 CoreGuardがメタデータ管理に必要なメモリの量を最小限に抑えることも望ましいです。

したがって、パフォーマンス、電力、および面積の要求を満たすには、ハードウェア層とソフトウェア層の両方からの最適化の複雑な相互作用が必要です。

Doverのハードウェアチームは、標準のSystemVerilogベースのプロセスとツールチェーンを使用しています。 CoreGuardシステムの初期プロトタイプは、RISC-VベースのSoC上に構築されています。 CoreGuardにはハードウェアIPに加えて実質的なソフトウェアコンポーネントがあるため、ハードウェアプロトタイプが利用可能になる前に、ソフトウェアチームが十分に開始できることが重要でした。

Doverのソフトウェアチームは当初、RISC-VGitHubリポジトリから入手できるSpikeRISC-VISAソフトウェアシミュレーターを使用していました。彼らは、スパイクを中心としたCoreGuardの商用開発に基づいて2つの問題に遭遇しました。

- スパイクは現実的な周辺機器を提供しません。つまり、SpikeはISAシミュレーターであり、SoCシミュレーターではありません。 Doverチームは、UARTや永続ストレージなどの周辺機器をSpikeに追加し始めましたが、これは大変な作業でした。

- スパイクは、定義上、RISC-V固有ですが、DoverMicrosystemsの最初の顧客はRISC-VとArmベースの両方です。

これらの欠点は、スパイクの代わりに使用される周辺機器モデルの概念を備えた柔軟なマルチアーキテクチャシミュレータに対するドーバーの必要性を浮き彫りにしました。

Renodeが重要な共同設計のニーズにどのように対処するか

オープンソースのソフトコア、最先端のコンピューティングプラットフォーム用の初期のソフトウェア、FPGA SoC、およびオープンソースに焦点を当てたRISC-V、Antmicroなどの新しいCPUアーキテクチャでの作業に起因する、同様の異種ハードウェア/ソフトウェアの共同設計エンジニアリングの課題に直面しています。テクノロジーおよびサービスプロバイダー—Renodeと呼ばれる柔軟なシミュレーションフレームワークを開発しました。

Renodeは、相互接続されたマルチノード、マルチアーキテクチャ、異種、MCUレベル、Linux対応システムなど、さまざまな複雑なシステムで実際の本番(つまり、変更されていない)ファームウェアを実行することを目的とした階層型のモジュラーシミュレーションフレームワークです。

>これらのさまざまなレベルの複雑さに取り組むために、Renodeは抽象化の強力な概念に基づいて構築されており、システムシミュレーションにオブジェクト指向のモジュラーアプローチを採用しています。コアと周辺機器は、実際のSoCの構築方法を反映して、さまざまな構成のインターフェイスを介して接続できるビルディングブロックと見なされます。

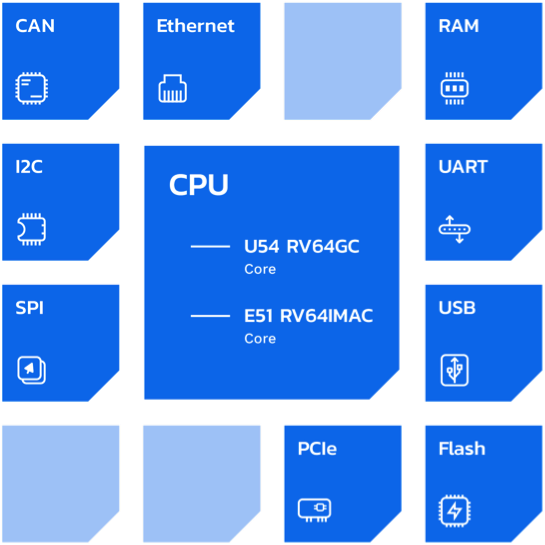

図1。 シミュレートされたRISC-VSoCの例。

図1は、シミュレートされたRISC-VSoCの例を示しています。 CPUを含む各ビルディングブロックには、SoC全体のシミュレーションモデルを構築するために使用できる一連のプロパティとAPIがあります。同様に、単一ノードは、仮想化された無線および有線接続(6LoWPAN、UART、イーサネットなど)を使用して、マルチノードシステムにさらに組み合わせることができます。これはすべて、Renodeのコードベースを変更する必要はありませんが、構成とスクリプトを介して行われるため、学習曲線が短縮され、コードベースの断片化が制限されます。

Renodeフレームワークの柔軟な性質、オープンソースの可用性、および作成者が提供する商用サポートの存在により、Doverは最初に目的のワークフローのプロトタイプ実装を構築し、次にAntmicroと契約して実装(およびオープンにリリース)することが容易になりました。ソースドメイン)命令ごとの実行など、Renodeをユースケースにさらに適したものにする機能。

特に、Renodeを使用すると、Doverのエンジニアは次のことができるようになります。

- 同じセットアップを使用して、ArmベースとRISC-Vベースの統合作業を切り替えます。

- さまざまな詳細レベル/忠実度でのプロトタイプSoC(参照/最小および顧客定義の両方)。

Doverのハードウェアグループからハードウェアアーキテクチャ仕様をモデル化し、ハードウェアの開発中に、それらのモデルに対してファームウェアを作成してテストします。

Renodeがドーバーの設計サイクルを大幅に短縮した方法

DoverのCoreGuardテクノロジーは、ハードウェアとソフトウェアの両方の設計が進化しているハイブリッドサイバーセキュリティ製品です。その結果、ドーバーの開発プロセスで、ハードウェアとソフトウェアの両方の並行開発とテストが可能になることが重要です。

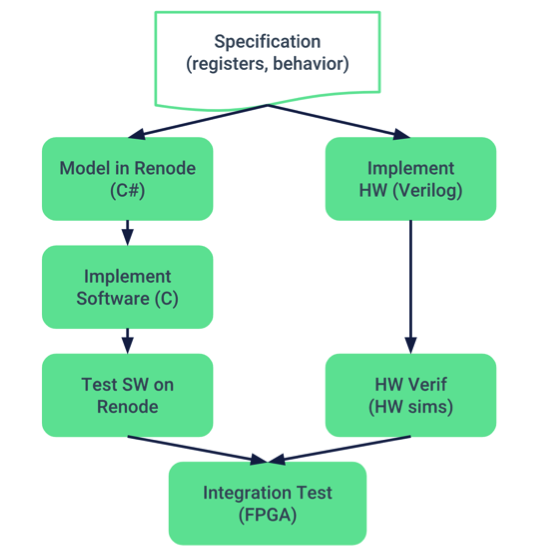

図2。 ドーバーが使用する開発プロセス。

Doverは、図2に概説されている開発プロセスを使用しています。ハードウェアチームとソフトウェアチームは、ハードウェアインターフェイスで共同作業を行います(もちろん、これは進化し続けます)。ハードウェアチームがSystemVerilogでブロックの実装を開始すると、ソフトウェアチームは、Renodeの基礎となる母国語であるC#で新しいブロックのモデルを作成します。その後、ソフトウェアチームは、新しいハードウェアインターフェイスと通信するファームウェアを作成し、Renodeシミュレーションでそのソフトウェアをテストできます。最終的に、ソフトウェアはFPGAエミュレーターで実行されます。

Renodeによって可能になったこの開発プロセスは、Doverが「低忠実度」と「高忠実度」の両方のシミュレーションを最適化するのに役立ちました。

この「忠実度の低い」シミュレーションはCoreGuardのすべてのハードウェアロジックを抽象化しますが、Doverは、この設定が次のコンテキストで役立つと考えています。

- マイクロポリシーのデバッグ: 新しいCoreGuardマイクロポリシーが開発されているときは、さまざまなソフトウェアテストに対して迅速に反復して、動作を確認したいと考えています。

- デモと顧客のプレビュー: CoreGuardのデモンストレーションでは、CoreGuardの®機能について潜在的な顧客を教育し、さらなる議論への関心を刺激するには、純粋なソフトウェアシミュレーションで十分なことがよくあります。さらに、Doverは、顧客のソフトウェアに対してCoreGuardマイクロポリシーを実行することを含め、顧客がCoreGuardで「遊ぶ」ために、いくつかの事前定義されたマイクロポリシーを備えたこの「低忠実度」シミュレータで構成される「SDK」を顧客に提供することがよくあります。

より正確なハードウェアモデルを複製する「高忠実度」シミュレーションでは、ドーバーエンジニアリングチームは、次のようなRenodeの多くの利点を認識することができました。

- ハードウェアブートROMで使用されるさまざまな非ELF(スキャッターロードなど)バイナリ形式との統合。

- ブートプロセスの開発とテスト。フラッシュからRAMにコピーし、デバイスを初期化します。

- Renodeインストルメンテーションを使用したバストラフィックのデバッグ。

- インストルメンテーションによる周辺機器(UART、PIC、CoreGuardインターフェース自体)のデバッグ。

- メモリマップで遊んでいます。

- ハードウェアが機能する前に、HDMIビデオファームウェアを実装します。

前に示したように、CoreGuardなどの次世代ソリューションが実装中にSoC設計チームに課すいくつかの困難なパフォーマンスと領域の制約があります。

パフォーマンスを向上させ、メモリ使用量を削減するために、ハードウェア/ソフトウェアの境界を超えることが多い、さまざまな最適化を行う必要があります。

設計チームが、大規模なシリアル化された「最初のハードウェア、次にソフトウェアの開発プロセス」なしで、可能なハードウェア/ソフトウェアの協調最適化手法とトレードオフの広い範囲を調査できることが重要です。 Renodeなどの柔軟なソフトウェア機能シミュレーターにより、ドーバーのエンジニアはハードウェアとソフトウェアの違いを超えて協力し、ハードウェアとソフトウェアの複雑さの間の最適なトレードオフを見つけて、彼らの努力に不可欠なものにすることができます。

Renodeが共同設計プロジェクトを合理化する方法の詳細については、renode.ioにアクセスしてください。 CoreGuardが組み込みシステムをネットワークベースの攻撃から保護する方法の詳細については、デモをリクエストしてCoreGuardの動作を確認してください。

この記事は、ビジネス開発担当副社長であり、Antmicroの共同創設者であるMichaelGieldaによって共同執筆されました。

業界記事は、業界パートナーが編集コンテンツに適さない方法でAll About Circuitsの読者と有用なニュース、メッセージ、テクノロジーを共有できるようにするコンテンツの形式です。すべての業界記事は、読者に有用なニュース、技術的専門知識、またはストーリーを提供することを目的とした厳格な編集ガイドラインの対象となります。業界記事で表明されている見解や意見はパートナーのものであり、必ずしもAll AboutCircuitsやそのライターのものではありません。

埋め込み

- 組み込みシステム設計とは:設計プロセスのステップ

- ソフトウェアで解決できる4つの積層造形の課題

- 専門家インタビュー:ジェネレーティブデザインソフトウェアでAMの可能性を高めるnTopology CEO

- ロボット工学で未来を設計する

- PCB設計におけるRFフィードラインの最適化

- FPGAを使用した組み込み設計:プロジェクトの構築

- 最高のジュエリーデザインCADソフトウェアを選択する方法

- ヒューズを使用したジェンダーに配慮した個別化された製品の製造1

- Steve Ricard(PODCAST)を使用してCMMSソフトウェアに移行する

- 適切なソフトウェアで卸売注文管理をマスターする方法

- クラウド製造ソフトウェア テクノロジーに最適なものを見つける