7nmに向かって前進

これは、IEDM2016でのIBM特集論文に関する4部構成のシリーズの第4回です。

毎年恒例の国際電子デバイス会議は、「半導体および電子デバイスの技術、設計、製造、物理学、モデリングの分野における技術革新を報告するための世界有数のフォーラム」です。そこで、IBMの研究者は、走査型プローブ温度計、10ナノメートルチップ用のエアスペーサー、7 nmチップを持ち込み、シリコンに負けないように、カーボンナノチューブも持ち込みました。 IBM社員と多くのパートナーによるこれらの論文とプレゼンテーションは、今週サンフランシスコで開催される会議に参加します。

IEDMは、このコンピューティングの再想像の会議の最良の例として、4つのIBMの論文を取り上げています。ムーアの法則を拡張し、新しいアーキテクチャを構築し、新しい材料を使用してそれを超えています。これらの論文と、研究の背後にある科学者を詳しく見てみましょう。シリーズの最終回では、GlobalFoundriesの技術スタッフのシニアメンバーであり、Albany NanotechCenterのIBMチームのメンバーであるRuilongXieによる論文「EUVパターニングとデュアルストレインドハイモビリティチャネルを備えた7nmFinFETテクノロジー」に焦点を当てています。 。

昨年7月、IBMとそのアライアンスパートナーは、世界初の7nmノードテストチップを開発したと発表しました。画期的な進歩は、極端紫外線(EUV)リソグラフィー(光を使用して他の材料にパターンをエッチングする技術)を適用し、トランジスタのチャネル材料としてシリコンゲルマニウム(SiGe)を使用することで実現しました。

シリコンからシリコンゲルマニウムへ

チームのIEDMペーパーは、「SiGeベースのFinFETテクノロジーは、10nmテクノロジーの基本ルール(業界標準)によるパフォーマンスの向上を実証し、実行可能なCMOSテクノロジーオプションに向けたエレガントなソリューションを提供することを示しています。これらの洗練されたソリューションの1つは、同じチップ上で低電力デバイスと高性能デバイスの両方を可能にすることです。 7nmへの材料革新で説明されているように、あるタイプのデバイスのパフォーマンスや変動性を失うことはありません。 。

さらに、SiGeは、電流がトランジスタのチャネルを通過する方法を変更することにより、チップスケーリングの限界を押し広げます。小さなシリコン原子でできた結晶に大きなゲルマニウム原子を加えることにより、結晶は格子不整合を生じ、トランジスタチャネルに歪みを発生させることがわかります。このひずみにより、より低い電圧でより多くの電流をチャネルに流すことができます。したがって、寄生抵抗と静電容量の削減の革新と組み合わせてチャネル材料としてSiGeを使用することにより、チームは、電力とパフォーマンスのバランスを維持しながら、7nmチップへのロードマップを作成できます。これは、IEDMで提示された一定の電力でのパフォーマンスです。 、10nmチップよりも40%優れています!

非常に短い波長の光

使用されている光は、波長が13.5 nmしかないため、今日の標準的な193 nmの波長の光よりもはるかに短く、200億個の7nmトランジスタをチップにエッチングすることができます。しかし、チームがその数のスイッチをチップに搭載する前に、そのような短波長を使用する背後にあるテクノロジーを、一貫性があり、制御され、再現可能なプロセスにする必要があります。

リソグラフィーを使用してチップを作成するには、すべての非デジタル写真ネガがコンタクトペーパーに印刷されるのとほぼ同じ方法で、ウェーハを光のパターンにさらします。ウェーハの上に保持され、光がマスク(「ネガ」)を通過します。 。この技法を使用して印刷できる線とワイヤーのサイズは、マスク上の線のサイズだけでなく、使用されている光の波長も反映します。現在、193 nmの光を使用すると、必要なパターンが193 nmで提供できるパターンよりも小さい場合、ウェーハが複数回露光される可能性があります。

そのため、日本の木版画と同じように、パターンを次々とウェーハの上に重ねて、より複雑で小さなチップを作成します。ただし、このマルチパターン手法は劣化を引き起こします。これは、スマートフォンなどの大量生産されたデバイスのチップにとってはそれほど重要な問題ではないかもしれませんが、非常に高い信頼性を必要とするスーパーコンピューターや特殊なシステムにとっては重大な障害です。そして、この方法で7 nmチップを製造することは技術的には可能ですが、IBMがEUV技術を使用して7nmチップを製造する方法を模索することを決定した大きな理由です。

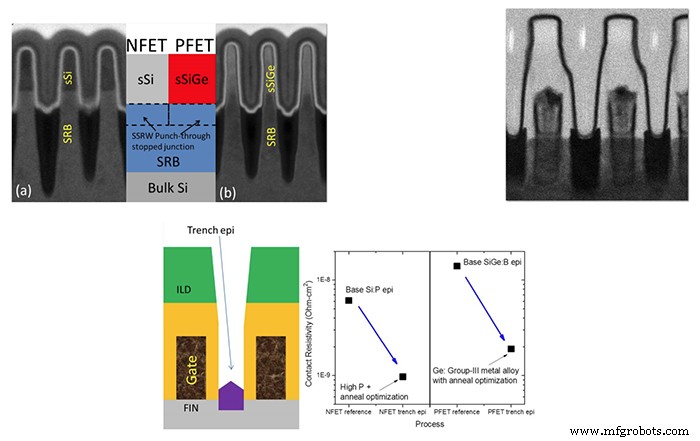

左上: 超急勾配逆行ウェル(SSRW)を備えたSRB上の二重応力チャネル材料の概略図と、(a)引張ひずみシリコンフィンおよび(b)一般的なSRB上の圧縮ひずみSiGeフィンのTEM画像。 右上: 接触開口部が約10nm、Lmetalが約15nmの最適化された自己整合接触を備えた48nm接触ポリシリコンピッチデバイスのTEM画像。 中央下: 図とグラフは、トレンチエピタキシャルプロセスが、インプラントとアニーリングの最適化に続いて、基本ルールと接触抵抗率の低下を同時に満たすことを示しています。

13.5 nm EUVを使用すると、7nmチップに単一のパターンを印刷するために必要な高忠実度パターンは1つだけです。 EUVの課題は、技術を成熟させて生産の準備を整える方法です。 1964年に構築されたIBMSystem 360が、改良、スケーリング、エンジニアリングの取り組みを通じて今日のより小型で高速なマシンにつながったのと同じように、EUVも同様の方法で成熟する必要があります。

これを考慮してください:13.5 nmの光を生成するために、EUVデバイスは溶融スズの液滴を真空に放出し(球形にするため)、次に炭酸ガスレーザーを当てて平らにし、特定の角度に移動します。まだ落下しているスズは、さらに強力な炭酸ガスレーザーで叩かれ、気化して13.5 nmの光を放出します。この光は、特殊なミラーを使用してキャプチャされ、ウェーハに焦点を合わせます。

この13.5nmの光を使用するプロセスは複雑ですが、チームの作業により、EUVを使用して7 nmのチップを作成することが可能であり、高品質の結果が得られることが証明されています。つまり、次世代のスーパーコンピューターやシステムの需要を満たすために、将来の高性能システムに特化した高信頼性チップを製造できるということです。

パート1を読む:ホットスポットのマッピング

パート2を読む:カーボンナノチューブを備えた別の種類のチップ

パート3を読む:10nmチップ用のエアスペーサー

ナノマテリアル