10nmチップ用のエアスペーサー

これは、IEDM2016でのIBM特集論文に関する4部構成のシリーズの3番目です。

毎年恒例の国際電子デバイス会議は、「半導体および電子デバイスの技術、設計、製造、物理学、モデリングの分野における技術革新を報告するための世界有数のフォーラム」です。そこで、IBMの研究者は、走査型プローブ温度計、10ナノメートルチップ用のエアスペーサー、7 nmチップを持ち込み、シリコンに負けないように、カーボンナノチューブも持ち込みました。 IBM社員と多くのパートナーによるこれらの論文とプレゼンテーションは、今週サンフランシスコで開催される会議に参加します。

IEDMは、このコンピューティングの再想像の会議の最良の例として、4つのIBMの論文を取り上げています。ムーアの法則を拡張し、新しいアーキテクチャを構築し、新しい材料を使用してそれを超えています。これらの論文と、研究の背後にある科学者を詳しく見てみましょう。第3部は、IBMResearchのシニアテクニカルスタッフメンバーでありMasterInventorであるKangguoCheng博士による論文「10nmFinFETCMOS以降のエアスペーサー」に関するものです。

現在、14 nmノードチップを製造できますが、次のノードへの飛躍には大きな課題が残っています。トランジスタが小さくなると、寄生容量(不要な電荷)によって2つの問題が発生します。トランジスタ間の信号スイッチングが遅くなり、消費電力が増加します。 IBMのAlbanyNanotech CenterのChengと彼のチームは、10nmトランジスタの絶縁体として空気を使用する方法を調査しました。彼らのエアスペーサーは、トランジスタレベルでの静電容量を最大25%削減し、リングオシレータテスト回路の静電容量を最大15%削減することを示しています。

トランジスタには、チャネル、チャネルの両端にある2つのリザーバ(いわゆるソースとドレイン)、およびトランジスタをオンまたはオフにするためにチャネルを制御するゲートの4つの重要な要素があります。接点(金属合金)を使用して、ソース、ドレイン、およびゲートをトランジスタの上のワイヤに接続し、トランジスタを接続して残りの回路を完成させます。トランジスタがどんどん小さくなり、互いに近づくにつれて、トランジスタの接点間のギャップも小さくなります。電荷の一部は、有用な仕事をするためにチャネルに流れ込む代わりに、これらのギャップに蓄積されます。トランジスタが切り替わると、蓄積された電荷が再び出て、エネルギーを浪費します。これらの追加の電子を前後に動かすためにより多くの電力が必要になるため、チップを機能させるためにより多くのエネルギーが必要になります。これにより、チップが高温になり、場合によっては使用できなくなることもあります。

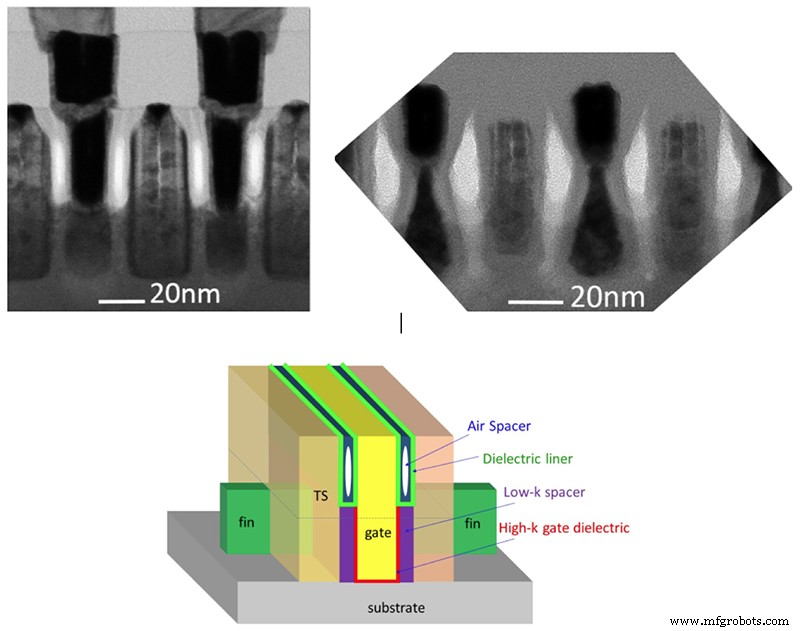

左上: 10nm寸法のエアスペーサー(空白)を備えたFinFETトランジスタのTEM画像。 右上: 積極的なスペーサープルダウンプロセス後の損傷。具体的には、フィンの侵食とソース/ドレインエピタキシー。 中央下: 部分的なエアスペーサー構造の概略図。エアスペーサーは、ゲートスタックへの影響を最小限に抑えるためにフィントップの上にのみ形成されています。誘電体ライナーは、エアスペーサーの製造プロセス中にゲートスタックをさらに保護するために使用されます。

そのため、これらの厄介な電子が接点間に付着するのを防ぐために、近くの接点の間に新しい材料を配置する必要がありました。最高の素材は素材ではなく、空気です。そこでIBMチームは、トランジスタの接点間に空気で満たされた小さなスペースを作成して、ギャップに蓄積される電子の数を制御する方法を見つけ出しました。開発されたプロセスにより、トランジスタの消費電力は25%少なくなり、ひいては回路全体で15%少なくなります。

エアスペーサーは、次世代システムの10および7 nmチップ、および潜在的により効率的な14nmチップに到達するのに役立ちます。

パート1を読む:ホットスポットのマッピング

パート2を読む:カーボンナノチューブを備えた別の種類のチップ

ナノマテリアル