7nm以降の材料革新の鍵

ニューヨーク州アルバニーの半導体研究チームは、将来のノードに向けてCMOSテクノロジーを拡張し続けています(10 nm、7 nm、およびそれ以上)。電流の流れを決定するトランジスタチャネル抵抗と、それに接続する方法は、チップの全体的なパフォーマンス。したがって、特定の将来の半導体技術のパフォーマンスの競争力を確保するために、トランジスタのチャネル抵抗を低減するためのチャネル材料の革新は、重要な研究分野です。そのため、昨年の7nmチップの発表で概説された電力性能の利点を達成するために必要な元素であるシリコンゲルマニウム(SiGe)を調査しています。

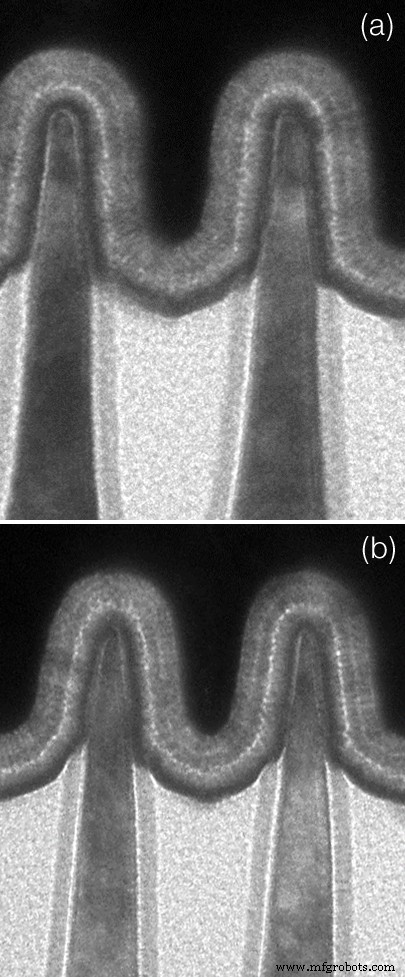

対称Siニューヨーク州アルバニーにあるSUNYPolytechnicのNanoTechComplexでIBMResearchが作成した10nmでのFinFET(a)およびSiGe FinFET(b)プロファイル。これは、SiGeFinがSiFinよりも優れた電気的特性を提供できることを示しています。

今日の14nmノードのFinFET *ベースのチップは、シリコンのみのチャネルを使用しています(シリコンはこのスケールを超えて安定していません)。あるいは、SiGeベースのFinFETテクノロジは、10nmテクノロジの基本ルール(業界標準)によるパフォーマンスの向上を実証しており、実行可能なCMOSテクノロジオプションに向けたエレガントなソリューションを提供します。これらのエレガントなSiGeFinFETソリューションの1つは、同じチップ上で低電力デバイスと高性能デバイスの両方を可能にすることです。あるタイプのデバイスのパフォーマンスや変動性を他のタイプと比較して失うことはありません。

SiGe FinFETテクノロジーは、SiFinFETよりも優れた電気的信頼性も提供します。そしてこれは、チップ寿命にわたってSiFinFETよりも改善されたチップレベルの性能安定性につながります。これは、同じプロセス統合フローがスーパーコンピューターの設計だけでなくモバイルの設計にも適していることを意味します。

SiGeは、電流がトランジスタのチャネルを通過する方法を変更することにより、チップスケーリングの限界を押し広げます。小さなシリコン原子でできた結晶に大きなゲルマニウム原子を加えることにより、結晶は格子不整合を生じ、トランジスタチャネルに歪みを発生させることがわかります。このひずみにより、より低い電圧でより多くの電流をチャネルに流すことができます。したがって、チャネルマテリアルとしてSiGeを使用することで、電力とパフォーマンスのバランスを維持しながら、より小さな次元へのロードマップをグラフ化できます。

先のノードのSiGe:10nmおよび7nmチップの製造に関する課題の解決

積分フロー全体でのひずみ保持と欠陥制御は、10nmノード以下でSiGeFinFETを製造するための2つの主要な技術的課題です。トランジスタチャネルは、ドーパントを活性化し、トランジスタの完全性を安定させる熱アニーリングプロセス中にひずみを失う可能性があります。または、フィンの上部からフィンの下部まで均一な接合部を形成するソース/ドレインのくぼみプロセス中。または、短い長さのフィンを必要とする特定の設計のフィンのパターン化。

欠陥制御は、CMOS技術の大量生産においても重要です。 SiGeチャネルとそのシリコンウェーハ基板の間の格子不整合により、ウェーハ全体にわたって必要な製造可能性の欠陥レベルを維持することは困難です。しかし、高度なエピタキシャル(結晶)成長管理、革新的なFinモジュールプロセス統合、およびソース/ドレインエンジニアリングにより、統合フロー全体を通じてチャネルのひずみを確保すると同時に、10nmおよび7nmテストで低い欠陥率を維持するソリューションを開発しました。ノード。

10nmテクノロジの基本ルールでのこの包括的なSiGeFinFETテクノロジの実現可能性調査により、現在、チップ設計者およびチップメーカーと協力して、SiGeFinFETテクノロジを大量生産しています。私たちのSiGeFinFETテクノロジーは、スーパーコンピューターからモバイルデバイスに至るまで、コンピューティング用途の次世代CMOSテクノロジーノードでシリコンFinFETに取って代わることを期待しています。また、クラウドやコグニティブコンピューティングのアプリケーションなど、低電力供給と低消費電力が非常に望ましい「ムーア以上の」アプリケーションIクラウドやコグニティブコンピューティングでも使用できます。

さらに読む

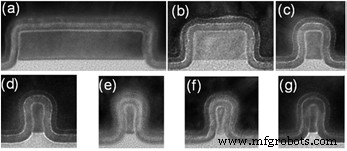

断面SiGeフィンのGe含有量を増やすための87nm(a)から3nm(g)の範囲のフィン幅のフィンとゲートスタックの組み合わせ。

今年のVLSI(超大規模集積回路)技術に関するIEEEシンポジウムで、私たちのチームは、10nmの基本ルールでSiGeを使用することを中心に、またスケーリングを解決するための道として、多くの新しいデバイス、材料、および統合の革新を発表しました。昨年製造した7nmテストノードのパフォーマンスの課題。

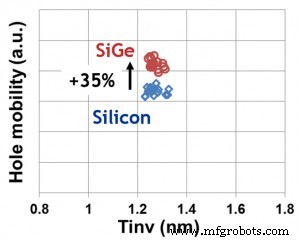

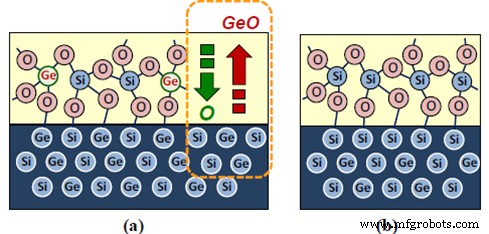

私たちのプレゼンテーションでは、欠陥制御のための重要な技術的特徴と基本的なプロセス革新について説明しました。 SiGeFINに適したゲートスタックと界面層の革新。また、VLSI会議の研究論文T2.2で報告された、SiGeFinFETプラットフォームの高度な接触技術。 T4.3の研究論文は、SiGeチャネル用の堅牢な界面層を構築するための独創的な選択的酸化ゲルマニウム掃気プロセスを紹介しました。

明確なモビリティSiFinよりもSiGeFinの利点があり、チップレベルのパフォーマンスが向上します。

将来のより高性能なノードのためのSiGeFinFETテクノロジーの拡張性に焦点を当てたPouyaHashemi博士が率いる私たちの研究も、VLSIで発表されました。 T9.3の研究論文では、Geの含有量を増やし、フィンの幅を狭くし、ゲートスタックのスケーリングをさらに進めることで、より高いパフォーマンスを実現できることを報告しました。 VLSIシンポジウムの参加者は、VLSIWebサイトでこれらの技術論文を見つけることができます。詳細については、Linkedinグループに参加することもできます。

T2.2: 10nm以降の高移動度SiGeチャネルを特徴とするFINFETテクノロジー

T4.3:選択的GeO x -Si 1-x の界面層からの清掃 Ge x 高移動度Si / Si 1-x 用のチャネル Ge x CMOSアプリケーション

T9.3:交換用High-K / Metal-Gate High-Ge-Content Strained SiGe FinFETs、高い穴移動度、優れたSS、アグレッシブEOT〜7Åでの信頼性、サブ4nmフィン幅までのスケール寸法>

T7.2:先端技術用のTiおよびNiPt / Tiライナーケイ化物接点

概略図本発明の選択的GeOx掃気プロセス(a)およびSiGeチャネルを備えたGeOxフリー界面層(b)。

* -FinFETは、トランジスタチャネルを上げてフィンのように見えるトランジスタアーキテクチャを指します)

Dechao Guoは、IBM Researchの研究スタッフメンバー、マスター発明者、およびAdvanced Device Design&Integrationのマネージャーです。

ナノマテリアル

- クラウドインフィニティへ、そしてそれを超えて

- IBM at SPIE:7nmチップを超えた7つの進歩

- PoCを超えたIoT:考え方の変化

- デジタルツインテクノロジー:ロケット科学を超えて

- マシンビジョンはインダストリー4.0とIoTの鍵です

- ミズーリテクノロジーコーポレーションが州全体の起業家精神とイノベーションイニシアチブを開始

- IoTと産業自動化がイノベーションをどのように推進しているか

- コラボレーションは、ヨーロッパの高度な製造および技術(AMT)企業にとって重要です

- AMRCはテクノロジーとサーキュラーエコノミーの革新を推進します

- ABBロボティクス:技術革新とロボティクスR&D

- インダストリー4.0:5Gがスマートファクトリーイノベーションを加速