マイクロLEDおよびVCSEL用の高度な原子層堆積技術

要約

近年、ナノデバイスのプロセス要件により、半導体デバイスの規模が徐々に縮小し、その結果、エッチングによって引き起こされる無視できない側壁の欠陥が生じています。プラズマ化学気相成長法では十分なステップカバレッジが得られなくなるため、原子層堆積ALD技術の特性を使用してこの問題を解決します。 ALDは、前駆体ガスと基板表面の間の自己制限的な相互作用を利用します。反応性ガスが基板表面に吸着した化学物質の単層を形成する場合、それらの間で反応は起こらず、成長の厚さを制御することができます。 Åレベルでは、良好なステップカバレッジを提供できます。この研究では、マイクロ発光ダイオードと垂直共振器面発光レーザーのALDパッシベーションに関する最近の研究をレビューして比較しました。いくつかの不動態化方法が、光効率の向上、漏れの低減、信頼性の向上につながることが実証されました。

はじめに

原子層堆積(ALD)技術の開発は1970年代に始まりました。 1977年、フィンランドのトゥオモ・スントラ博士は、ALD技術の最初の特許を正式に申請しました[1]。 1983年から1998年の間に、ALD技術は、フィンランドのヘルシンキ空港での電子ディスプレイの製造に適用されました。 1990年代後半、半導体業界にALDプロセスが導入されたため、かなりの研究開発資金と人材が投資され、ALDプロセス技術の急速な成長に大きく貢献しました。 2007年、IntelはALDプロセステクノロジーを使用して二酸化ハフニウム(HfO 2 )45 nmマイクロプロセッサ上の金属酸化物ハーフ電界効果トランジスタに適用されたゲートパッシベーション層。これにより、半導体業界におけるALDプロセス技術の重要性がさらに強化されます[2]。

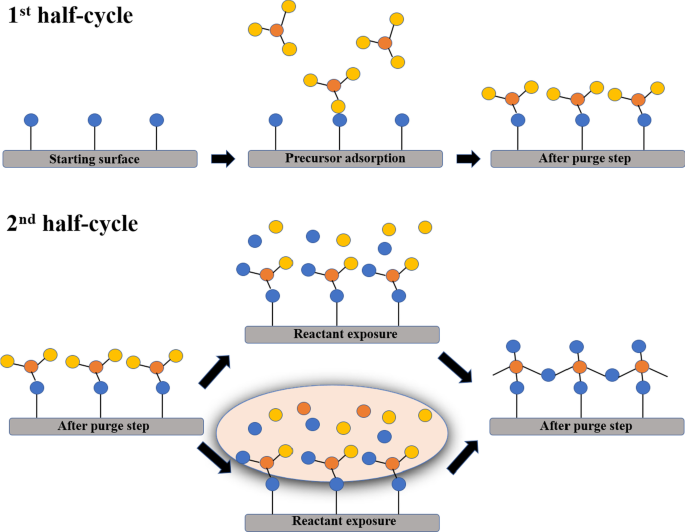

ALDは表面化学反応[3]に基づいており、優れた原子レベルの厚さ精度、大面積の高い均一性、および高アスペクト比の構造上のフィルムの適合性を特徴としています。図1に示すように、従来の化学蒸着(CVD)や物理蒸着(PVD)とは異なり、ALDプロセスでは通常2つの異なる化学前駆体を使用します。これらは異なる時間に反応チャンバーに送られ、2つの半サイクル反応を形成し、すべての化学反応は化学吸着によって表面に限定されます。単層膜の堆積を促進するALDサイクルを構成するこれらの2つの半サイクル反応は、膜を成長させるために層ごとに繰り返すことができます。これらの表面化学反応は、ALDプロセスウィンドウである自己制限反応の条件下で発生します。フィルムを堆積するために2つの半サイクル反応を使用することで、反応チャンバー内に2つの化学前駆体が同時に存在することを回避し、CVDなどの堆積モードが形成されるため、ALDテクノロジーでフィルムの厚さと均一性を正確に制御できます[4、 5,6,7]。

熱およびプラズマ支援ALDの概略図

ALDフィルムの成長率は、サイクルあたりの成長(GPC)で表されます[8、9]。一般に、GPCの厚さは0.05〜0.1nmの範囲です。化学的前駆体の選択は、フィルムの品質、その成長速度、およびプロセスに必要な時間に影響を与えます。 ALD堆積手順は、パルスA、クリーンA、パルスB、およびクリーンBの4つの連続したステップで構成されます。パルスAは金属前駆体蒸気で構成され、パルスBは非金属前駆体蒸気で構成されます。窒素またはアルゴンなどの不活性ガスおよび真空ポンプを使用して、洗浄Aおよび洗浄B中に、反応空間からガス状反応副生成物および残留反応物分子を洗浄します。堆積シーケンスには、少なくとも1つの堆積サイクルが含まれます。堆積サイクルは、堆積シーケンスが所望の厚さの膜を生成するまで繰り返される。

自己制限反応はALDのコアを形成します[10、11、12、13]。表面化学反応が自己制限条件を達成できるようにするためのプロセスパラメータ(プロセス温度、化学前駆体の選択、投与量など)の設定と調整は、ALDプロセス開発の最初のステップです。 ALDプロセスウィンドウを満たす場合、すべての化学反応は表面で発生し、自己制限条件を満たす。したがって、各ALDサイクルで十分な化学前駆体分子が導入される場合、表面化学反応に関与する化学前駆体の総量は、表面反応基の数に依存します。プロセス温度が、化学前駆体分子が物理吸着と自動熱分解の範囲内にないレベルに制御されている場合、各ALDサイクルですべての基板表面に原子層を均一に堆積させることができます。その結果、ALD技術は優れた均一性と共形能力を持ち、フィルムの厚さを減らすことができます。制御の精度は、原子レベルでの重要な要素です[14、15、16、17]。

ALDの最も重要な用途は、半導体の分野[18,19,20,21,22]であり、たとえば、high-k誘電体、金属薄膜、銅バリア膜、フィン電界用のエッチングストップ層の調製などです。エフェクトトランジスタ(FinFET)[23、24、25、26、27、28]、酸化物パッシベーション層、およびLEDとVCSEL用の反射防止層。 ALDの非常に均一な被覆率と高密度フィルム特性により、ALDは水と酸素に敏感なデバイスに適しています。したがって、ALDは、高い信頼性を必要とするデバイスの保護層に最適なコーティングツールになりました。水蒸気透過率(WVTR)は、水と酸素に対するフィルムの抵抗を測定するための重要な指標であり、特に水蒸気に敏感な柔軟な有機発光ダイオード(OLED)ディスプレイの場合です[29、30、31、 32、33、34、35、36、37]。その値は10 -4 に達する必要があります g / m 2 -日以内。その他のハイパワーVCSEL、パワーデバイス、およびハイエンドLEDの場合、それらのWVTRは少なくとも10 -3 未満である必要があります。 g / m 2 -過酷な環境での信頼性を確保するための日。したがって、これらのデバイスは、安定性を確保するためにALDパッシベーションの使用を開始しました[38、39、40、41、42、43、44]。上記のアプリケーションに加えて、太陽光発電[45,46,47]、リチウム電池[48,49,50]、燃料電池、および微小電気機械システム(MEMS)デバイスも多くのALDプロセスを使用します[6、51、 52,53]。この記事では、デバイスのパフォーマンスに対するALDテクノロジーの影響に焦点を当て、VCSELのケースを確認します。さらに、この記事では、VCSELのパフォーマンスを向上させるためのALDプロセスの概要を説明します。

マイクロLED用ALDテクノロジー

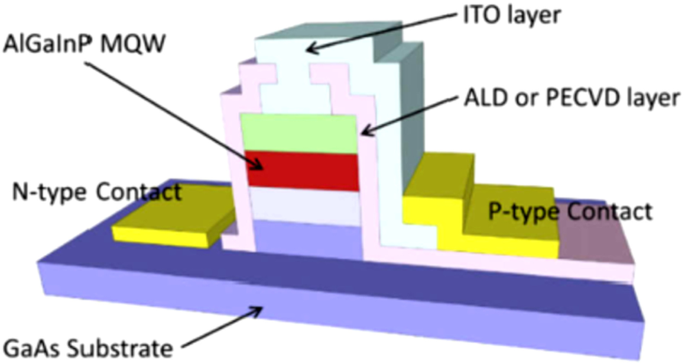

青緑色LEDは主にInGaNベースの材料で構成されています。その結晶構造のために、それは圧電材料です。強力な電界が組み込まれているため、アクティブエリアの発光波長とキャリア再結合効率に影響を与えます。この現象は量子閉じ込めシュタルク効果(QCSE)と呼ばれ、LEDの発光効率の主な理由の1つです[54]。したがって、研究チームは、緑色のエピタキシャルウェーハ上のリング状のナノ構造を介してQCSEの特性を使用しました。構造の製造により、LEDのアクティブ領域の応力が解放され、波長変調が実現されます。ナノ構造が発光領域の一部を犠牲にし、光度を低下させるため、発光波長を緑から青に変調します[55]。図2に、マイクロLED(μ-LED)の概略図を示します。 μ-LEDのサイズが小さくなると、側壁の欠陥がウェーハに与える影響が大きくなり、チップの発光効率が低下します[56、57、58]。マイクロサイズのLEDのパッシベーションは、通常、プラズマ化学気相成長法(PECVD)を使用して実現されます。これは、水素ベースの前駆体を使用して、急速な堆積速度を実現します[30、32]。マイクロサイズのLEDにはALDが推奨されます。 PECVDによって堆積されたパッシベーション層と比較して、ALDはナノメートルスケールの厚さの非常にコンパクトな誘電体膜を堆積することができます。 ALDは、コンパクトで高密度の誘電体膜を提供し、膜厚をより適切に制御することにより、μ-LEDの不動態化に有望なアプローチを提供します。そのため、多くの研究チームが、従来のPECVD法に代わるALD薄膜パッシベーション保護技術を導入しています。 Fケーラー他標準のPECVDは中程度の温度(400°C)で膜を堆積させることができますが、強い負荷効果に悩まされていると報告しています。 ALDには、低温での適合性が良好であるという利点があります。さらに、ALDは、ウェーハ間およびウェーハ内の均一性に優れています[59,60,61]。さらに、Milojevic [38]は、より小さなμ-LEDでのリーク電流の増加は、PECVDの誘電品質に起因する可能性があると報告しました。この増加により、PECVD側壁パッシベーションは、周囲長/面積比が大きいμ-LEDのリーク電流を低減するには不十分であることが明らかになりました。中村ほかは、ALDおよびPECVDを使用してΜicro-LEDに対する側壁パッシベーションの光電子効果を調査しました。これらの結果は、ALDが光学的および電気的効果の強化により有益であることも明らかにしました[62]。 ALDパッシベーション保護層は、高密度、高ステップカバレッジ、効果的な欠陥修復、およびデバイスの表面の欠陥によってキャリアがトラップされるのを防ぐその他の機能を備えています。したがって、デバイスの光度が大幅に増加し、効率が向上します[44、55、60、63、64、65、66、67]。

μ-LEDの概略図[67]

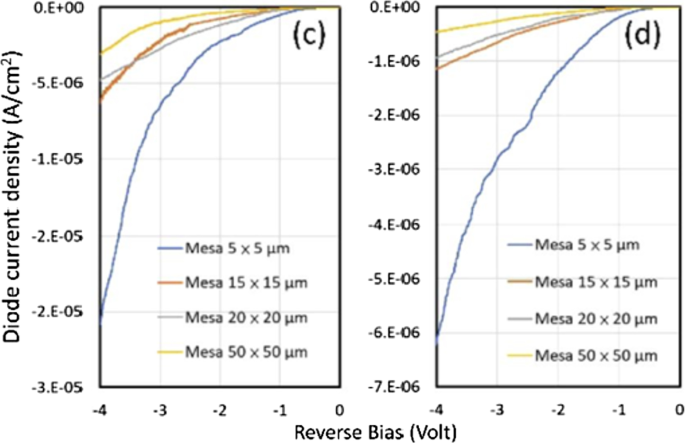

PECVDとALDによって成長したパッシベーション保護層がリーク電流に与える影響を考慮して、図3にPECVDとALDパッシベーション保護後の赤色μ-LEDのリーク電流図を示します[66,67,68]。 ALDを使用したデバイスの平均リーク電流は、PECVDを使用して得られたものよりもはるかに低いことが観察されています。さらに、小型デバイスの表面積対体積比の増加と逆バイアス下での追加のリークパスにより、コンポーネントのサイズが小さくなると、リーク電流は均一に増加します。

a の逆バイアスJ-V曲線 PECVDサンプルと b ALDサンプル[68]

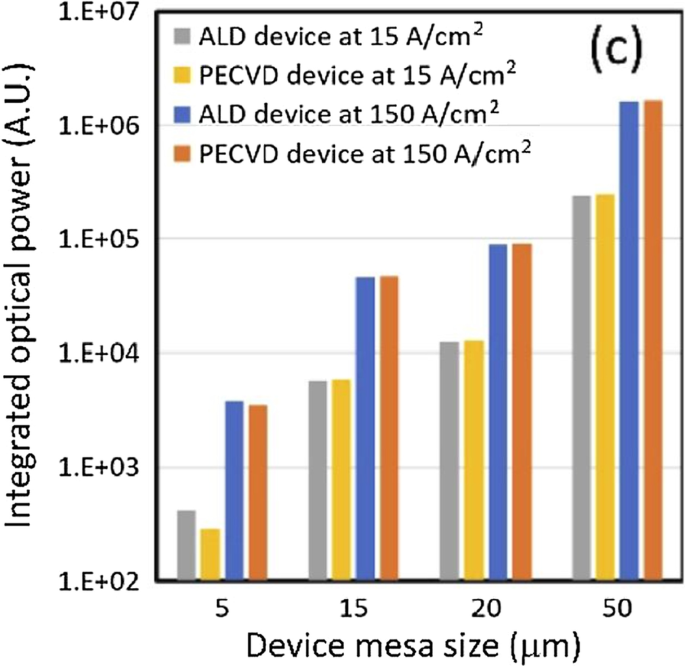

赤色光μ-LEDの光パワーに対するパッシベーション保護層の影響を説明するために、図4は、さまざまなサイズと電流密度に対するPECVDおよびALDパッシベーション保護層の光パワーを比較しています。コンポーネントサイズが15µmを超えると、PECVDおよびALDパッシベーション層の光パワーは十分なレベルに達する可能性がありますが、コンポーネントサイズが5 µm未満の場合、ALDはPECVDによって提供されるパッシベーション保護よりも優れています。異なるコーティングと異なる電流レベルのデバイス間の比較から、統合された光パワーの点で劇的な低下が観察できます。同じ電流密度と異なるサイズの下で、ALDによって提供される光パワーの差は570倍ですが、PECVDを使用するコンポーネントは850倍にもなります。これは、ALDが依然として小さなコンポーネントに優れたパッシベーションを提供することを示しています。保護層は、表面欠陥の継続的な抑制を可能にし、放射再結合効率を高めます。さらに、ALDによって提供されるパッシベーション保護により、デバイスの信頼性が向上します。ドライエッチングプロセスはサイドウォールに損傷や欠陥を引き起こす可能性があるため、デバイスのサイズを小さくすると、サイドウォールの欠陥の影響が比例して大きくなり、パフォーマンスが早期に低下する可能性があります。したがって、パッシベーション層の品質は特に重要です。上記の結果は、デバイスのサイズが縮小するにつれて、ALDパッシベーションによって保護されたデバイスのパフォーマンスがさまざまな条件下で向上することを示しています。将来の高度な製造プロセスでは、ALDテクノロジーが引き続き重要な役割を果たすことが期待されています。

高/低電流密度下でのALDサンプルとPECVDサンプル間の統合スペクトル強度[68]

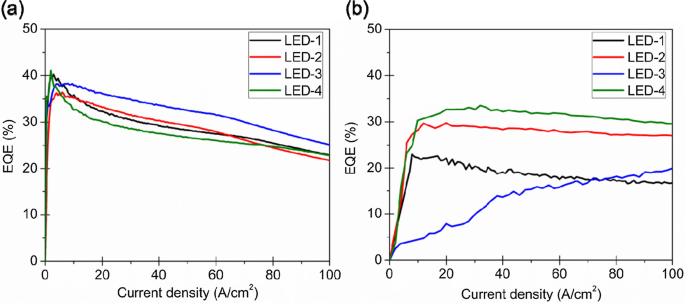

EQEの影響を考慮して、本研究では、側壁にパッシベーション層が存在することを確認し、ALDおよびPE-CVDによって生成されたパッシベーション層がEQEに及ぼす影響を次のように比較しました。側壁パッシベーションへ; LED-2:ALDサイドウォールのパッシベーションと誘導結合プラズマエッチングを受けたμ-LED。 LED-3:PE-CVD側壁のパッシベーションとHFエッチングを受けたμ-LED。 LED-4:ALD側壁のパッシベーションとHFエッチングを受けたμ-LED。図5a、bは、100×100μm 2 で得られたEQEを示しています。 および20×20μm 2 それぞれ、さまざまな側壁パッシベーション技術の効果を説明するためのデバイス。すべての不動態化された100×100μm 2 μ-LEDは同様のピークEQEを示しました(LED-1、40%、LED-2、36%、LED-3、38%、LED-4、41%)。周囲長と面積の比率が小さいため、側壁の損傷はデバイスのパフォーマンスにほとんど影響しませんでした。したがって、側壁のパッシベーションは大きなμ-LEDに大きな影響を与えませんでした。さらに、EQEは、より大きなデバイスの場合、サイドウォールの損傷による影響が少なく、サイドウォールのパッシベーションによって改善されません。 100×100μm 2 の場合 サンプルでは、使用したサイドウォールパッシベーション方法に関係なく、最大EQEは一定のままでしたが、EQEドロップは変化しました。面積が20×20μm 2 のμ-LEDの場合 、ALDパッシベーションありとなしで達成されたEQEは、それぞれ33%と24%でした。この結果は、強化された光抽出、表面の再編成、および側壁の損傷によって引き起こされるリーク電流の減少の複合効果に起因しています。

a の電流に対するEQEの依存性 100×100μm 2 および b 20×20μm 2 異なる側壁パッシベーション方法を備えたデバイス[63]

その結果、μ-LED技術はソリッドステート照明ビジネスを変える大きな可能性を秘めています、そしてそれは確かに画期的なディスプレイ技術になるでしょう。側壁のパッシベーションは、デバイスのサイズをさらに縮小して高性能に必要な信頼性を維持するために不可欠です。一般に、ALDは、漏れ電流によって特性サイズがマイクロスケールに縮小されるため、μ-LEDの効率の低下を防ぐためにサイドウォールパッシベーションを実行するための重要な手法です[69]。

VCSEL用ALDテクノロジー

酸化物VCSELには、データ伝送アプリケーションのモーダル安定性と低ジッターの向上、非ハーメチックトランシーバパッケージの低コストなど、多くの利点があります。ただし、レーザーの出力密度が高いため、酸化物VCSELには、レーザー特性の変化を防ぐためのより多くの保護方法も必要です。

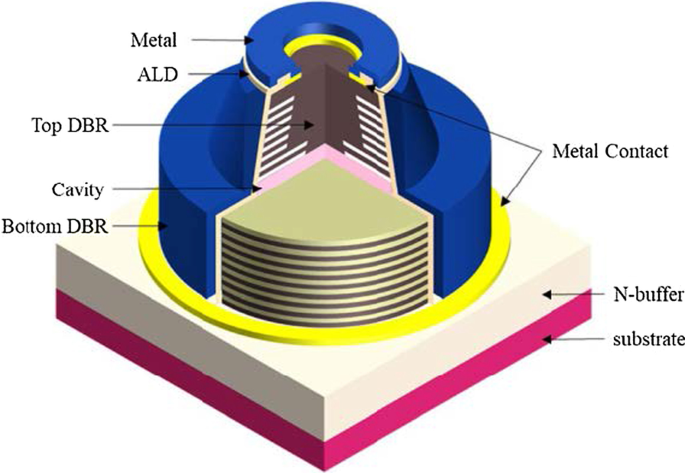

VCSELは、上部分布ブラッグ反射鏡(p-DBR)、キャビティ、下部n-DBRの3つの部分で構成されています。 DBRは、20〜40ペアの薄膜で構成されています。空洞は一般に数ミクロンの厚さです。サイドエミッタの利得長と比較して、VCSELの活性層の利得長は非常に小さい(数十ナノメートル)。放射線の誘導放出を得るには、DBRは、放射線の誘導放出が発生するための非常に高い反射率を備えている必要があります。 VCSELの特性を改善するために、ALDは、パッシベーション層、DBR、複数の量子井戸(MQW)、さらにはVCSELの透明電極を準備するために適用されています。

VCSELのパッシベーションレイヤー用のALDテクノロジー

量子ドットとLCDの信頼性を高めるためにALDが適用されており[31、32、70、71]、VCSELのパッシベーション層には、ALDの均一で緻密なコーティング薄膜が信頼性を高めることができます。 VCSELの酸化物パッシベーション層としての緻密な膜の挿入は、VCSELの空洞を保護するために非常に重要である。以前は、保護フィルムは通常PECVDを使用してめっきされていました。ただし、通常、フィルムの緻密さを維持するために厚いフィルムが必要であり、これは過度の応力を引き起こし、VCSELの信頼性に影響を及ぼします。 ALDテクノロジーはAl 2 を堆積させることができます O 3 VCSELのパッシベーション層と同様の特性を持つ薄膜、および均一で高密度のコーティング薄膜は、保護チップを完全に絶縁することができます。したがって、ALDは、VCSELのパッシベーション層に最適なコーティングプロセスとしてPECVDの代わりに使用されてきました。

酸化物VCSELの信頼性は、DBR層と比較してAl濃度が高いAlGaAsの酸化層のため、85/85(85°Cおよび85%相対湿度、RH)テストで非常に高かった。より高いAl酸化物アパーチャは、酸化物と半導体の界面での腐食剥離を引き起こしました。 Xie etal。は、湿気にさらされた酸化物VCSELのかなりの割合で、転位の成長、全体的な亀裂、および開口面の劣化が発生したことを示しました[72]。 Herrick etal。 85/85チャンバー内の湿気への暴露から生じる同様の失敗も観察されました[73]。過去20年間、多くの研究者や企業が、湿気の侵入によって引き起こされるVCSEL素子の経年劣化の防止に関する研究に投資し、幅広い保護パッシブフィルムとレイアウト設計の変更を提案してきました。たとえば、2004年に、Agilent Technologiesは、湿気への暴露を防ぐために、ポリマーにエッチングホールとフィルを提案しました[74]。 2006年にDebrabanderはメサパッシベーションフィルムのピンホール検出方法を提案し[75]、2014年にTrueLightはSiONパッシベーションフィルムを提案しました[76]。ここでは、例としていくつかの研究のみを引用します。この研究では主にAl 2 を使用しました O 3 ALDによって成長し、PECVD成長SiN x を使用して防湿パッシベーションフィルム用に積み重ねられた複合体を形成した膜 。実験を設計し、ALD層による85/85テストの失敗の改善を示すために比較研究を実施し、PECVDおよびALDによって堆積されたVCSEL構造の耐性湿気誘電体層をそれぞれデバイスAおよびデバイスBと表記しました。 。

図6は、n型DBR、MQW層、高Al含有量(〜0.98)AlGaAs酸化物アパーチャ層、p型DBR層を含むVCSELの構造を示しています。以下の説明は、ラベルに関するものです。耐湿性パッシベーション層は、酸化後にデバイスBの側壁にALDによってのみ堆積されました。

VCSELの概略図[42]

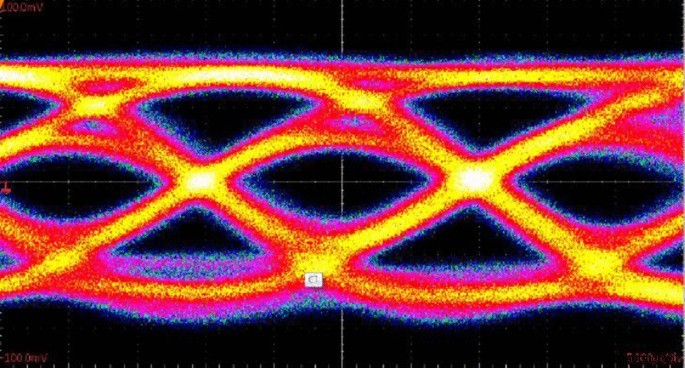

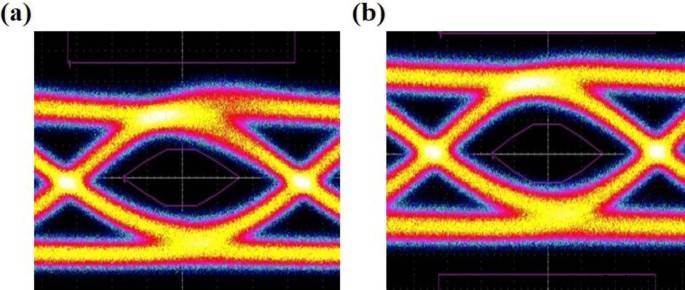

表1に、この作業と他のグループのVCSELの比較を示します。この作業では、ALDを使用した場合と使用しない場合のVCSELのLIV、S 21、アイダイアグラム、および湿式高温動作寿命(WHTOL)を調査しました。これらの結果は、ALDが高周波の光電特性と通信特性に影響を与えなかったことを示しています。高速VCSELですが、高速VCSELの信頼性を向上させます。

<図>図7に示すように、プリエンファシスNRZ-OOK変調下でのGIシングルモードファイバ(SMF)で最大100mの53Gb / sのエラーのない伝送は、いくつかの酸化物開口部の直径6μmで得られます。 -モード(FM)VCSEL。この作業では、ALDの手法を使用して、FMVCSELの信頼性を高めています。

ALD後のVCSELの酸化物アパーチャの直径6μmで最大100mの53Gb / sエラーのない伝送のアイダイアグラム

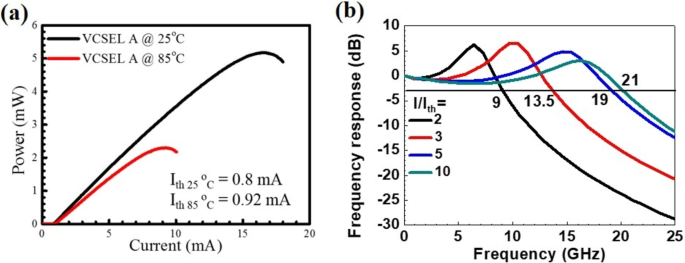

デバイスBのDC、AC、および伝送性能が示されています。図8a、bは、25°CでのデバイスBの光電流(L-I)曲線と小信号変調応答を示しています。図9は、 I のバイアス下での56Gb / sでのパルス振幅変調4レベル(PAM4)アイダイアグラムを示しています。 =25°Cで8mA。図10a、bは、 I のバイアス下での28Gb / sでのオンオフキーイング(OOK)アイダイアグラムを示しています。 =25°Cおよび75°CでのデバイスBの8mA。

a 25°Cおよび85°Cでの850nm VCSELの光電流特性、 b 25°CでのデバイスBの小信号変調応答

I のバイアスの下で56Gb / sで850nmVCSELによって送信されたPAM4信号のアイダイアグラム =25°Cで56Gb / sで8mA

I のバイアスの下で28Gb / sで850nmVCSELによって送信されたOOK信号のアイダイアグラム = a で8mA 25°Cおよび b 75°C

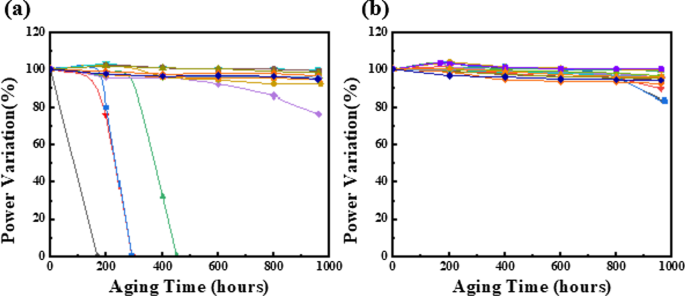

Al 2 の不動態化による耐湿性の向上を研究する O 3 ALD層、誘電体層でコーティングされた2つのデバイスが定義されました。デバイスAでは、誘電体層はSiN x のみをコーティングしました 、デバイスBにある間、Al 2 をコーティングしました O 3 ALDおよびSiN x 一緒。 SiN x 、ポリイミド、SiN x 、および金属化が順番に完了しました。最初のp-金属は、GaAsトップ材料とオーミック接触を形成しました。 2番目のp-metalはボンドパッドメタルです。複雑に積み重ねられたパッシベーションフィルムは、デバイスBのメサ表面を効率的に覆っていました。老朽化したデバイスのパッケージは、オープンカンTOで準備されました。

エージングの環境条件は85°Cおよび85%RHで、ウェット高温動作寿命(WHTOL)のバイアスは6mAでした。デバイスAとBの入力量はそれぞれ18と18でした。結果を図11に示します。デバイスAには、5つの障害チップがあり、障害は500時間以内にランダムに検出されました。デバイスBとは対照的に、960時間まで障害は発生しませんでした。結果を図11a、bに示します。これらの結果は、ALDで成長したAl 2 O 3 ALDフィルムは、PECVDで成長させたSiN x だけよりも、メサ側壁でのカプセル化が優れています。 湿気の侵入を防ぐためのフィルム。

VCSELチップのWHTOL(85°C / 85%湿度)性能、 a デバイスA、SiN x のみ パッシベーションレイヤーとして、 b デバイスB、Al 2 O 3 / SiN x パッシベーションレイヤーとして

VCSELのDBR用のALDテクノロジー

ALDによるVCSEL蒸着のDBRには、サファイア基板との良好な接着性と、DBRのさまざまな誘電体層の界面での良好な状態という利点があります[80]。 VCSELの構造によれば、レーザーの垂直方向の空洞は、活性層をクランプする2つのグループのミラーによって形成され、光はp-DBRとn-DBRの間で数回反射されてから、空気中に伝播します。 。 DBRの構造は屈折率の異なる2種類の半導体材料で構成されており、DBRの周期的な厚さはλ/ 4(λは中心波長)で正確に制御する必要があります。設計と成長の方法は、高反射率DBRの製造の基礎を形成します。高品質のDBRの場合、位相干渉効果はキャビティ内の光を強化するのに役立ちますが、DBRの高い反射率(> 99%)はVCSELのしきい値ゲインと量子効率を大幅に向上させることができます。高い反射率、広い阻止帯域、および穏やかな位相応答を実現するには、DBRの周期を20〜40の間に設定し、その製造に使用する材料の屈折率に大きな差を持たせる必要があります。この場合、多くのグループがAIA / GaAs、Al 2 O 3 、HfO 2 、SiO 2 などは、DBRの成長に適しています。

DBRには、分子線エピタキシー(MBE)や有機金属蒸着(MOCVD)など、さまざまな成長方法があります。ただし、ALDはDBRの正確な成長方法でもあります。厚みが薄く、反射率が高く、粗さが小さいALDで作製したDBRは、VCSELの特性を効果的に向上させることができるため、多くの研究者がALD技術を用いてDBRを強化する技術を研究してきました。たとえば、1997年にHuffaker [81]は、Al x を使用することで、DBRが低いことによるひずみを減らすことができると提案しました。 O 1-x 厚さが1/4波の層よりも薄い層。 2013年、Guo etal。 [82]は、ALDプロセスによって作成されたDBRは、EBEによって作成されたものよりも優れた品質を示し、ALDプロセス時間はEBEプロセスとほぼ同じかそれ以下であると報告しました。さらに、少なくとも2種類以上の材料で構成されるDBRを成長させるには、一般にEBEプロセスで頻繁に温度を上げ下げする必要がありますが、異なる材料を堆積するALDプロセスでは温度を同じに保つことができます。 2017年、Liu [83]は、ALD法を適用して、シャープな界面と優れた均一性を備えた高品質の層を作成できると報告しました。したがって、ALDは高品質のDBRを預けるのに適しています。

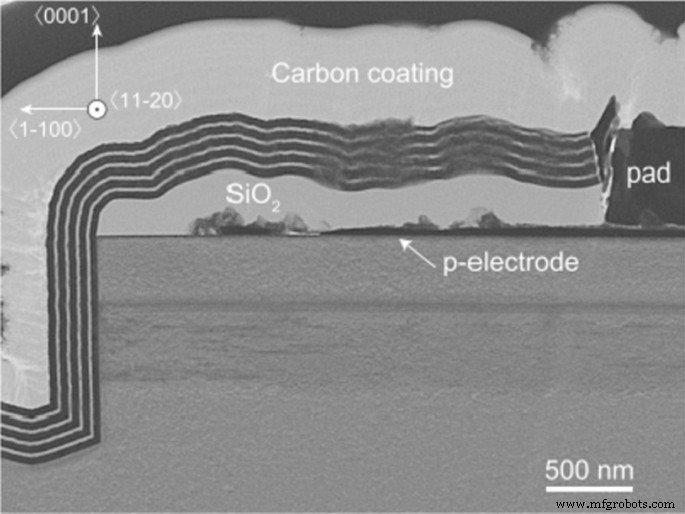

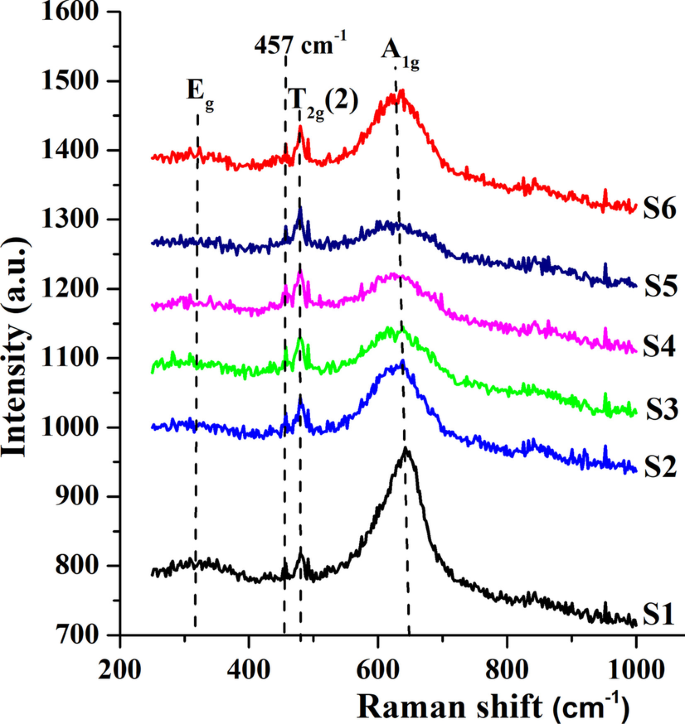

たとえば、酒井ら。レーザー発振しきい値電流密度の低減に寄与する、ALD蒸着DBRを備えたエッチングミラーUV-Cレーザーダイオード(LD)のオンウェーハ製造を提案しました。この研究では、HfO 2 の4つの期間 およびAl 2 O 3 DBRにALDを使用して寄託されました。 Al 2 O 3 堆積速度がSiO 2 よりも著しく高いため、低屈折率材料として選択されました。 。図12は、ALDによって堆積されたDBRのTEM画像を示しています。これは、DBRの優れた厚さと品質を示しています。

ALDで堆積されたDBRのTEM画像[84]

MOCVDの技術は、膜の正確な成長制御や高品質の膜の堆積など、多くの利点のためにDBRの堆積に広く使用されています。ただし、実際の製造プロセスでは、DBRのさまざまな誘電体層の界面で界面状態が影響を受けます。そうでなければ、DBRの設計方法では、異なる誘電体層の界面に別の追加のバッファ層を堆積するなど、複雑な最適化が必要になります。図13aは、バッファ層を挿入せずにMOCVDを使用したDBRの反射率の転送行列法(TMM)の計算を示しています。 HfO 2 の反射スペクトル / Al 2 O 3 ALDで堆積されたDBRは、図13bで計算されたTMMスペクトルとより一致しています[85]。この場合、ALDの手法により、MOCVDと比較して異なる誘電体層間の界面が良好なDBRを堆積させることができます(図14)。

a で堆積された設計DBRの測定および計算された反射スペクトル MOCVD、 b ALD [84、85]

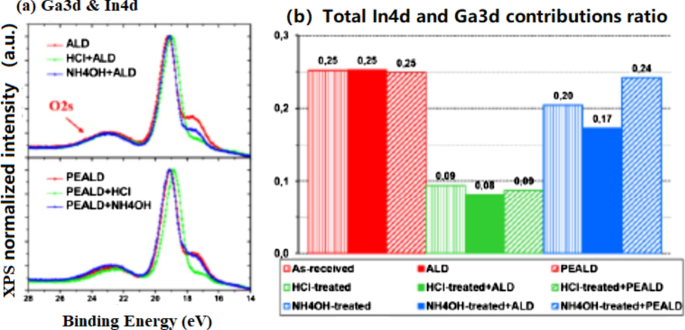

a ALDおよびPEALDサンプルの正規化されたGa3d-In4dスペクトルの重ね合わせ(HClあり、HClあり、またはNH 4 あり) OH表面処理、 b Al 2 と比較した同じサンプルのGa3d-In4d比 O 3 自由表面[86]

ALD Technologies for the Multiple Quantum Wells of VCSELs

Owing to the high requirement for optical gain in VCSELs, most devices use MQWs as the active region. In general, when the MQW period increases to a certain value, the threshold current density of the VCSEL is mainly caused by the following three factors. First, for the width of the quantum well, the active region cannot overlap with the peak position of the waveform. The farther the quantum well from the peak position, the lower is its gain efficiency. Therefore, distant quantum well regions cannot play a significant role in improving the optical gain. Second, there is a direct proportional relationship between the total transmittance current and period of MQWs. The total transmittance current increases with the MQW period because the transmittance current is a part of the threshold current of the device. Therefore, the threshold current of the device will increase with the transmittance current. Third, as the current increases, the slope of the optical gain to current curve will decrease, increasing the threshold current of the device. Hence, thin MQWs with high crystalline quality and optical properties are promising candidates for realizing VCSELs.

For the MQWs of VCSEL, ALD can optimize the interface properties and surface recombination of MQWs [80, 83,84,85]. In the last several decades, methods for optimizing MQWs using ALD have been studied. In 2008, Lo et al. reported the successful growth of high-quality ultraviolet (UV) AlGaN/GaN MQWs structures using ALD [87]. In the same year, Bosund et al. [88] proposed that a thick TiN passivation layer deposited by ALD on top of InGaAs/GaAs can significantly increase the photoluminescence intensity and carrier lifetime of the MQWs, while Li et al. reported that a low dislocation density ultraviolet (UV) AlGaN/GaN MQW structure can be grown using the ALD technique. In 2019, Lee et al. [89] proposed that the emission intensity of the 860 nm GaAs VCSEL with SiN anti-reflection film was significantly increased (compared to the VCSEL without the SiN anti-reflection film) to improve the light extraction efficiency of a VCSEL. Here, we cite a few studies as examples.

A deep understanding of semiconductor–dielectric interface properties will provide guidelines for optimizing efficient passivation solutions for InGaN/GaN-based µ-LEDs. To this end, quantum well (QW) semiconductors are of tremendous interest because many surface recombinations are likely to occur at the edges of the LED active regions and are probably responsible for the low µ-LED efficiencies. Thus, Le Maoult et al. [86] studied the X-ray photoemission (XPS) and wavelength dispersive X-ray fluorescence (WDXRF) characteristics of In0.1 Ga0.9 N surfaces after acid, base, or sulfur-based chemical treatments followed by ALD of Al2 O3 thin films with TMA/H2 O or TMA/O2 plasma (plasma-enhanced ALD) at 250 °C.

The ALD of Al2 O3 with H2 O as a weak oxidizer does not seem to significantly modify the InGaN surface. Indium depletion occurs as the In4d intensity decreases, as observed previously in the case of the HCI or NH4 OH-treated surfaces only (upper portion of Fig. 15a, b). On the contrary, during the PEALD of A12 O3 (strong oxidizer), the NH4 OH-treated surfaces changed compared to HCl because the In4d component level is indistinguishable from the PEALD reference (as illustrated by Fig. 15a, bottom, and 15b). Then, if indium is assumed to be the main species sensitive to plasma-induced oxidation, the indium-depleted surfaces after HCI treatment would indeed remain in a stable state of oxidation regardless of the ALD or PEALD process. On the contrary, a higher proportion of indium from the NH4 OH-treated surfaces is more likely to be oxidized by the plasma species.

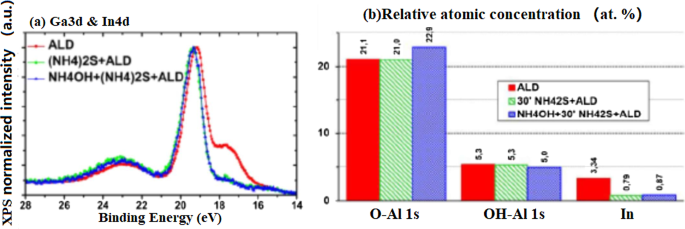

a Superposition of normalized Ga3d-In4d spectra for ALD and PEALD samples without, with a 30’ (NH4 )2 S or with a NH4 OH + 30’ (NH4 )2 S surface treatment, b proportion of O1s components and total indium contribution using In4d line [86]

If a 30' (NH4 )2 S surface treatment with or without prior treatment with NH4 OH is performed before ALD, the quantitative analysis seems to report (Fig. 15b) results similar to those observed previously without the alumina layer. As an example, a similar decrease in the indium proportion was observed (~ 75%). However, a slight increase in the O–Al-related component from the O1s line was observed for the sample that underwent the double surface treatment, probably owing to the increased surface hydrolysis by the first NH4 OH treatment. Thus, ALD does not seem to significantly modify the initial state of the (NH)S-treated surfaces. However, these results do not provide quantitative information regarding the proportion of sulfur after the deposition of Al2 O3 by ALD. Considering that sulfur was adsorbed on InGaN before deposition, further investigations are required to determine the evolution of sulfur bonds after ALD of Al2 O3 , especially if binding state differences with stronger oxidizing processes such as PEALD are evident.

ALD Technologies for the Transparent Electrode of VCSEL

For the transparent electrode of VCSEL, ALD can deposit the electrode with high transparency and good current spreading properties [90]. In terms of the current spreading of the conventional VCSEL, the metal electrode has good current spreading properties, but strongly absorbs the emitted light. Hence, the conventional VCSEL relies on the upper heavily-doped layer for current spreading. However, since the upper heavily-doped layer has poor current spreading performance and absorbs part of the emitted light, the light output power of the device is lowered. Therefore, a transparent conductive oxide (TCO) film deposited by ALD, exhibiting excellent photoelectric performance, can solve the current spreading problem described above.

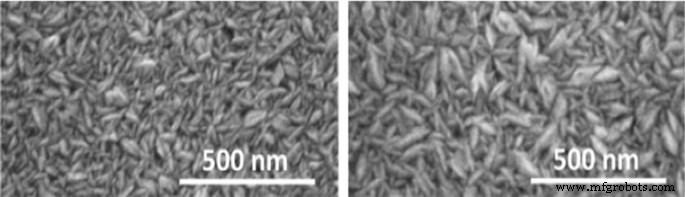

Figure 16 shows the SEM images of ZnO films deposited on Si with ALD and CVD modes as the transparent conductive materials, which can be applied to new-generation photovoltaic devices. So far, there are few studies and reports on the application of TCO films in VCSEL devices. At present, the indium tin oxide (ITO) films are used in VCSEL devices. In 1997, C. L. Chua et al. [91] first reported the top-emitted VCSEL with a transparent tin oxide electrode. In this study, the peak transmittance of ITO is 96%. In 2002, Jiang et al. [92] studied the P-type ohmic contact of ITO as an 850 nm GaAs-based oxide restricted type VCSEL. In comparison with VCSELs with traditional Ti/Au contact, they found output power of the VCSEL with ITO contact is 1.27 times higher than the VCSEL with T/Au contact. In 2014, Meng et al. [93] found that the output power of the 850 nm GaAs oxide-confined VCSEL with an ITO transparent conductive film is 1.18 times higher than the traditional VCSEL.

SEM images of ZnO films deposited on Si using ALD and CVD [90]

At present, the commonly used techniques for preparing TCO are magnetron sputtering, pulsed laser deposition, CVD, ALD, etc. However, it is difficult to achieve large-scale and large-area film formation using magnetron sputtering, the film deposited by pulsed laser deposition is uniform, and it is difficult to prepare large-area films while the deposition temperature for CVD is high, which renders it unsuitable for some devices that need to be prepared at low temperature. ALD possesses the advantage of highly controllable deposition parameters and the film deposited by it is characterized by good uniformity, absence of pinholes, and excellent shape preservation for film graphics. In this case, the oxide (TCO) film deposited by ALD can improve the properties of VCSELs.

Conclusions

This article reviews the application of ALD technology to the optoelectronic devices, µ-LEDs and VCSELs. Since sidewall damage is prominently observed in μ-LEDs when their sizes are reduced to the microscale level, this issue must be addressed to achieve high device performance. ALD sidewall passivation is a crucial technique because the sidewall damage can be reduced after passivating a surface with an ALD-grown dielectric. ALD passivation has also been found to help in protecting the quantum dot (QD) conversion layer in full-color displays. Different approaches involving the deposition of passivation layers have been established for reducing sidewall damage. In addition, an 85 °C/85% RH test with bias, which is a very difficult challenge for oxide-confined VCSEL devices, was conducted. In this study, we demonstrate that complex stacked dielectric layers as passivation films resist moisture ingress. The stacked passivation layers consist of Al2 O3 growth by ALD film and SiNx growth by PECVD film. A very good encapsulation that prevented damage from moisture and excellent reliability was observed. In addition, the effects of ALD on the accurate control of DBR growth are specified. This technique has also been found to enhance the optical properties of MQWs, such as the deposition of an anti-reflection layer for improving the light extraction efficiency of a VCSEL and the accurate control of the growth of MQWs for improving its crystalline quality. In addition, because the output power of the VCSEL with an ITO transparent conductive film exceeds that of the traditional VCSEL, this study addresses the potential applications of ALD for preparing the TCO films of VCSELs.

データと資料の可用性

The data used and analyzed during the current study are available from the corresponding authors upon reasonable request.

略語

- PECVD:

-

Plasma-enhanced chemical vapor deposition

- ALD:

-

Atomic layer deposition

- LED:

-

Light emitting diode

- VCSEL:

-

Vertical cavity surface emitting laser

- CVD:

-

Chemical vapor deposition

- PVD:

-

Physical vapor deposition

- GPC:

-

Growth per cycle

- HKMG:

-

High-K metal gate

- FinFET:

-

Fin field-effect transistor

- WVTR:

-

Water vapor transmission rate

- OLED:

-

Organic light-emitting diode

- MEMS:

-

Micro-electro mechanical systems

- μLED:

-

Micro-LED

- WHTOL:

-

Wet high-temperature operation life

- OOK:

-

On–off keying

- PAM4:

-

Amplitude modulation 4-level

ナノマテリアル

- 三菱ケミカルアドバンスドマテリアルズは、2023年までに気候ニュートラルを、2030年までに気候陽性を目指す

- 原子層堆積によって製造されたPtおよびTiNコーティング基板上のHfO2 / TiO2 / HfO2三層構造RRAMデバイスのバイポーラ抵抗スイッチング特性

- プラズマ化学原子層堆積によるその場で形成されたSiO2中間層を有するHfO2 / Geスタックの界面、電気、およびバンド整列特性

- 原子層堆積と水熱成長によって製造された抗菌性ポリアミド6-ZnO階層型ナノファイバー

- プラズマ化学原子層堆積によって調製されたCo3O4被覆TiO2粉末の光触媒特性

- 超循環原子層堆積によるZnO膜のフェルミ準位調整

- 高度なナトリウムイオン電池のアノード材料としてのCuGeO3ナノワイヤの合成と調査

- c面GaN上に堆積した原子層AlNの界面および電気的性質への厚さ依存性

- コンピュータとバッテリー用の高度な冷却システム

- クーラントチャネル閉鎖のためのクラッディングとフリーフォーム堆積

- コンポーネントおよびアセンブリ用 SIGRABOND® Chemical CFRP