セレクタおよびメモリとしてのV / SiOx / AlOy / p ++ Siデバイスの二重機能

要約

このレターは、V / SiO x でのセレクターとメモリスイッチングを含む2つの機能を示しています。 / AlO y / p ++ コンプライアンス電流制限(CCL)を制御するだけのSi抵抗変化型メモリデバイス。 1μAの低いCCLでポジティブフォーミングを行った後、一方向のしきい値スイッチングが観察されます。酸素のV電極側へのシフトは、VO x を形成します しきい値の切り替えは、金属絶縁体転移現象によって説明できます。デバイスに適用されるより高いCCL(30μA)の場合、バイポーラメモリスイッチングが得られます。これは、SiO y での導電性フィラメントの形成と破壊に起因します。 層。 1.5nmの厚さのAlO y 熱伝導率の高い層は、メモリとしきい値の切り替えのオフ電流を下げるのに重要な役割を果たします。温度依存性により、LRSの高エネルギー障壁(0.463 eV)が確認され、低抵抗状態で非線形性が発生する可能性があります。 CCLが小さいほど、非線形性が高くなり、クロスポイントアレイのアレイサイズが大きくなります。 CCLに従ったメモリとしきい値の切り替えの共存により、デバイスをその意図された用途に合わせて制御する柔軟性が提供されます。

背景

抵抗変化型メモリ(RRAM)は、スイッチング速度が速く[1、2]、消費電力が少ない[3,4,5,6,7]ため、次世代の不揮発性メモリテクノロジの有望な候補の1つです。 、8]、マルチレベル機能[9,10,11,12,13,14,15]、高スケーラビリティ[16,17,18,19,20]、および3Dスタッキング機能[21,22,23,24,25 ]。これらのプロパティは、メインメモリとしてのダイナミックランダムアクセスメモリ(DRAM)とストレージメモリとしてのソリッドステートドライブ(SSD)の間のパフォーマンスギャップを埋めることができるストレージクラスメモリ(SCM)に特に適しています。 RRAMデバイスは過去数年間で大きな進歩を遂げましたが[1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18,19 、20、21、22、23、24、25]、しかし、大きな欠点が残っています。隣接するセルを通るスニーク電流が高密度クロスポイントアレイで発生します[26]。セレクタコンポーネントを備えたメモリデバイスは、この問題を克服するために非線形電流-電圧(I-V)特性を提供する必要があります[26、27、28、29、30、31、32、33、34、35]。これまで、相補抵抗スイッチング(CRS)[26]、トンネルバリア[27,28,29,30,31,32,33]、Agベースのしきい値スイッチング[34]、ダイオードタイプなどの非線形概念を持つさまざまなデバイスセレクター[35、36]、オボニックスレッショルドスイッチング(OTS)[37、38]、および金属-絶縁体転移(MIT)[39,40,41,42,43]が報告されています。 VO x 典型的なMIT材料の1つとして、光および電気スイッチングコンポーネントとして潜在的なアプリケーションで広く使用される可能性があります[40、41、42]。 SiO 2 半導体業界でパッシベーション層として広く使用されています。さらに、Siが豊富なSiO x ( x <2)はRRAMの抵抗変化層として使用できます[44、45、46、47、48、49、50、51、52、53、54、55]。 SiO x CMOSプロセスとの互換性と低コストの点で、他の多くの材料よりも優先される可能性があります。 SiO x ベースのRRAMデバイスは、拡散性の高いCuやAgなどの電極を使用するだけでブリッジを伝導する役割のメディエーターとして機能することが報告されています[44、45、46、47]。別のケースでは、メモリの切り替えは、SiO x 内の原子価変化効果によって引き起こされます。 層。これは、酸素空孔の生成またはプロトン交換モデルによって説明できます[48、49、50、51、52、53、54、55]。集合演算がリセットに先行するユニポーラスイッチングでは、周囲の雰囲気に敏感です。空中でのスイッチング性能は大幅に低下します[48、49、50、51、52、53]。一方、後方スキャン効果のないフィラメントスイッチングは、さまざまなSiO x での典型的なユニポーラおよびバイポーラスイッチングを示しています。 ベースのRRAMデバイス[52,53,54]。

ここでは、V / SiO x におけるしきい値スイッチングとメモリスイッチングの共存について説明します。 / AlO y / p ++ コンプライアンス電流制限(CCL)に依存するSiデバイス。シリコン底部電極(BE)を備えたデバイスには、従来の金属電極と比較していくつかの利点があります。メモリまたはスレッショルドスイッチングを備えたRRAMデバイスは、トランジスタのソース側またはドレイン側に直接接続されます。これは、組み込みメモリおよび急勾配デバイスの潜在的なアプリケーションです。 Si BEの直列抵抗により、オーバーシュート電流を低減できます。さらに、ウェットエッチングによるシリコンBEのナノチップとシリコン表面のドーピング濃度の調整により、スイッチング性能を向上させることができます。 AlO y 絶縁性を備えた大きなバンドギャップである層は、スレッショルドおよびメモリスイッチング中の動作電流を下げるのに役立ちます。 SiO x 層は、高CCLでメモリスイッチング層として機能し、低CCLでV TEに酸素を供給し、しきい値スイッチングを提供します。

メソッド

V / SiO x / AlO y / p ++ Siデバイスは次のように製造されました。まず、BF 2 イオンは、40keVの加速エネルギーと5×10 15 の線量で注入されました。 cm −2 高濃度にドープされたSiBEへのSi基板への変換。格子損傷は、1050°Cで10分間のアニーリングプロセスによって修復されました。高濃度にドープされたSiBEのシート抵抗は30.4Ω/□でした。次に、厚さ1.5nmのAlO y 層は、H 2 を使用した原子層堆積(ALD)システムによって堆積されました。 OとAl(CH 3 ) 3 厚さ5.5nmのSiO x 層は、5%SiH 4 を反応させることにより、プラズマ化学気相成長法(PECVD)を受けました。 / N 2 (160 sccm)、N 2 O(1300 sccm)、およびN 2 (240 sccm)300°Cで。続いて、直径100μmの厚さ50 nmのバナジウム(V)上部電極(TE)が、Arガス(30 sccm)を使用してVターゲットをDCスパッタリングすることによって堆積されました。最後に、保護層としての厚さ50 nmのAlを、VTEのさらなる酸化を防ぐためにDCスパッタリングによって堆積させました。すべての電気的特性は、Keithley 4200-SCS半導体パラメーターアナライザー(SPA)および4225-PMU超高速電流-電圧(I-V)モジュールを室温で使用して、DC電圧スイープおよびパルスモードによってそれぞれ特徴付けられました。デバイスの動作については、TiN BEを接地し、NiTEバイアスを制御しました。

結果と考察

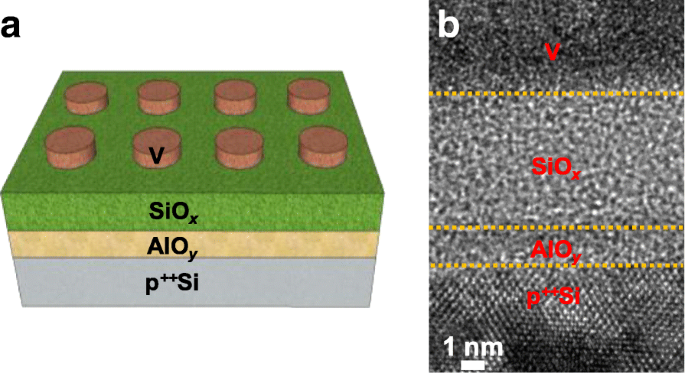

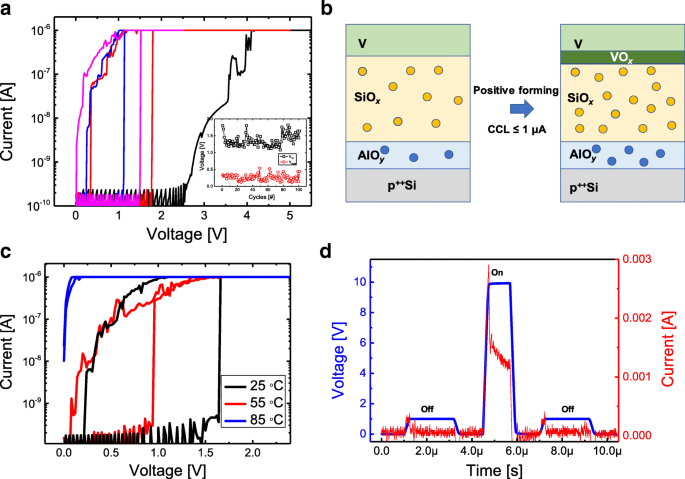

図1aは、V / SiO x の概略構造を示しています。 / AlO y / p ++ Siデバイス。 3つのアモルファスV、SiO x 、およびAlO y 図1bに示すように、層と単結晶Si層は、透過型電子顕微鏡(TEM)の断面画像で観察されます。 SiO x の厚さ およびAlO y レイヤーはそれぞれ5.5nmと1.5nmです。 2つの誘電体膜の組成比を確認するために、XPS分析を実施しました(追加ファイル1)。 x SiO x の値 と y AlO y の値 それぞれ0.88と1.33です。私たちのSiO x SiO 2 と比較したPECVDを使用したフィルム 乾式酸化を使用して堆積されると、はるかに低い温度で堆積され、はるかに多くの欠陥があり、比較的低い電圧での抵抗スイッチングに適しています。図2aは、V / SiO x の一般的なしきい値スイッチングを示しています / AlO y / p ++ Siデバイス。誘電体層の欠陥は最初は小さいため、ポジティブフォーミングプロセスによる最初のスイッチングでは、後続のしきい値スイッチングよりも高い電圧が必要になります。 1μAのCCLがデバイスに適用され、SiO x での過剰な導電性フィラメントの形成を回避します。 層。以前に報告されたVO x のしきい値スイッチングと比較して、リーク電流は非常に低くなっています(1Vで100pA)。 。この利点は、Al 2 に起因します。 O 3 SiO 2 と比較して誘電率と熱伝導率が高い 。フィラメントが容易に破裂し、フィラメントが残っていないため、オフ状態には絶縁性があります。しきい値切り替えの考えられるメカニズムは、SiO x から供給される酸素からのVTEの酸化です。 図2bに示すように、ポジティブフォーミングプロセス中の層。 VO x の電気的特性 VTEとSiO x の間 層が絶縁状態から金属状態に変化し、抵抗が急激に変化する場合があります。 1μAの低いCCLは、SiO x 内に効率的な導電性フィラメントを発生させるのに十分ではありません。 映画。したがって、SiO x 絶縁性を備えていることは、オフ電流を減らす別の原因となる可能性があります。 V / SiO x のネガティブフォーミングプロセスの場合 / AlO y / p ++ Siデバイスの場合、しきい値の切り替えは観察されません(追加ファイル1を参照)。負のバイアスがVTEに印加されると、酸化物の動きがSi BEに向かって移動するため、VTEはVO x としてしきい値スイッチングに参加できなくなります。 。図2aの挿入図は、しきい値電圧(V th )およびホールド電圧(V hold )100サイクル中。 V th ここで、電流はほぼ無限の傾きで急激に増加し、1.08〜1.82 Vであり、V hold この時点で、高抵抗状態に戻る電流は0.12〜0.54 Vです。図2cは、さまざまな温度でのオン電流のI–V特性を示しています。 25°Cと55°Cでは、ほぼ同様のしきい値スイッチングを示しますが、85°Cの高温でのI-V曲線は、しきい値スイッチング特性を失います。 VO x であることはよく知られています 高温でMITを失います。したがって、この結果は、VO x のもう1つの証拠です。 しきい値の切り替えの主な原因です。図2dは、しきい値スイッチングの過渡特性を示しています。振幅1Vのパルスは、幅1μsのパルスを書き込む前後の読み取り電流を監視しました。高振幅のパルスがデバイスに印加されている間、高電流が監視され、次にV / SiO x / AlO y / p ++ Siデバイスは、書き込みパルスが除去された直後に電流をオフにしました。上で分析したセレクターのプロパティは、1μA未満のメモリ要素の操作と組み合わせると使用できます[55、56]。

V / SiO x のデバイス構成 / AlO y / p ++ Si。 a 概略図と b TEM画像

V / SiO x の一方向しきい値スイッチング / AlO y / p ++ 1μAのCCLでポジティブフォーミングを適用した場合のSi。 a 典型的なI–V曲線。 b 成形工程の概略図。 c 温度依存性によるI–V特性。 d 過渡特性

図3aは、V / SiO x のバイポーラ抵抗スイッチングを示しています。 / AlO y / p ++ 100μAのCCLでポジティブフォーミングした後のSiデバイス。次に、負の電圧をスイープすることにより、抵抗が急激に増加するリセットプロセスが実行され、デバイスが高抵抗状態(HRS)に切り替えられます。次に、抵抗が急激に減少するセットプロセスが正のバイアス電圧で発生し、デバイスが低抵抗状態(LRS)に戻ります。導電性フィラメントの特性を理解するために、正規化されたコンダクタンスと温度依存性を観察します。 LRSの伝導は、伝導フィラメントの特性を間接的に通知するための重要なガイドラインです。図3bは、正規化されたコンダクタンス(G N )これは動的コンダクタンス(G d )静的コンダクタンスで除算します(G 0 )V / SiO x のI–V曲線の場合 / AlO y / p ++ 異なる温度のLRSのSiデバイス。温度に関係なく、G N 電圧がゼロのとき、値は1に収束します。これにより、Schottky放出、Fowler-Nordheimトンネリング、Child’s law(I〜V 2 などのよく知られた伝導メカニズムを除外できます。 )空間電荷制限電流(SCLC)で。図3cに示すように、温度依存性を考慮して、金属オーム伝導も除外できます。温度の上昇に伴う抵抗の減少は、導電性フィラメントが半導体特性を持っていることを示唆しています。したがって、VのSiO x への浸透を除外できます。 V / SiO x の主導電性フィラメントの層 / AlO y / p ++ LRSのSiデバイス。したがって、V / SiO x のバイポーラメモリ動作 / AlO y / p ++ Siデバイスは、SiO x の固有のスイッチングによって支配されます 。また、正電流と負電流にそれほど差がないことも確認されており、ショットキー発光などの界面型ではなく、バルク伝導が支配的であることを示唆しています。上記の正規化されたコンダクタンスを考慮に入れると、2つの可能なバルク支配伝導メカニズムがあります。 1つ目は、次の式に従って伝導をホッピングすることです。

$$ J ={qnav} _o {e} ^ {-q {\ o} _T / kT} {e} ^ {qaV / 2 dkT} $$

V / SiO x のメモリスイッチング / AlO y / p ++ 30μAのCCLでポジティブフォーミングを適用した場合のSi。 a 典型的なI–V曲線。 b 正規化されたコンダクタンス。 c (I)対1000 / T。 d 成形プロセスの概略図

ここで、 q 、 n 、 a 、ø T 、 v o 、および d は、それぞれ、電荷、空間電荷の集中、ホッピング距離の平均、ホッピングの電子障壁の高さ、固有振動周波数、および誘電体膜の厚さです。 ø T 図3cに示すように、ln(I)対1000 / Tの線形プロットの傾きから計算すると0.463eVです。 E a 間の関係から計算された値 Vは5.17nmで、SiO x に形成された導電性フィラメントを示します。 強くなく、HRS状態に近いです。もう1つの伝導メカニズムであるPoole-Frenkel(P-F)放出については、追加ファイル1で説明しました。上記の結果に基づいて、V / SiO x のメモリ操作における伝導フィラメントモデル / AlO y / p ++ Siデバイスを図3dに示します。ポジティブフォーミングプロセスでは、酸化プロセスはV TE側で進行しましたが、CCLが高いため、SiO x の内部に導電性フィラメントを形成できます。 およびAlO y 酸素空孔の動きによる。リセットプロセス中、形成と硬化の反対側の電界が酸素を誘導し、酸素空孔と再結合して、導電性フィラメントを破壊します。セレクターとメモリーの操作は同じセルで観察されることに注意してください。スレッショルド動作が発生し、スイッチが完全にオフになった後、メモリ動作が可能になります。ただし、メモリ動作のリセット切り替えが完全にオフになっていないため、逆方向にはできません。

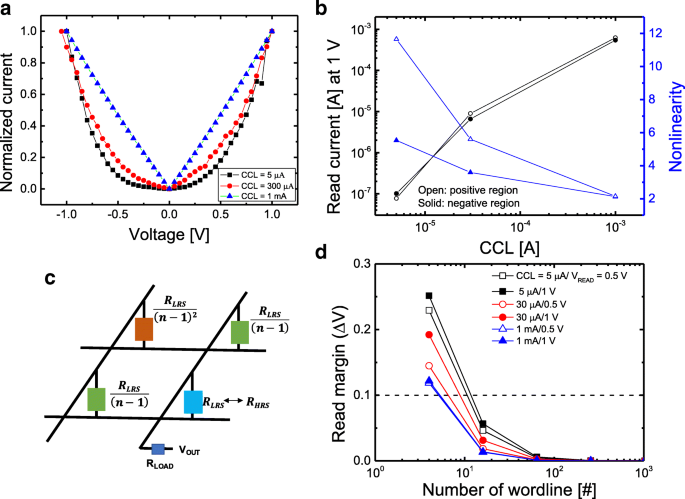

図4aは、V / SiO x のLRSにおける正規化されたI–V曲線を示しています。 / AlO y / p ++ さまざまなCCL条件(5 µA、30 µA、および1 mA)に対する低電圧レジーム(0〜1 V)のSiデバイス。ここで、正規化されたI–V曲線は、各電圧での電流を1 Vでの電流で割ったものとして定義されます。CCLに応じてLRS電流のレベルが変化するため、電流値を1 Vに設定して、非線形性。 CCLが減少すると、低電圧領域で電流が抑制されることがわかります。より定量的な関係を導き出すために、非線形性はV READ での電流の比率として定義されます。 V READ の半分でそれに 。図4bは、1Vでの読み取り電流とV / SiO x のCCLの関数としての非線形性を示しています。 / AlO y / p ++ Siデバイス。 CCLの減少による読み取り電流の減少は、導電性フィラメントが細くなり、非線形性が増加していることを示しています。真性酸化ケイ素膜は、単層でも高い非線形性を示します。固有の非線形特性は、シリコンの界面ではなく、酸化シリコンのバルク性によるものです。 CCLが小さいほど、SiO x で発生する劣化が少なくなります。 したがって、HRSのトラップエネルギーレベルと比較したLRSのトラップエネルギーレベルの低下を最小限に抑えることができます。したがって、より低いCCLがデバイスに適用される場合、より高いエネルギー障壁はLRS状態の非線形性を最大化できます。同様に、TaO x のP-F放出によって記述される伝導 / TiO y スタックは高い非線形性を保証します[57]。もう1つの可能性は、酸化物の誘電率が小さいため、電界の集中によって酸化物膜へのパスが多くなることです。これにより、酸化物層のトラップエネルギーレベルが低下する可能性があり、Al 2 のトンネルバリアとして機能することが期待できます。 O 3 。 n の読み取りマージン(ΔV)を取得するには × n クロスポイントアレイでは、図4cに示すように簡略化された等価回路を使用します。最悪の場合を考慮して、隣接するセルはLRSと負荷抵抗(R L )に設定されます。 )LRS抵抗に。 ∆Vは、V OUT 間の差から計算されました。 LRSおよびV OUT で HRSで。図4dは、ワード行数( n )の関数としてのΔVを示しています。 )V / SiO x の場合 / AlO y / p ++ Siデバイス。 CCLが小さいほど、非線形性が増加するため、ΔVは高くなります。 10%の読み取りマージンが確保されると、アレイは5μAのCCLの場合は約10×10を超え、1mAのCCLの場合は5×5に拡張できます。スニーク電流に耐えるアレイサイズでは不十分ですが、セレクタ機能付きのデバイスをV / SiO x に接続すると、アレイサイズを拡大するのに役立ちます。 / AlO y / p ++ Siデバイス。すべてのCCLでの0.5Vの読み取りと比較して、1Vでの読み取りでは非線形性が高くなります。ただしV READ は低くなります。 読み取り操作での静電気電力が低くなると、非線形性の値が小さくなります。これは、SiO x の電界が小さいためです。 / AlO y 小さいV READ のレイヤー 。

V / SiO x の非線形特性 / AlO y / p ++ メモリスイッチング用のSi。 a 異なるCCLのI–V曲線。 b CCLの関数として電流と非線形性を読み取ります。 c クロスポイントアレイの等価回路。 d さまざまなCCLおよび読み取り電圧のワード行番号の関数としての読み取りマージン

結論

この作品では、V / SiO x / AlO y / p ++ CCLを制御するだけでセレクタとメモリ機能の両方を備えたSiデバイスを調査した。 1μA以下のCCLが適用されると、セレクターアプリケーションで一方向のしきい値スイッチングが観察されます。ポジティブフォーミングはV電極とVO x のMIT現象を酸化します しきい値の切り替えを引き起こす可能性があります。 AlO y レイヤーは10 4 の高い選択性を達成できます オフ電流を下げることによって。一方、5μA以上のCCLを適用すると、SiO x 上に効果的な導電性フィラメントが形成されるため、メモリスイッチングが観察されます。 層。 CCLが低いほど、非線形性が大きくなり、クロスポイント配列のサイズを大きくするのに役立ちます。

略語

- ALD:

-

原子層堆積

- BE:

-

下部電極

- CCL:

-

コンプライアンス電流制限

- CRS:

-

補完的な抵抗スイッチング

- DRAM:

-

ダイナミックランダムアクセスメモリ

- HRS:

-

高抵抗状態

- I–V:

-

電流-電圧

- LRS:

-

低抵抗状態

- MIT:

-

金属-絶縁体転移

- OTS:

-

オボニックスレッショルドスイッチング

- PECVD:

-

プラズマ化学気相成長法

- P-F:

-

プール-フレンケル

- RRAM:

-

抵抗変化型メモリ

- SCLC:

-

空間電荷制限電流

- SCM:

-

ストレージクラスのメモリ

- SPA:

-

半導体パラメータアナライザ

- SSD:

-

ソリッドステートドライブ

- TE:

-

上部電極

- TEM:

-

透過型電子顕微鏡

- V:

-

バナジウム

ナノマテリアル