The D Latch

ゲートSRラッチのイネーブル入力は、SまたはRのステータスに関係なくQ出力と非Q出力をラッチする方法を提供するため、これらの入力の1つを削除して、「不正な」入力のないマルチバイブレータラッチ回路を作成できます。状態。

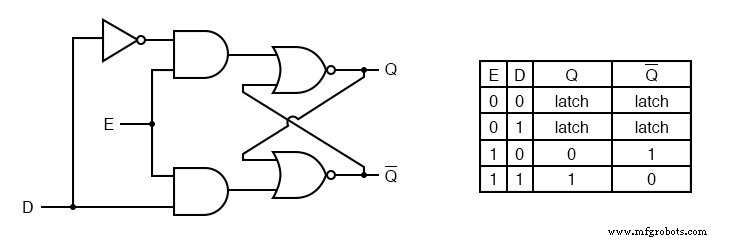

このような回路はDラッチと呼ばれ、その内部ロジックは次のようになります。

R入力が古いS入力の補数(反転)に置き換えられ、S入力の名前がDに変更されていることに注意してください。ゲートSRラッチと同様に、有効にすると、Dラッチは信号入力に応答しません。入力は0です。最後の状態でラッチされたままになります。ただし、イネーブル入力が1の場合、Q出力はD入力の後に続きます。

S-R回路のR入力が廃止されたため、このラッチには「無効」または「不正」な状態はありません。 Qとnot-Qは常に 互いに反対です。

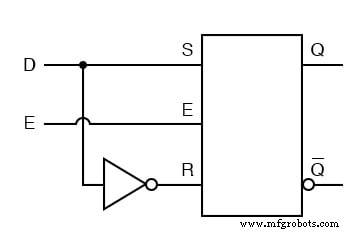

上記の図がまったく混乱している場合は、次の図で概念を単純化する必要があります。

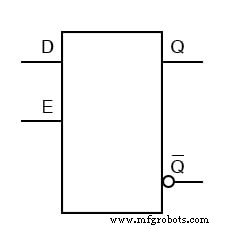

S-Rラッチとゲート付きS-Rラッチの両方と同様に、Dラッチ回路は、標準の記号が付いた独自のパッケージ済み回路として見つけることができます。

Dラッチは、RをSの補数(逆)にするためにインバータが追加されたゲート付きS-Rラッチにすぎません。

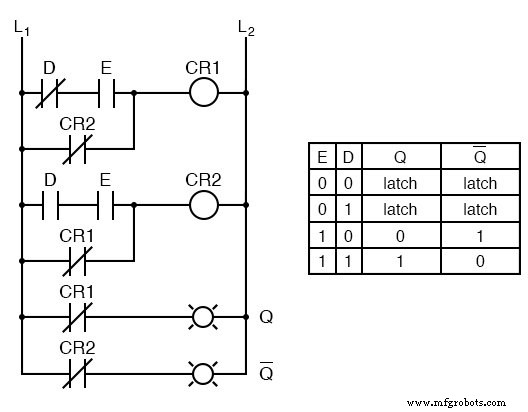

S-Rラッチの基本的なラダー図から変更されたDラッチに相当するラダーロジックを調べてみましょう。

Dラッチの用途は、1ビットのメモリ回路です。イネーブル入力をハイ(1)にし、Dを格納されたビットにしたいものに設定することにより、このラッチ回路に0または1ビットを「書き込む」(格納する)ことができます。イネーブル入力がロー(0)になると、ラッチはD入力のステータスを無視し、保存されたビット値を陽気に保持し、Qで保存された値で出力し、Qではない出力でその逆を行います。

レビュー:

- Dラッチは、「D」入力という1つの入力しかないS-Rラッチのようなものです。 D入力をアクティブにすると回路が設定され、D入力を非アクティブにすると回路がリセットされます。もちろん、これはイネーブル入力(E)もアクティブになっている場合のみです。そうしないと、出力がラッチされ、D入力の状態に応答しなくなります。

- Dラッチは1ビットメモリ回路として使用でき、無効にすると「ハイ」または「ロー」状態を保存し、有効にするとD入力から新しいデータを「読み取る」ことができます。

関連するワークシート:

- ラッチ回路-Dラッチワークシート

産業技術